作者:劉春風(fēng),王惠平,潘利明

隨著社會信息量的增大,人們對多媒體視頻壓縮的要求越來越高,“高壓縮、低比特速率”的高清視頻壓縮已廣泛應(yīng)用于家用電器、醫(yī)療設(shè)備、軍事偵察、衛(wèi)星遙感等領(lǐng)域。ADI公司最新推出的ADV212是一款具有實時壓縮/解壓縮標(biāo)準(zhǔn)(SD)視頻信號和高清晰度(HDTV)視頻信號功能的器件,具有可靠性好、配置靈活、支持視頻格式多樣等優(yōu)點,適用于多種視頻格式的數(shù)據(jù)處理。本文介紹了基于ADV212高清視頻壓縮系統(tǒng)的設(shè)計方案,該系統(tǒng)可支持SMPTE274M(1080i)視頻實時編碼。

1 ADV212的編解碼原理

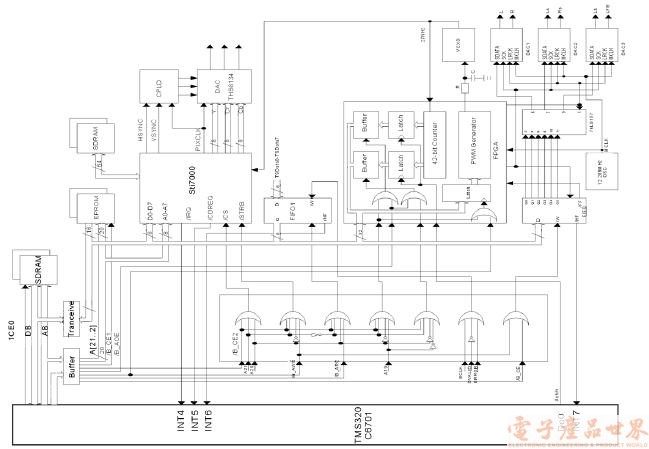

圖l所示為ADV212的功能圖,主要由像素接口、小波變換引擎、熵編/解碼器、嵌入式RISC處理器、存儲器系統(tǒng)和內(nèi)外部DMA等組成。操作的基本流程是視頻或像素數(shù)據(jù)通過ADV212像素接口輸入,有效采樣值則經(jīng)過隔行掃描傳輸?shù)叫〔ㄗ儞Q引擎中(小波變換引擎,可以對碼塊進(jìn)行高達(dá)6級的小波分解)。進(jìn)入小波變換引擎的數(shù)據(jù)被分瓦片或幀,每個瓦片或幀將通過5/3定點運算或9/7浮點運算濾波器分解成許多子帶,并生成相對應(yīng)的小波系數(shù),然后寫入內(nèi)部寄存器中。3個熵編/解碼器用來對小波系數(shù)的編碼塊進(jìn)行背景建模和算術(shù)編碼,并在壓縮過程中計算最佳速率和失真度。熵編碼形成的JPEG2000標(biāo)準(zhǔn)的數(shù)據(jù)碼流被存入代碼FIFO中。代碼FIFO主要緩沖內(nèi)部高速總線和低速主機接口。碼流數(shù)據(jù)可通過共用的讀寫存取協(xié)議(

,ADDR)從主機接口輸出,或者通過DREQ/DACK協(xié)議由外部DMA控制器協(xié)調(diào)下的外部DMA引擎輸出。內(nèi)部DMA引擎完成存儲器之間以及各模塊和存儲器之間的高帶寬、高性能傳輸。RISC處理器具有每一個程序和數(shù)據(jù)存儲器、中斷控制器、標(biāo)準(zhǔn)總線接口及定時器計數(shù)器所對應(yīng)的ROM和RAM。

2 統(tǒng)硬件設(shè)計

本方案作為實現(xiàn)高清視頻數(shù)據(jù)壓縮系統(tǒng),首先從系統(tǒng)實現(xiàn)功能和性價比上考慮,采用FPGA+ADV212來實現(xiàn)。

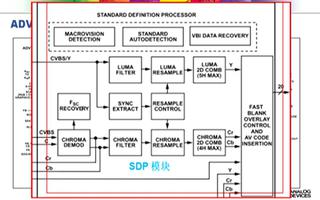

視頻解碼器選取:視頻解碼器選用ADV7402型高清視頻解碼器。它采用10位ADC,12個模擬輸入,支持標(biāo)清(480i,NTSC,PAL,SECAM)、高清(1080i,720p)和圖形RGB輸入(1 280xl 024@60 Hz),可以實現(xiàn)與ADV212無縫連接。

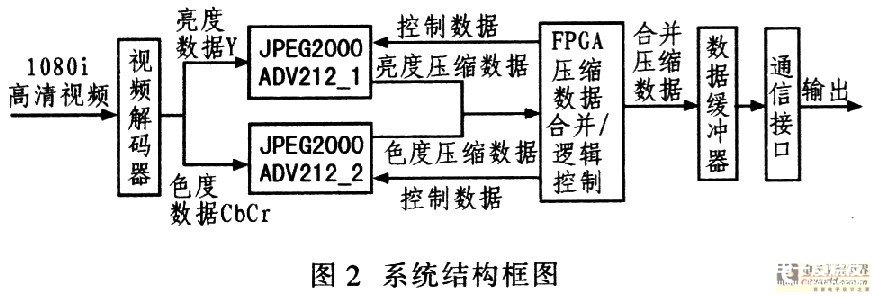

ADV212片數(shù)選取:1個10 bit的高清晰度(HDTV)視頻信號,輸入數(shù)據(jù)傳輸率大約為124 Ms/s,而ADV212像素接口輸入速率限制,在不可逆模式下為65 MS/s,可逆模式下為32 MS/s。這就要求系統(tǒng)至少要由2片ADV212組成,本系統(tǒng)選擇2片ADV212壓縮器件,YCbCr數(shù)據(jù)采取在4:2:2格式,分別完成亮度(Y)和色度(CbCr)的數(shù)據(jù)壓縮處理,輸入數(shù)據(jù)使用是EAV/SAV編碼格式。圖2所示為系統(tǒng)結(jié)構(gòu)框圖,本方案包括視頻采集解碼模塊、視頻圖像JEPG200壓縮模塊、壓縮合并模塊、邏輯控制模塊和通信輸出模塊。

FPGA選取:選用Altera公司的CycloneIII系列EP3C55F484C8器件,其具有328個用戶I/O,55 856個可用邏輯元,312個嵌入式乘法器單元和4個鎖相環(huán),可輕松實現(xiàn)ADV212初始化及壓縮數(shù)據(jù)捕獲和亮度壓縮數(shù)據(jù)與色度壓縮數(shù)據(jù)的合并等功能。

3 ADV212器件初始化流程和參數(shù)配置

3.1 ADV212初始化流程

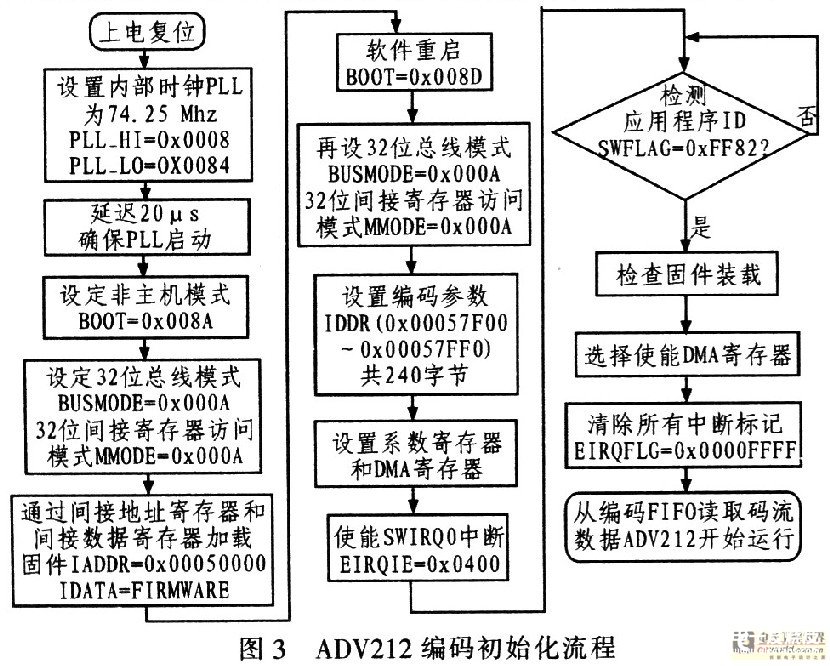

ADV212初始化程序依據(jù)特定的指令命令配置ADV212內(nèi)部直接寄存器和間接寄存器來完成。圖3所示為ADV212編碼初始化流程,初始化程序從PLL寄存器、BOOT寄存器、MMODE寄存器和BUSMODE寄存器等直接寄存器的接入開始,訪問直接寄存器時目標(biāo)系統(tǒng)必須保持輸入管腳ADDR,

,和HDATA(寫)的狀態(tài)。當(dāng)裝載完固件和配置參數(shù)后,軟件重啟,然后再次配置BUSMODE和MMODE寄存器和應(yīng)用特殊寄存器。下一步,要確定正確的固件被應(yīng)用ID裝載。正確的固件裝載能被EIRQFLG寄存器的中斷或投票程序證實。當(dāng)你確定固件連接裝載和EIRQFLG寄存器清零后。編碼開始。

3.2 ADV212參數(shù)配置

時鐘配置:高清視頻1080i要求VCLK為74.25 MHz。根據(jù)ADV212的數(shù)據(jù)表,JCLK必須至少為2VCLK,因此最大的脈沖頻率推薦為0.35J-CLK,這接近50 MHz,這是最大的讀寫脈沖頻率。

總線及DMA配置:HDTV(1080i)應(yīng)用時,2個ADV212必須工作在不可逆最大傳輸率為65 MS/s模式,視頻輸入采取32位VDATA總線(像素接口),壓縮數(shù)據(jù)輸出采取2個ADV212共享32位HDATA總線(主機接口)。初始化ADV212選擇屬性類型5(ATTRTYPE),屬性數(shù)據(jù)讀取采用單一傳輸?shù)腄REQ/DACK DMA模式,碼流讀取采取脈沖傳輸DREQ/DACK DMA模式。

如圖3所示。根據(jù)ADV212的直接寄存器配置,設(shè)定ADV212內(nèi)部時鐘、總線模式、間接寄存器訪問模式等。ADV212_l和ADV212_2初始化流程說明如下:PLL_HIOx008h、PLL_HO,0x0084:設(shè)置VCLK為74.25 MHz;BOOT:0x008A引導(dǎo)模式用來那上否裝載;BUSMODE:0x000A設(shè)置主機控制數(shù)據(jù)寬度和DMA數(shù)據(jù)寬度為32位;MMODE:0x000A設(shè)置間接數(shù)據(jù)存取位數(shù)和間接地址步長大小為32位;IADDR:Ox00050000設(shè)置程序存儲的起始點;IDATA:0x********在程序存儲器裝載程序;BOOT Ox008D軟件重啟;BUSMODE0x000A重新設(shè)置主機控制數(shù)據(jù)寬度和DMA數(shù)據(jù)寬度為32位:MMODE 0x000A重新設(shè)置間接數(shù)據(jù)存取位數(shù)和間接地址步長大小為32位。ADV212的參數(shù)根據(jù)IADDR和IDATA設(shè)置,參數(shù)配置說明如下:IADDR 0x00057F00 ADV212_1和ADV212_2的編碼參數(shù)起始地址;IDATA 0x02010503(ADV212_1)、0x03010503(ADV212_2)02=1080i亮度(03=1080i色度);0l=10位精度;05=5級小波變換;03=Y,C單級;IDATA 0x03000000 03=碼塊大小為128x32;00=不可逆9x7小波;00=跳過無字節(jié)區(qū)域;00=無屬性數(shù)據(jù)輸出;IDATA0x01019500(ADV212_1)、0x01008700(ADV212_2) Ol=目標(biāo)視頻域,幀大小;019500=10:1壓縮率(008700=30:1壓縮率);IDATA 0x00000001 00=LRCP級數(shù)格式;00=EAV.SAV編碼,所有陰極同步;00=Qfaetor是1X;01=編碼格式是.j2c;IDATA0x00000000保存參數(shù)。

上述配置好以后,ADV212_1和ADV212_2的EIRQFLG(地址Ox6h)寫入0x0400去清除軟件中斷(SEIRQ0)并開始程序,當(dāng)DREQ0變?yōu)橛行В珹DV2-12準(zhǔn)備從CODE FIFO傳輸數(shù)據(jù),主機按照ADV212特定時序說明開始數(shù)據(jù)傳輸。

4 FPGA結(jié)構(gòu)功能

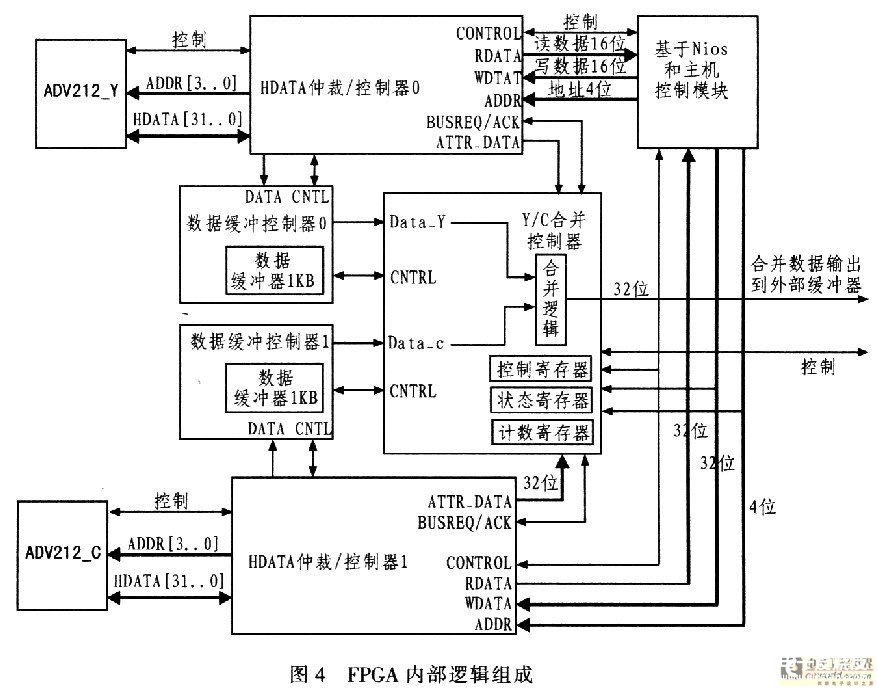

圖4為FPGA內(nèi)部邏輯組成,F(xiàn)PGA主要由以下功能模塊組成:1)主機邏輯,基于Nios的嵌入式主機邏輯模塊,主要實現(xiàn)2片ADV212的讀寫操作,實現(xiàn)對ADV212的初始化和固件下載;2)ADV212仲裁邏輯,實現(xiàn)2片ADV212壓縮數(shù)據(jù)同步,應(yīng)答總線判斷狀態(tài)的應(yīng)答信號功能;3)Y/C合并邏輯,該部分根據(jù)讀出的屬性和代碼信息,實現(xiàn)亮度壓縮數(shù)據(jù)與色度壓縮數(shù)據(jù)的合并功能;4)數(shù)據(jù)緩沖控制模塊,緩沖外部DMA通道讀取速率和亮度/色度合并邏輯模塊間的數(shù)據(jù)流。

在FPGA主控模塊中,要確保ADV212加載了正確的固件,通過4個步驟來實現(xiàn):第1步是向外部中斷使能寄存器中寫入0x0400來屏蔽軟件中斷0位:第2步等待到中斷引腳IRQ被拉低,第3步檢查外部中斷標(biāo)記寄存器的EIRQFlLG[10]位是否被設(shè)置,第4步從軟件標(biāo)記寄存器中讀應(yīng)用標(biāo)識,如果讀到的是0XFF82,則說明固件加載正確,系統(tǒng)可以開始工作。

系統(tǒng)開始工作時,F(xiàn)PGA在仲裁,控制模塊中將從ADV212屬性FIFO中讀取的分區(qū)字節(jié)數(shù)信息進(jìn)行分析判斷,數(shù)據(jù)緩沖控制模塊將ADV212代碼FIFO中讀到的壓縮數(shù)據(jù)進(jìn)行寄存。仲裁/控制模塊分析結(jié)果來控制亮度/色度合并邏輯模塊,碼流從Y數(shù)據(jù)開始從兩個器件相對部分(Y和CbCr)交錯合并,輸出到緩沖器再由通信端口輸出。

5 結(jié)束語

基于FPGA+ADV212結(jié)構(gòu)的高清視頻壓縮系統(tǒng)可實現(xiàn)高清視頻(YCbCr 4:2:2格式)信號的實時處理,本系統(tǒng)具有性價比高、可靠性好、調(diào)整靈活、壓縮信號易恢復(fù)等優(yōu)點。但本系統(tǒng)采用的是不可逆9/7小波變換,視頻處理具有一定的失真,為獲取1080i視頻信號具有更好的特性(如無損壓縮),建議用3片或3片以上的ADV212來處理信號,信號格式可采取YCbCr 4:4:4格式。隨著JPEG2000的廣泛應(yīng)用,專用圖像壓縮器件ADV212必將被越來越多地應(yīng)用到視頻和圖像壓縮方面的領(lǐng)域中。

責(zé)任編輯:gt

-

處理器

+關(guān)注

關(guān)注

68文章

19259瀏覽量

229653 -

FPGA

+關(guān)注

關(guān)注

1629文章

21729瀏覽量

603007 -

解碼器

+關(guān)注

關(guān)注

9文章

1143瀏覽量

40718

發(fā)布評論請先 登錄

相關(guān)推薦

【RTC程序設(shè)計:實時音視頻權(quán)威指南】音視頻的編解碼壓縮技術(shù)

基于TI DSP TMS320C6455和Altera FPGA EP3C40F484C8軟件無線電處理卡

基于TMS320C6455和Altera FPGA EP3C40F484C8的Camera Link 智能圖像處理...

基于TI TMS320DM6467無操作系統(tǒng)Camera Link智能圖像分析平臺

基于TI TMS320DM6467無操作系統(tǒng)Camera Link智能圖像分析平臺

102-基于TI DSP TMS320C6455和Altera FPGA EP3C40F484C8軟件無線電處理卡

103-基于TMS320C6455和EP3C40F484C8的Camera Link 圖像處理平臺

如何在Hive中進(jìn)行數(shù)據(jù)壓縮

視頻編解碼器是什么,編解碼器技術(shù)原理作用

高清視頻解碼器功能介紹

數(shù)字播放器和解碼器

基于EP3C55F484C8和解碼器實現(xiàn)高清視頻數(shù)據(jù)壓縮系統(tǒng)的應(yīng)用方案

基于EP3C55F484C8和解碼器實現(xiàn)高清視頻數(shù)據(jù)壓縮系統(tǒng)的應(yīng)用方案

評論