近期,來自 Kioxia 公司的 Ravi Tangirala 做了一個主題為存儲控制器系統級硬件仿真與原型驗證性能的演講。他是 Kioxia America 公司(前東芝存儲,之后作為獨立公司被拆分)的驗證總監。

存儲控制器作為一種很“常見”的 SoC,是所有 NAND 閃存的接口。盡管近些年出現了 3D NAND,但從存儲控制器的角度而言其實沒帶來什么實質變化。

驗證過程的核心是綜合利用 Cadence Palladium Z1 企業級仿真平臺和 Cadence Protium X1 企業級原型驗證平臺來實現硬件仿真和原型驗證。

上方圖表展示了該團隊的工作過程。圖中紅色線條逐漸上升及下降,反映的是 Palladium 在項目周期中的使用量變化。開始時 Palladium 的使用并不多,因為 RTL 尚未完成。隨著設計的逐步完成,Palladium 使用量也隨之上升。

藍色陰影區代表了固件開發,開始時會使用 Palladium,當設計足夠穩定后就會轉用 Protium。Protium 的優勢是具有比 Palladium 更快的軟件運行速度;不足則是由于 FPGA 布局布線耗時較多,需要相對多些時間來準備版本。

所以在 RTL 穩定前,Protium 并非固件團隊的軟件開發人員的最佳選擇;可一旦 RTL 趨于穩定,軟件人員就會更傾向于用 Protium 做軟件測試。

樣片回片后,軟件開發逐漸結束,Palladium 還會被用來分析樣片測試出的遺留問題。

Palladium 仿真

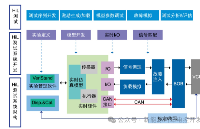

上圖展示了以 Palladium 為核心的完整驗證環境案例,SoC 運行在位于中心的仿真器內,左側為實際主機(訪問閃存)和調試主機(訪問調試端口)。右側連接 DIMMS 上的實際閃存,其容量巨大,同時對仿真速度有要求,因而不適合直接放在仿真器里實現。

Host PC 機通過 SpeedBridge 硬件接口與 Palladium 連接,另一臺調試 PC 機與調試端口相連,而 DIMMS 上的 NAND 會直接與 Palladium 相連。

實際上,這個過程用到了 Palladium 的兩個操作模式:

TBA(Test Bench Acceleration)模式:應用各種虛擬接口,比較適用于 RTL 早期驗證過程。

ICE(In Circuit Emulation)模式:利用上圖中的真實物理接口,能夠達到最快的仿真速度,但不適用于對接口的直接驗證。

Kioxia 總共部署了 6 臺服務器集群用于 Palladium 編譯。單次編譯可以在 3 小時內完成,利用相關選項,12 小時內可以完成 30 次迭代。當然,這種方法在 RTL 穩定后才可真正發揮作用。

如上方圖示,經過時鐘優化,核心功能時鐘可達到 373% 的性能提升。需要注意的是,這是仿真性能提升,而非指 SoC 自身時鐘頻率。

以 Palladium 為核心搭建起來的硬件仿真環境,可以實現端到端測試(在 PC 主機上運行的應用軟件可以訪問到實際的 NAND 存儲器)。

有了這樣的仿真平臺,我們可以運行測量 I/O 吞吐率的硬盤應用,以及測試硬盤在最差情況的運行等等。因為測試時間需要足夠長才能生成精確的度量數據,所以仿真平臺的整體性能就變得非常關鍵。上述以 Palladium 為核心的仿真平臺可以將 I/O 訪問速率提升 9 倍,并將啟動時間和 NAND 擦除時間縮短 5.5 倍。

Protium 原型驗證

固件開發可以實現從 Palladium 至 Protium 的無縫切換,因為兩者在前端使用同樣的編譯器。上圖可以看出,Protium 和 Palladium 兩個平臺幾乎完全一樣,都使用同樣的 Speedbridge 和 I/O 卡。

動態配對組合

利用 Palladium 和 Protium 聯合使用流程,RTL 可以按照上圖所示同時編譯給兩大平臺,使得客戶可以用 Palladium 實現高性能的硬件仿真,同時用 Protium 實現更高性能的固件開發。由于 Protium 的編譯和布局布線需要 15-24 小時,在設計足夠穩定后,軟件開發者利用雙平臺的流程會更加高效。比如完成操作系統啟動,保證軟件開發人員能夠調試各自的代碼。

小結

Palladium 應用在項目初期,在性能加快 373% 同時,充分利用其強大的調試能力。

Protium 主要針對固件開發,仿真性能可以達到Palladium 的 4.6 倍。

可以利用 QTDB 實現 Palladium 與 Protium 的快速無縫遷移。

原文標題:【成功案例】如何利用 Palladium 和 Protium 進行早期固件開發

文章出處:【微信公眾號:Cadence楷登】歡迎添加關注!文章轉載請注明出處。

責任編輯:haq

-

控制器

+關注

關注

112文章

16332瀏覽量

177812 -

soc

+關注

關注

38文章

4161瀏覽量

218167

原文標題:【成功案例】如何利用 Palladium 和 Protium 進行早期固件開發

文章出處:【微信號:gh_fca7f1c2678a,微信公眾號:Cadence楷登】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

芯華章推出新一代高性能FPGA原型驗證系統

解決方案丨EasyGo新能源系統實時仿真應用

EasyGo實時仿真丨PCS儲能變流器控制仿真應用

組合邏輯控制器的設計步驟是什么

開放式高實時高性能PLC控制器解決方案-基于米爾電子STM32MP135

湯谷智能發布全棧RISC-V硬件仿真加速系統方案

存儲控制器系統級硬件仿真與原型驗證性能

存儲控制器系統級硬件仿真與原型驗證性能

評論