我們還是先從脈沖寬度調制的基礎說起。脈沖寬度調制,英文縮寫為:PWM(Pulse Width Modulation),是通過數字信號實現對模擬電路控制的一種非常有效的技術,常被廣泛應用于測量、通信、功率控制與變換等眾多領域。

那么PWM是如何工作的?

我們知道,數字電路只能產生高電平(1)或低電平(0),在小腳丫上也就意味著3.3V和0V。那么如果我們的應用恰好在這之間怎么辦?比如,將3.3V直接連到LED上會導致LED燈很亮。如何將LED燈調暗呢?當然,最簡單的辦法就是直接串聯一個限流電阻但這樣一來,限流電阻就需要不斷產生功耗,而這個功耗實際上是完全浪費掉的。

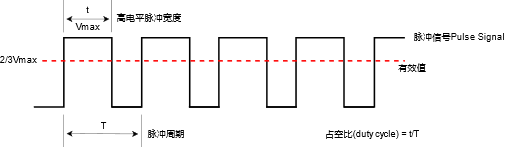

無非就是調節LED的亮度而已,難道就沒有其他更好的辦法了嗎?當然有,用我們今天學習的PWM就可以輕松實現。在進一步探討點亮LED之前,我們先通過圖1了解一些基本的參數:

圖1

圖1中,脈沖信號的周期為T,高電平寬度為t。如果我們將t/T定義為占空比,占空比就是2/3,因為高電平的寬度占了整個周期的2/3。在圖1中我們還可以看到一條紅色虛線,畫在了脈沖高度2/3的位置。這條虛線實際上就對應著最終的有效值。那么如何在FPGA上生成PWM信號呢?

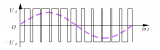

我們還是習慣看圖說話,請看圖2。假如我們有一個鋸齒波,然后在鋸齒波上設置一個閾值(黑色水平虛線),凡是大于該閾值時輸出均為高電平,反之則為低電平,這樣我們是不是就得到一個PWM信號呢?如果我們想調整它的占空比,那么調節閾值的高低就可以了。在本例中,閾值線越低占空比越高。

圖2

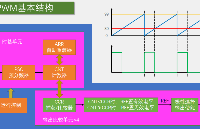

如果把上面的描述再抽象化一下,就可以畫出圖3的模塊框圖。鋸齒波實際上就可以用計數器生成,閾值就是一個數值而已,比較器是用來生成最后輸出高低電平用的。

圖3

有了設計思路之后,我們來看一下最終代碼。

module pwm (PWM_out, clk, reset); input clk, reset; output reg PWM_out; wire [7:0] counter_out; //計數器的8位寬儲存,可以最多數128次時鐘的嘀嗒 parameter PWM_ontime = 32; //閾值設在32,對應25%的占空比 always @ (posedge clk) begin //比較器 if (PWM_ontime 》 counter_out) PWM_out 《= 0; else PWM_out 《= 1; end counter counter_inst( //調用計數器 .clk (clk), .counter_out (counter_out), .reset(reset) );endmodule

module counter(counter_out,clk,reset); //計數器模塊代碼 output [7:0] counter_out; input clk, reset; reg [7:0] counter_out; always @(posedge clk) if (reset) //如果沒有按reset,則計數器清零 counter_out 《= 8‘b0; else //如果按下reset,則計數器開始計數 counter_out 《= counter_out + 1;endmodule

在代碼中,我們設置的計數器位寬是8位,也就是每128次后自動重新計數。所以,該計數器的最大頻率也就是12MHz/128=93.75KHz。圖3中可以看出,PWM信號的頻率和計數器的頻率相同,因此也是93.78KHz。

試想一下,LED現在正以超過每秒9萬次的速度閃爍,肉眼是完全分辨不出來的。那么閃爍過程中,亮/滅的比值越大,LED的視覺發光效果就越強,反之則越弱。我們最后將上述程序導入小腳丫中,并通過調節閾值來觀察小腳丫上的LED發光強度的變化。

編輯:lyn

-

通信

+關注

關注

18文章

6209瀏覽量

137905 -

數字電路

+關注

關注

193文章

1641瀏覽量

81977 -

測量

+關注

關注

10文章

5277瀏覽量

113635 -

脈沖寬度調制

+關注

關注

7文章

81瀏覽量

13996

原文標題:基于FPGA的數字電路實驗8:PWM脈寬調制

文章出處:【微信號:xiaojiaoyafpga,微信公眾號:電子森林】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

PWM逆變器的不同調制方法對比

STM32H7開啟單脈沖模式 PWM波脈沖寬度不受CCR控制怎么解決?

開關電源三種控制模式:PWM/PFM/PSM

探索PWM技術:數字世界的模擬魔法

【瑞薩RA2L1入門學習】+PWM呼吸燈

請問DLP4500觸發器脈沖寬度可以調整嗎?

SM7075-12 AC/DC PWM 功率開關芯片 輸出電壓12V

評論