這款DSP + ZYNQ核心板,是如何實現核間通訊呢?

核心板簡介

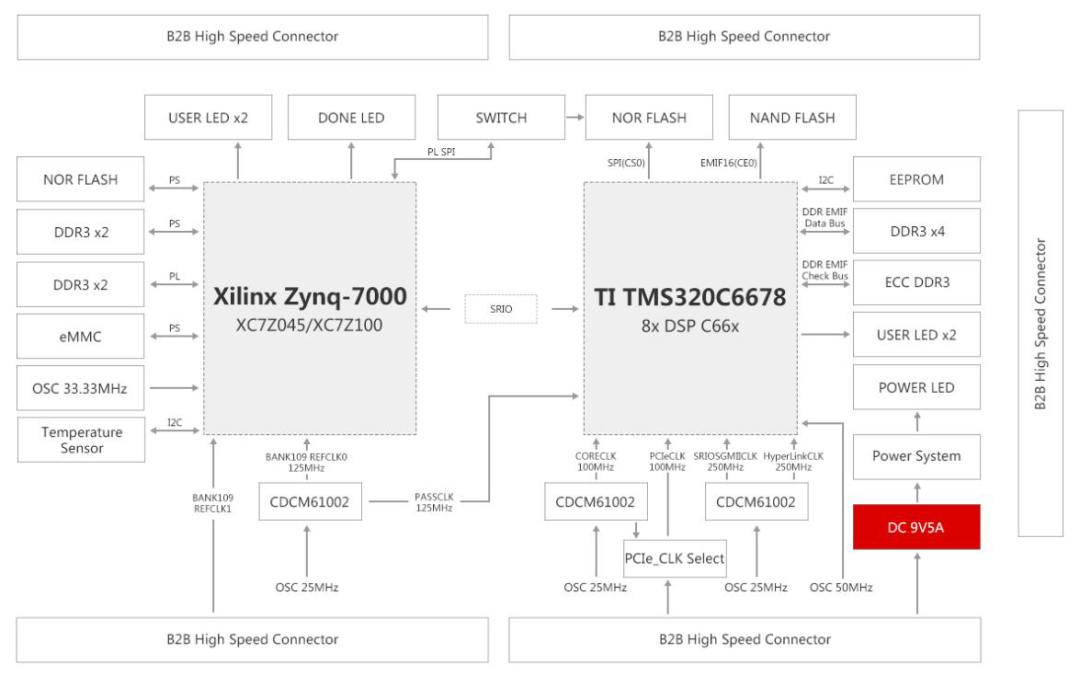

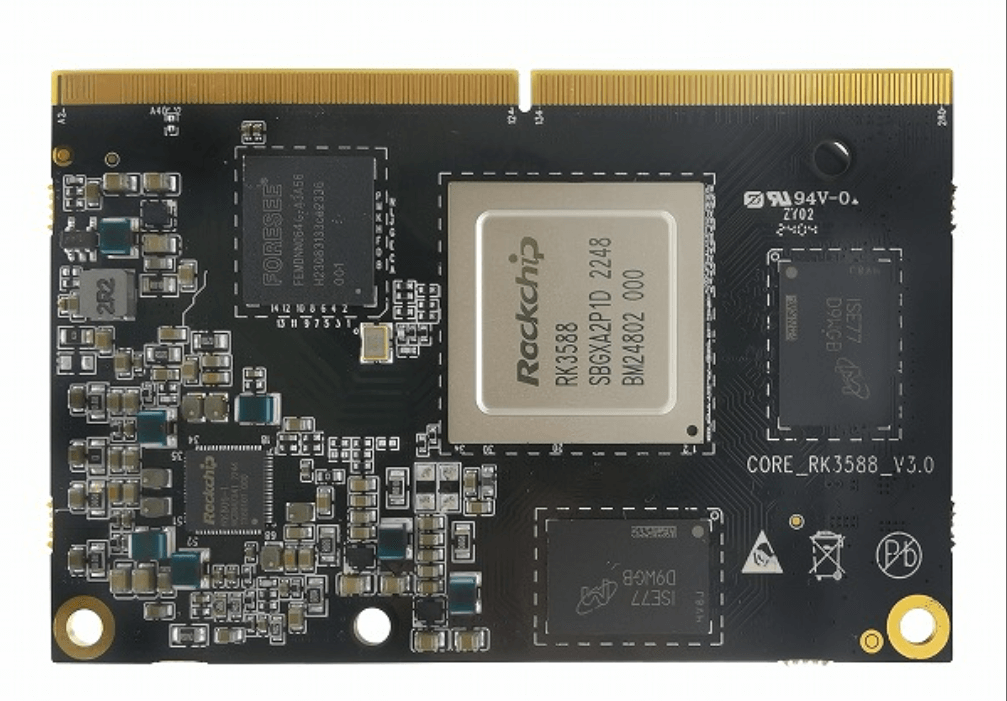

SOM-TL6678ZH是一款基于TI KeyStone架構C6000系列TMS320C6678八核C66x定點/浮點DSP,以及Xilinx Zynq-7000系列XC7Z045/XC7Z100 SoC處理器設計的高端異構多核工業級核心板。TMS320C6678每核心主頻可高達1.25GHz,XC7Z045/XC7Z100集成PS端雙核ARM Cortex-A9 + PL端Kintex-7架構28nm可編程邏輯資源。核心板內部DSP與ZYNQ通過SRIO通信總線連接,并通過工業級高速B2B連接器引出千兆網口、PCIe、HyperLink、EMIF16、USB、CAN、UART、GTX等通信接口。

本文主要介紹DSP + ZYNQ基于SRIO的通信案例。

1

SRIO簡介

SRIO(Serial Rapid I/O)是高速串行RapidIO通信接口,常用于DSP與DSP、DSP與FPGA之間的數據高速傳輸。SRIO引腳占用數量少,支持多點傳輸,速率可配置為1.25Gbps、2.5Gbps、3.125Gbps和5Gbps。

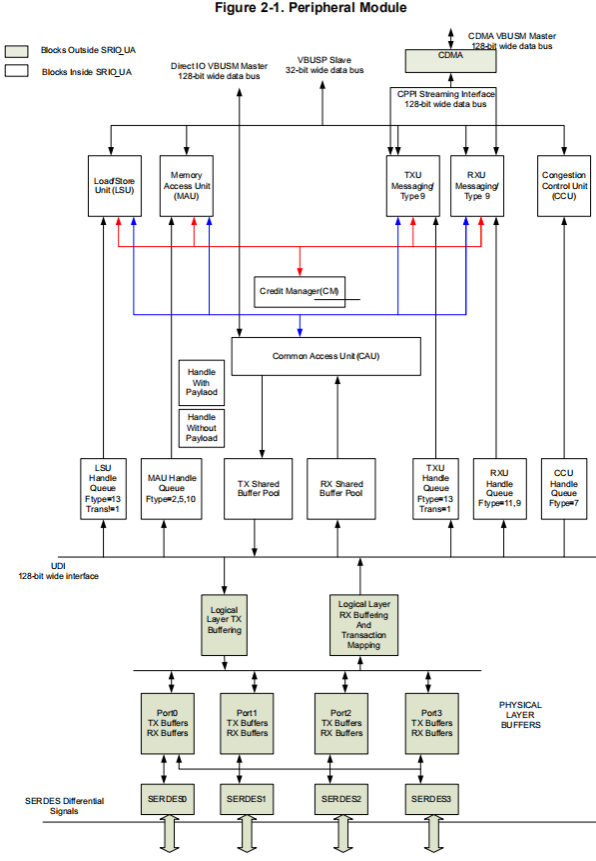

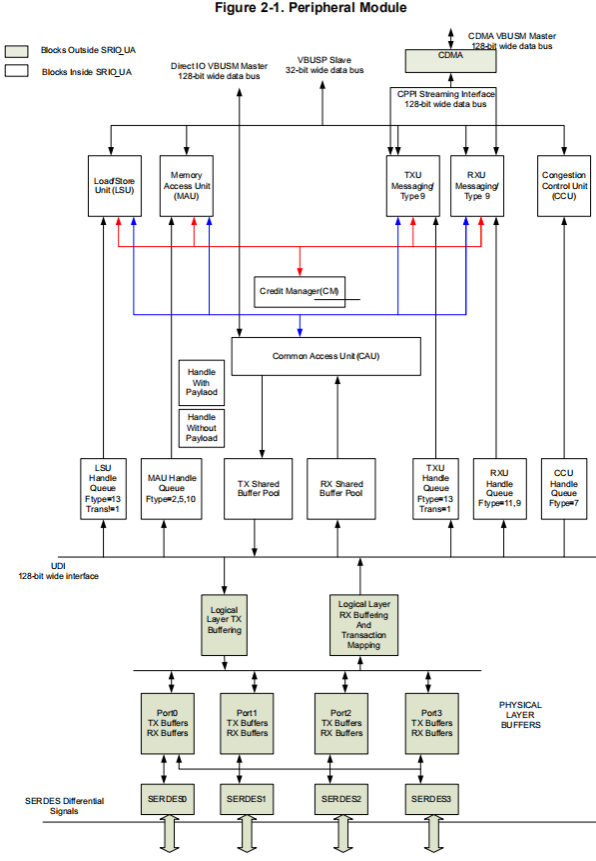

SRIO包含三層結構協議,即物理層、傳輸層、邏輯層。

(1) 邏輯層:定義包的類型、大小、物理地址、傳輸協議等必要配置信息。

(2) 傳輸層:定義包交換、路由和尋址規則,以確保信息在系統內正確傳輸。

(3) 物理層:包含設備級接口信息,如電氣特性、錯誤管理數據和基本流量控制數據等信息。

RapidIO體系結構如下:

2

SRIO通信案例

1.1 案例功能

評估板DSP端和ZYNQ PL端進行SRIO通信測試,并統計讀寫速率。評估板DSP端作為Initiator,評估板ZYNQ PL端作為Target。SRIO默認配置為x4模式,每個通道速率5Gbps,并分別使用NWRITE + NREAD和SWRITE + NREAD模式進行測試。ZYNQ PL端使用一個36Kbit的BRAM作為設備存儲空間,將DSP端發送的過來數據儲存至BRAM。

1.2 案例測試

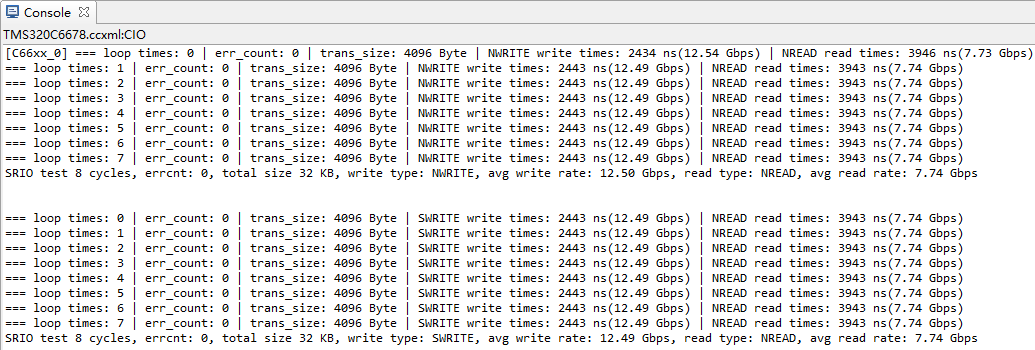

先加載運行ZYNQ PL端程序,再運行DSP端程序,CCS Console窗口將打印測試結果。

NWRITE + NREAD模式:NWRITE = 12.50Gbps NREAD = 7.74Gbps

SWRITE + NREAD模式:SWRITE = 12.49Gbps NREAD = 7.74Gbps

備注:由于寫測試僅統計發送數據至SRIO FIFO的時間,讀測試統計發送讀請求并等待Target發送數據完成的時間,因此寫速率將比讀速率高。

2.3關鍵代碼

2.3.1 DSP工程

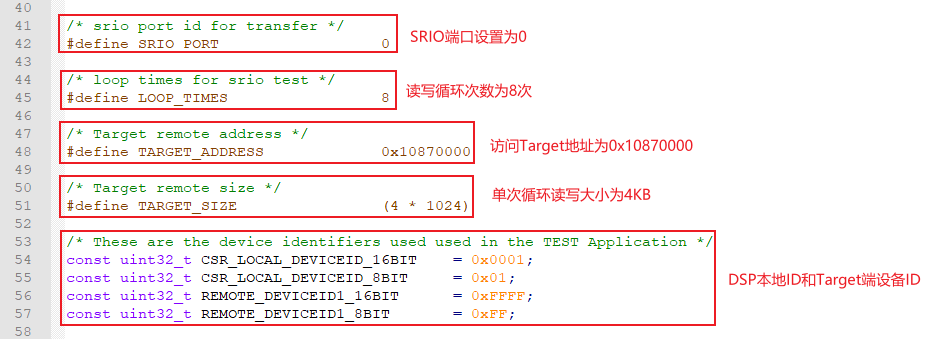

(1) 程序配置說明。

(2) 使能SRIO PSC,初始化SRIO子系統,SRIO通信測試。

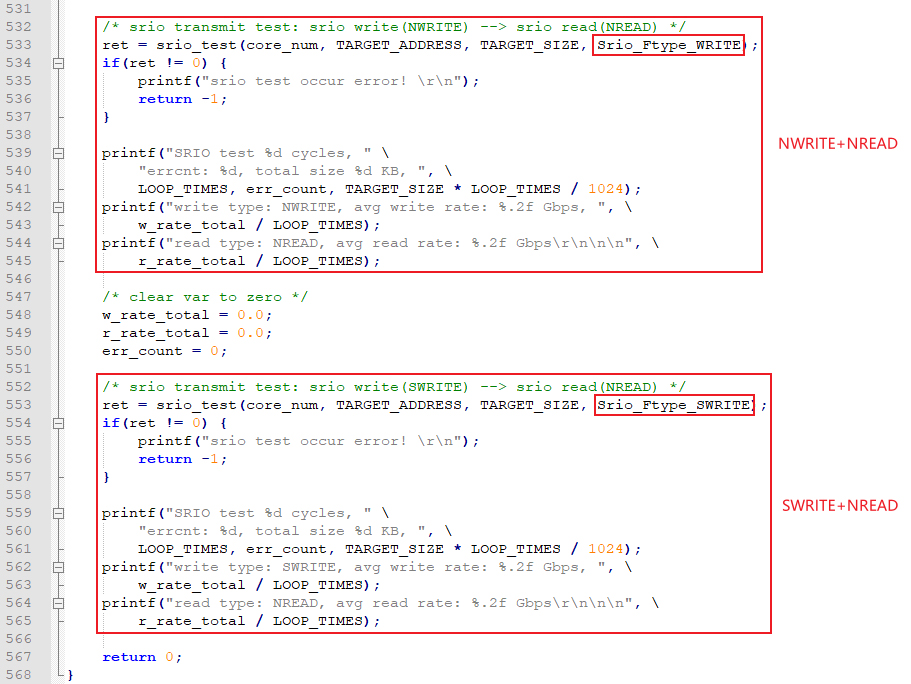

(3) 以NWRITE + NREAD和SWRITE + NREAD模式進行SRIO通信測試,單次讀寫大小為transfer_size,單位為Byte。w_format_type寫格式類型在main函數中調用srio_test()傳入。

(4) SRIO寫測試流程。

(5) SRIO讀測試流程。

2.3.2 ZYNQ工程

(1) 端口定義。

(2) 使用STARTUPE2原語提供的EOS作為系統復位信號,CFGMCLK(65MHz)作為系統時鐘。

(3) 例化Serial RapidIO Gen2 IP核。

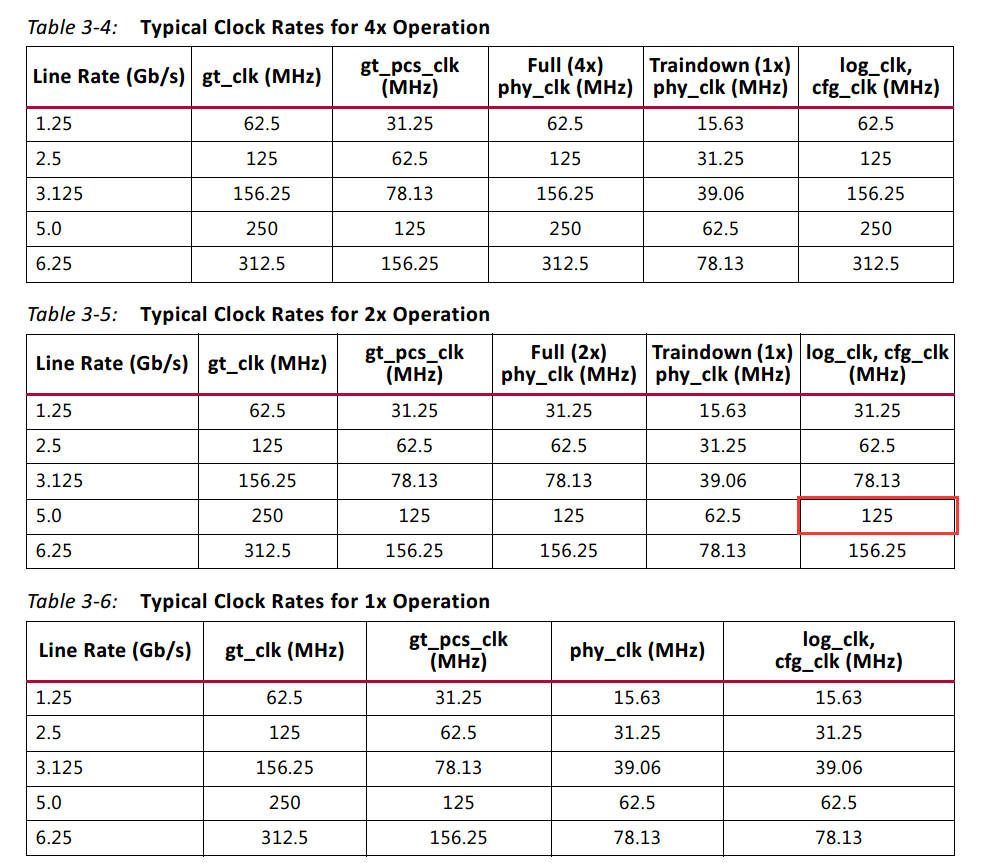

其中Serial RapidIO Gen2 IP核輸出的log_clk為125MHz。

(4)調用srio_response_gen模塊,其接口與Serial RapidIO Gen2 IP核連接。

SRIO詳細開發說明請參考產品光盤“6-開發參考資料TI官方參考文檔”目錄下的《Serial Rapid IO (SRIO) User Guide.pdf》文檔。

原文標題:想了解DSP+ZYNQ核間通訊?看完這篇就夠了

文章出處:【微信公眾號:FPGA開源工作室】歡迎添加關注!文章轉載請注明出處。

責任編輯:haq

-

連接器

+關注

關注

98文章

14547瀏覽量

136655 -

核心板

+關注

關注

5文章

1016瀏覽量

29784

原文標題:想了解DSP+ZYNQ核間通訊?看完這篇就夠了

文章出處:【微信號:leezym0317,微信公眾號:FPGA開源工作室】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

MTK6761(MT6761)安卓核心板_聯發科MTK核心板模塊方案

嵌入式核心板的分類及PCB設計

驍龍665安卓核心板_SM6125核心板參數_安卓核心板高通方案定制

FET113i-S核心板已支持RISC-V,打造國產化降本的更優解

MT6877安卓核心板_MTK6877核心板規格參數_MTK平臺模塊定制

正點原子ZYNQ7015開發板!ZYNQ 7000系列、雙核ARM、PCIe2.0、SFPX2,性能強悍,資料豐富!

MT8390安卓核心板_MT8390 (Genio 700)核心板詳細參數

[XILINX] 正點原子ZYNQ7035/7045/7100開發板發布、ZYNQ 7000系列、雙核ARM、PCIe2.0、SFPX2!

盛顯科技RK3588核心板:高性能工業計算的新紀元

MTK8766核心板_MT8766安卓核心板聯發科4G智能模塊方案

全志T527國產核心板及米爾配套開發板批量上市!

米爾這款首發的國產核心板批量上市了!全志T527

DSP+ZYNQ核心板是如何實現核間通訊的?

DSP+ZYNQ核心板是如何實現核間通訊的?

評論