引言:傳輸介質(zhì)的選擇,無論是PCB材料還是電纜類型,都會對系統(tǒng)性能產(chǎn)生很大的影響。盡管任何傳輸介質(zhì)在GHz頻率都是有損的,但本章提供了一些管理信號衰減的指南,以便為給定的應(yīng)用獲得最佳性能。

1.信號實(shí)際頻率

信號邊緣包含稱為諧波的頻率分量。每個(gè)諧波都是信號頻率的倍數(shù),其有效最高頻率可以由式1表示:

(式1)

其中,f單位為GHz,為信號上升時(shí)間或下降時(shí)間中的較小者。通常高速或者低速信號的劃分,可以參照式1。即高速信號不一定都是頻率很高的信號,主要和信號中包含的有效最高頻率有關(guān)。

由于PCB中的介電損耗與頻率有關(guān),因此必須確定所關(guān)注的帶寬以找到PCB的總損耗。頻率必須從工作頻率開始,并延伸至等式1中的頻率。例如,具有10ps上升時(shí)間的10Gb/s信號具有10Ghz到35Ghz的帶寬。

2.介質(zhì)損耗

電介質(zhì)中損耗的信號能量是材料特性的函數(shù)。用來描述材料的一些參數(shù)包括相對介電常數(shù)(也稱為介電常數(shù))和損耗角正切。集膚效應(yīng)也是在GHz范圍內(nèi)能量損失的一個(gè)因素。

圖1、不同材料的損耗曲線

2.1 相對介電常數(shù)

相對介電常數(shù)是測量介質(zhì)對導(dǎo)體電容的影響。相對介電常數(shù)越高,信號在PCB走線傳播的速度越慢,給定走線幾何結(jié)構(gòu)的阻抗越低。低常數(shù)幾乎總是首選。

相對介電常數(shù)

盡管在所有材料中,相對介電常數(shù)隨頻率變化,但FR4的εr隨頻率變化很大。由于εr直接影響阻抗,F(xiàn)R4走線阻抗值隨頻率的增加而擴(kuò)展。雖然在1.125 Gb/s的速度下,這個(gè)擴(kuò)展可能不重要,但在10Gb/s的速度下,它可能是一個(gè)問題。

損耗角正切

損耗角正切是一種測量電介質(zhì)沿傳輸線傳播時(shí),有多少電磁能量損失到電介質(zhì)上的方法。較低的損耗角正切允許更多的能量以較少的信號衰減到達(dá)目的地。

隨著頻率的增加,能量損失的幅度也隨之增加,導(dǎo)致信號邊緣的最高頻率諧波受到最大的衰減。這表現(xiàn)為上升和下降時(shí)間的下降。

集膚效應(yīng)和電阻損耗

集膚效應(yīng)是電流優(yōu)先在導(dǎo)體外表面附近流動的趨勢。這主要是由于高頻信號中的磁場推動電流沿垂直方向流向?qū)w的周長。 隨著表面附近電流密度的增加,電流流過的有效橫截面積減小。由于導(dǎo)體的有效橫截面積現(xiàn)在變小,所以電阻增大。因?yàn)檫@種趨膚效應(yīng)隨著頻率的增加而更加明顯,電阻損耗隨著信號速率的增加而增加。 電阻損耗對信號的影響與損耗角正切相似。由于高次諧波的振幅減小,上升和下降時(shí)間增加,最高頻率的諧波受到的影響最大。在10Gb/s信號的情況下,使用FR4時(shí),即使基頻也會有一定程度的衰減。 例如,在1 MHz下8 mil寬的走線的電阻約為0.06Ω/英寸,而在10Gb/s下相同的走線的電阻略高于1Ω/英寸。給定一個(gè)10英寸的走線和1.6V的電壓擺幅,160mV的電壓降是由基頻的電阻損耗引起的,不包括諧波和介電損耗中的損耗。

圖2、介電常數(shù)、板材及應(yīng)用頻率范圍選擇基底材料

材料選擇的目標(biāo)是優(yōu)化特定應(yīng)用的性能和成本。

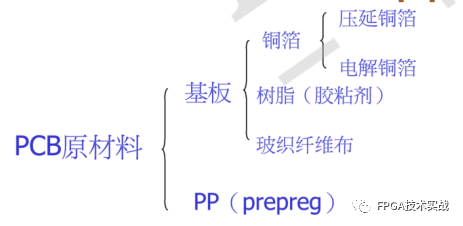

圖3、PCB原材料 FR4是最常見的PCB基板材料,通過仔細(xì)的系統(tǒng)設(shè)計(jì)提供了良好的性能。對于較長的走線長度或高信號速率,必須使用具有較低介電損耗的更昂貴的襯底材料。

基板,例如,Nelco,具有較低的介電損耗,并且在GHz范圍內(nèi)表現(xiàn)出顯著較少的衰減,因此增加了PCB的最大帶寬。在3.125Gb/s時(shí),與FR4相比,Nelco的優(yōu)點(diǎn)是增加了電壓擺幅裕度和更長的Z走線長度。在10Gb/s的速度下,除非高速走線保持很短,否則像Nelco這樣的低損耗電介質(zhì)是必要的。

基板材料的選擇取決于高速走線的總長度和信號速率。 假設(shè)分析可以在HSPICE模擬中進(jìn)行,以評估各種基底材料。通過改變PCB基板材料的介電常數(shù)、損耗角正切等參數(shù)。對眼圖質(zhì)量的影響可以仿真,以證明使用更高成本的材料是合理的。還可以探討銅板厚度等其他參數(shù)的影響。

3.走線

3.1 走線幾何

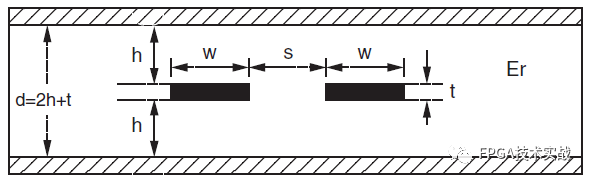

對于任何走線,其特性阻抗取決于其層疊幾何結(jié)構(gòu)以及走線幾何結(jié)構(gòu)。在差分走線的情況下,緊耦合對之間的電感和電容耦合也決定了走線的特性阻抗。

走線的阻抗由其與附近導(dǎo)體的電感和電容耦合決定。例如,這些導(dǎo)體可以是平面、過孔、焊盤、連接器和其他走線,包括差分對中的其他緊密耦合走線。基板特性、導(dǎo)體特性、磁鏈面積和到附近導(dǎo)體的距離決定了耦合量,從而決定了對最終阻抗的貢獻(xiàn)。 二維場解算器是解決這些復(fù)雜相互作用的必要工具,有助于計(jì)算走線的最終阻抗。它們也是驗(yàn)證現(xiàn)有走線幾何圖形的有用工具。 更寬的走線為電流流動創(chuàng)造了更大的橫截面積,并減少了高速接口中的電阻損耗。使用空間限制允許的最寬走線。因?yàn)樽呔€寬度公差是用絕對值表示的,所以較寬的走線也會使制造走線的百分比變化最小化,從而使沿傳輸線長度的阻抗控制更加嚴(yán)格。 有時(shí),帶狀線優(yōu)于微帶線,因?yàn)樽呔€兩側(cè)的基準(zhǔn)面提供輻射屏蔽。微帶線只在一側(cè)(通過基準(zhǔn)面)被屏蔽,因?yàn)樗鼈冞\(yùn)行在最頂層或最底層,而另一側(cè)暴露在環(huán)境中。

為獲得最佳結(jié)果,建議使用2D或3D場解算器進(jìn)行驗(yàn)證。

3.2 高速收發(fā)器的走線特性阻抗設(shè)計(jì)

因?yàn)槭瞻l(fā)器使用差分信號,所以最有用的走線配置是差分邊緣耦合帶狀線和差分微帶。雖然有些背板使用差分寬帶耦合帶線配置,但不建議將其用于10Gb/s操作,因?yàn)镻和N過孔是不對稱的,并引入共模非理想性。

除少數(shù)例外,50Ω特性阻抗(Z0)用于通道中的傳輸線。通常,當(dāng)寬度/間距(W/S)比大于0.4(8 mil寬的記錄道,間隔20 mil)時(shí),P和N信號之間的耦合會影響走線阻抗。在這種情況下,差分走線必須設(shè)計(jì)為奇數(shù)模阻抗(Z0O)為50Ω,導(dǎo)致差分阻抗(ZDIFF)為100Ω,因?yàn)閆DIFF=2 x Z0O。

同樣的W/S比也必須小于0.8,否則,對于50Ω的Z0O,走線之間的強(qiáng)耦合需要更窄、更損耗的走線。為了澄清,當(dāng)Z0O為50Ω時(shí),需要60Ω或以下的偶數(shù)模阻抗(Z0E)。 圖4至圖7顯示了差分結(jié)構(gòu)的橫截面示例。

圖4、差分邊緣耦合中心帶狀線

圖5、差分邊耦合偏移帶狀線

圖6、中心寬邊耦合帶狀線

圖7、差分微帶

一個(gè)好的印刷電路板制造商了解控制阻抗,并允許對線寬進(jìn)行微調(diào),以產(chǎn)生50Ω的Z0O。PCB制造商還提供特定PCB布局所需的參數(shù)。一些參數(shù)可以根據(jù)示例中概述的準(zhǔn)則進(jìn)行計(jì)算或仿真。盡管Z0O上±10%的公差是典型的,并且可以提供足夠的性能,但是更緊公差的額外成本會導(dǎo)致更好的信道性能。

3.3走線布線

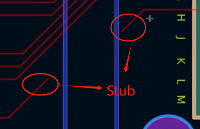

高速串行差分走線應(yīng)以最高優(yōu)先級布線,以確保對這些關(guān)鍵走線提供最佳路徑。這減少了對彎曲和通孔的需要,并將阻抗轉(zhuǎn)換的可能性降至最低。走線必須保持筆直、簡短,并盡可能減少層疊變化。過孔的影響在后續(xù)的微分過孔中討論。 高速走線的布線必須避免靠近其他走線或其他潛在噪聲源。相鄰信號平面上的走線應(yīng)垂直運(yùn)行,以盡量減少串?dāng)_。 盡可能使用帶狀線,以及最上面和最下面的帶狀線層,以盡量減少通孔短線。規(guī)劃層疊時(shí),這些層必須盡可能靠近頂層和底層可能。設(shè)計(jì)限制可能需要用于BGA出口路徑或從通孔到連接器傳輸或SMT焊盤的微帶線。在這種情況下,微帶線必須盡可能短。

建議使用斜接45度彎頭(與90度彎頭相反)。在90度彎曲處,走線的有效寬度發(fā)生變化,由于附加導(dǎo)體區(qū)域與基準(zhǔn)面的電容耦合,導(dǎo)致阻抗不連續(xù)。差分對的兩條走線必須長度匹配以消除偏差。歪斜在共模中產(chǎn)生不匹配,并因此降低差分電壓擺幅。

3.4 平面分割

地平面應(yīng)作為信號的參考平面,而不是噪聲較大的電源平面。每個(gè)參考平面在走線長度上應(yīng)該是連續(xù)的,因?yàn)樵谄矫娣指钌喜季€會產(chǎn)生阻抗不連續(xù)性。在這種情況下,走線的阻抗會發(fā)生變化,因?yàn)槠渑c基準(zhǔn)面的耦合在平面分割處發(fā)生突變。

圖8、PCB走線跨分割平面

3.5 回流

在平面分割上布線也會產(chǎn)生回流問題。由于介電損耗中提到的集膚效應(yīng),高速信號在走線表面附近傳輸。同時(shí),回流也在緊耦合參考面的表面附近流動。 由于緊密耦合,回流有向原始信號傳輸走線靠近的趨勢。在平面分割時(shí),回流不能再沿著與走線平行的同一路徑,而是必須找到另一條路徑。

平面分割會導(dǎo)致次優(yōu)的電流返回路徑,并增加電流回路面積,從而增加平面分割出走線的電感,從而改變走線的阻抗。

3.6 有損傳輸線

由于各種電路仿真器使用不同的建模實(shí)現(xiàn)(頻域和時(shí)域技術(shù)),因此檢查模型是否準(zhǔn)確反映實(shí)際損耗非常重要。一種方法是將模型與已知的已發(fā)布配置進(jìn)行比較。

4.電纜

由于沿電纜長度方向?qū)w和電介質(zhì)的物理尺寸恒定,電纜是受控阻抗傳輸線。最高質(zhì)量的電纜在這些尺寸上幾乎沒有變化,并且在高頻下具有低損耗的寬帶寬。

4.1 連接器

連接到電纜的連接器應(yīng)具有低寄生電感、低寄生電容和低串?dāng)_,以實(shí)現(xiàn)高帶寬操作。

4.2 導(dǎo)線間偏移

選擇電纜時(shí),請查看電纜中導(dǎo)線之間的傾斜規(guī)格。如果導(dǎo)線長度不匹配,則共模中會出現(xiàn)偏移,并直接降低眼圖高度。

原文標(biāo)題:Xilinx 7系列FPGA PCB設(shè)計(jì)指導(dǎo)(四)

文章出處:【微信公眾號:FPGA之家】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

責(zé)任編輯:haq

-

FPGA

+關(guān)注

關(guān)注

1629文章

21729瀏覽量

603009 -

pcb

+關(guān)注

關(guān)注

4319文章

23080瀏覽量

397518 -

Xinlix

+關(guān)注

關(guān)注

0文章

6瀏覽量

7998

原文標(biāo)題:Xilinx 7系列FPGA PCB設(shè)計(jì)指導(dǎo)(四)

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

PCB設(shè)計(jì)中的Stub對信號傳輸的影響

PCB板厚度對信號傳輸的影響

HDMI模塊的PCB設(shè)計(jì)

專業(yè)PCB設(shè)計(jì),高速PCB設(shè)計(jì),PCB設(shè)計(jì)外包, PCB Layout,PCB Design,PCB畫板公司,PCB設(shè)計(jì)公司,迅安通科技公司介紹

以太網(wǎng)的傳輸介質(zhì)和工作模式

PCB設(shè)計(jì)與PCB制板的緊密關(guān)系

Xilinx 7系列FPGA PCB設(shè)計(jì)指導(dǎo)

千萬不要忽略PCB設(shè)計(jì)中線寬線距的重要性

PCB設(shè)計(jì)中的常見問題有哪些?

儲能PCB設(shè)計(jì)與制造思考 探討儲能PCB設(shè)計(jì)與制造中的關(guān)鍵要素

pcb設(shè)計(jì)

多層pcb設(shè)計(jì)如何過孔的原理

DC電源模塊的 PCB設(shè)計(jì)和布局指南

FPGA PCB設(shè)計(jì)如何選擇傳輸介質(zhì)?

FPGA PCB設(shè)計(jì)如何選擇傳輸介質(zhì)?

評論