1 問題的提出

研制測量儀表及電子儀器的過程中,常常遇到按鍵抖動的問題,即雖然只是按下按鍵一次然后放掉,結果在按鍵信號穩定前后,竟出現了一些不該存在的噪聲,這樣就會引起電路的誤動作。在很多應用按鍵的場合,要求具有消抖措施,即對于噪聲信號消抖電路輸出信號為零(消抖電路屏蔽了噪聲信號,表示按鍵沒有動作),只有當按鍵信號K穩定下來甚至經過一定的時間消抖電路才產生輸出信號Y。按鍵信號K消除,消抖電路輸出信號Y隨之消失。

根據某用戶的具體要求設計了具有高抗噪聲特性的、延時時間精密可控的消抖動電路,其按鍵信號K、輸出信號Y之間的關系如圖1所示。

2 電路組成及工作原理

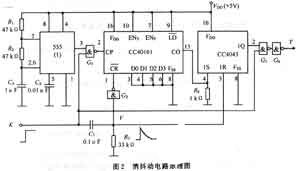

延時時間精密可控的消抖動電路的原理圖如圖2所示。該電路由4塊CMOS集成芯片和若干電阻、電容組成。

其中555定時器組成多諧振蕩器用來給計數器提供時鐘脈沖;1塊CC40161型四位同步二進制計數器用來設定消抖動電路輸出信號Y的延遲脈沖個數。1塊CC4043四R/S鎖存器(只用了1組,其余3組未用)和1塊CC4011四2輸入與非門用來實現信號的鎖存和控制。

當按鍵信號K由低電平變為高電平時,電阻尺3和電容C3組成的微分電路使V點產生一個正脈沖,該正脈沖一路經與非門G2反相后加到計數器CC40161的CR端使其清零;另一路加到鎖存器CC4043的1R端(此時由于計數器沒有進位輸出,CO端為低電平,即lS端為低電平),使鎖存器輸出端1Q為低電子。與此同時,按鍵信號K已加到了與非門G1的輸入端使G1門開門,那么,由555定時器組成的時鐘信號發生器3端輸出的時鐘脈沖通過與非門G1加到計數器的CP端,計數器開始計數。計到15個脈沖,計數器產生進位信號,其CO端輸出高電平,使鎖存器的1Q端變為高電平,該信號加到與非門G3的一個輸入端(與非門G3的另一個輸入端為K,已為高電平),則與非門G4的輸出Y端為高電平;只有當按鍵信號K由高電平為低電平時,Y端才隨之變為低電平。 另一方面,由于按鍵信號K變為低電平,封鎖了G1門,時鐘脈沖不能通過G1門到達計數器的CP端,計數停止。

當出現干擾脈沖時,計數器也計數,但只要干擾沖的寬度小于15個CP脈沖寬度,計數器的進位輸陸號CO端就保持低電平,那么Y信號為低電平,即際脈沖的影響不會出現在Y端。

可以用置數法或復位法將十六進制計數器CC40161接成任意進制計數器,然后通過任意進位信號控制1S端的電位,來調整消抖動電路輸出信號Y的延遲時間。

3 數據計算

555定時器組成的時鐘信號發生器產生的CP脈沖的周期為:

T1=ln(R1+2R2)C1

CP脈沖的占空比為:

q=( R1+ R2)/(R1+2 R2)

按圖中所給參數計算,CP脈沖的周期T1=0.1s,CP脈沖的占空比為:

q=2/3。

消抖動電路輸出信號Y的延遲時間為:

Td=15Tl=151n2(Rl+2R2)C1

按圖中參數計算Td=1.5s

4 電路特點

(1)該電路由CMOS集成芯片組成,功耗低,抗干擾能力強。

(2)從按鍵信號K到消抖電路產生穩定的輸出信號Y的延遲時間Td穩定、可調。

(3)每當按鍵信號K到來(由低電平變為高電平),均自動使計數器清零,不需另外加入復位脈沖。

(4)按鍵信號K消除,計數器自動停止計數,不需另外設置開關。 該電路除用于消除按鍵的抖動外,還可用于需要產生一定延時控制的任何電路中。該電路為利用單片機和CPLD(Complex Programmable Logic Device)實現軟件消抖提供了設計思想。

責任編輯:gt

-

單片機

+關注

關注

6035文章

44553瀏覽量

634765 -

cpld

+關注

關注

32文章

1248瀏覽量

169338 -

振蕩器

+關注

關注

28文章

3832瀏覽量

139049

發布評論請先 登錄

相關推薦

實現一個ns級的延時函數,延時時間不可控的原因?

有哪幾種方法可以實現單片機程序的硬件消抖呢

STM32單片機按鍵消抖和FPGA按鍵消抖的相關資料分享

單片機+CPLD結構體系在電子設計中的應用

基于單片機和CPLD的頻率測量研究

基于單片機+CPLD的多路精確延時控制系統設計

STM單片機中的按鍵消抖和FPGA消抖

單片機復位后為什么要對sp重新賦值_自學單片機第二十二篇:延時消抖|延時|key|單片機|消抖...

利用單片機和CPLD實現延時時間精密可控的消抖動電路設計

利用單片機和CPLD實現延時時間精密可控的消抖動電路設計

評論