作者:漆莊平 , 李國通 , 楊根慶

隨著A/D/A器件與DSP處理器的迅速發(fā)展,使得軟件無線電技術(shù)廣泛地應(yīng)用于陸上移動通信?衛(wèi)星移動通信與全球定位系統(tǒng)等?本文利用軟件無線電的思路,針對中科院創(chuàng)新一號低軌移動小衛(wèi)星多功能地面站設(shè)計的具體要求,研制了一套基于軟件無線電技術(shù)的多信道發(fā)射機設(shè)備?該地面站發(fā)射系統(tǒng)數(shù)字基帶部分采用全軟件化設(shè)計,核心部件是可編程的DSP及FPGA,可同時處理三路信號?該設(shè)備具有以下三個優(yōu)點:多模工作;無線通信系統(tǒng)可升級;發(fā)射配置動態(tài)更改?該設(shè)備可根據(jù)實際需要靈活配置系統(tǒng),適用范圍大大擴展?

1 系統(tǒng)構(gòu)成

從SDR地面站發(fā)射系統(tǒng)如圖1所示?該系統(tǒng)的發(fā)射速率為2.4kbps窄帶?2.4kbps擴頻?19.2kbps窄帶或它們混合的速率?中頻分別為18.45MHz?20MHz?21.85MHz?DAC的采樣頻率為78.336MHz?發(fā)射系統(tǒng)中FPGA實現(xiàn)FIFO?信道編碼?擴頻?內(nèi)插濾波?數(shù)字上變頻?信道合成?DAC預(yù)補償濾波器等功能?這些功能都集成在一片Xilinx VirtexII芯片中?

2 FPGA部分功能模塊

2.1 FIFO模塊

FIFO完成數(shù)據(jù)緩存功能?為了節(jié)省不必要的資源,設(shè)計了一個長度為32?深度為2的FIFO?即當(dāng)一個寄存器32位取完時發(fā)出中斷給DSP,同時讀?寫寄存器指針變換,DSP響應(yīng)中斷向FIFO寫數(shù),此時數(shù)據(jù)還在不斷地讀出?這樣就實現(xiàn)了用最少的資源實現(xiàn)數(shù)據(jù)緩存?

2.2 信道編碼

在實際信道上傳輸數(shù)字信號時,由于信道傳輸特性不理想及加性噪聲的影響,所收到的數(shù)字信號不可避免地會發(fā)生錯誤?采用信道編碼可以將誤碼率降低?本系統(tǒng)主要采用性能較優(yōu)的卷積編碼和差分編碼等?

對于窄帶信號還有擾碼(CCITT V.35)?擾碼能改善位定時恢復(fù)的質(zhì)量,還能使信號頻譜彌散而保持穩(wěn)恒,能改善幀同步和自適應(yīng)時域均衡等子系統(tǒng)的性能?

對于擴頻信號還有擴頻編碼?在直擴系統(tǒng)中,用偽隨機序列將傳輸信息擴展,在接收時又用它將信號壓縮,并使干擾信號功率擴散,提高了系統(tǒng)的抗干擾能力?

編碼過程在DSP的控制下進行,數(shù)據(jù)從DSP送出,并標(biāo)識信道特征,F(xiàn)PGA識別后進入相應(yīng)的編碼通道,這樣三路信道可以分時進行編碼處理?由于硬件速度快的特點,可視為同時處理?

2.3 信道合成

信道合成模塊由內(nèi)插濾波器?數(shù)字上變頻?信道復(fù)接三部分組成?

2.3.1 內(nèi)插濾波器

各信道濾波器性能指標(biāo)如表1所示?

為了以最少的濾波器階數(shù)得到較低的符號間干擾和高阻帶衰減,成形濾波器采用一個根升余弦濾波器,滾降系數(shù)0.4?其頻域表達(dá)式為:

式中α為滾降因子,取0.4?

成形濾波器設(shè)計采用頻率采樣技術(shù),這樣可以得到階數(shù)較低?性能較好的濾波器?成形濾波器一般采用4倍或8倍的內(nèi)插系數(shù)?先用MATLAB把濾波器階數(shù)和系數(shù)確定下來,這樣可以用移位加運算代替乘法以節(jié)省大量硬件資源?在FPGA實現(xiàn)時,采用DA(Distribute Algorithm)技術(shù)?DA技術(shù)提出了二十多年,廣泛應(yīng)用于線性時不變信號處理,已被證明不適用于可編程DSP的固定指令系統(tǒng)結(jié)構(gòu),但是用FPGA實現(xiàn)卻是個好的選擇--DA電路中沒有直接的乘法器,乘法可由查找表得到?

CIC濾波器是一種靈活的無乘法濾波器,適合于硬件實現(xiàn),并可處理任意大的數(shù)據(jù)率變換?由此,第二級內(nèi)插濾波采用CIC濾波器是最佳選擇?

在不降低性能的前提下,從節(jié)省資源的角度考慮,各信道內(nèi)插濾波器分為兩步實現(xiàn):第一級FIR成形濾波器,第二級內(nèi)插濾波器采用五級CIC濾波器?各信道濾波器內(nèi)插分解為兩級,大內(nèi)插系數(shù)濾波器由CIC完成,其結(jié)構(gòu)如圖2所示?實驗結(jié)果表明這樣做并不影響性能?

三路信道內(nèi)插濾波器分別描述如下:

(1)2.4kbps窄帶信號:編碼后信號采樣率為4.8kHz,要用78.336MHz進行采樣,必須經(jīng)過78336/4.8=16320倍內(nèi)插?第一級采用75階8倍內(nèi)插成形FIR濾波器,第二級采用2040倍五級CIC內(nèi)插濾波器?

(2)19.2kbps窄帶信號:編碼后信號采樣率為38.4kHz,要用78.336MHz進行采樣,必須經(jīng)過2040倍內(nèi)插?第一級采用75階8倍內(nèi)插成形FIR濾波器,第二級采用255倍五級CIC內(nèi)插濾波器?該路信道所有內(nèi)插濾波器頻率響應(yīng)如圖3所示?

(3)2.4kbps擴頻信號:編碼后信號采樣率為1.224MHz,要用78.336MHz進行采樣,必須經(jīng)過64倍內(nèi)插?第一級采用25階4倍內(nèi)插成形FIR濾波器,第二級采用16倍五級CIC內(nèi)插濾波器?

2.3.2 數(shù)字上變頻

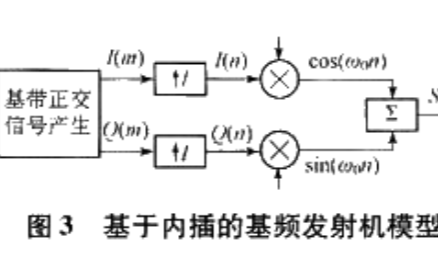

數(shù)字上變頻器的主要功能是對輸入數(shù)據(jù)進行各種調(diào)制和頻率變換,即在數(shù)字域內(nèi)實現(xiàn)調(diào)制和混頻?筆者設(shè)計了三個單路數(shù)據(jù)DUC?

在BPSK調(diào)制模式中,內(nèi)插濾波器把數(shù)據(jù)流采樣頻率升至時鐘頻率后,通過載波NCO進行混頻?DUC設(shè)計取22位累加器,SIN/COS的分辨率為12位?其頻率輸出調(diào)諧精度為18.68Hz?NCO簡單結(jié)構(gòu)如圖4所示?

2.3.3 信道復(fù)接

三路信道分別完成數(shù)字上變頻后經(jīng)過一個加法器變?yōu)橐宦沸盘査椭罝AC,這樣只需要一個RF模塊就可完成發(fā)射功能?如圖5給出了發(fā)射機信道復(fù)接后的頻譜?

2.4 Inverse-SINC預(yù)補償濾波器

Inverse-SINC預(yù)補償濾波器用于補償發(fā)射時由DAC采樣保持工作導(dǎo)致的頻率響應(yīng)的失真?該偏差在21.85MHz時為-1.142dB?為了達(dá)到性能最優(yōu)化,采用頻率采樣的方法設(shè)計了一個11階的補償濾波器,該濾波器頻率響應(yīng)如圖6所示?

為了分析發(fā)射機的性能,用矢量信號分析儀畫出各信道的星座圖與眼圖?圖7所示為窄帶19.2kbps信道的星座圖與眼圖,其性能可以滿足多功能地面站的要求?

本文采用了軟件無線電技術(shù)?實現(xiàn)衛(wèi)星地面站,具有很大的靈活性及現(xiàn)實意義?根據(jù)“創(chuàng)新一號”小衛(wèi)星對多功能地面站的研制要求,自行開發(fā)了一個軟件無線電多信道發(fā)射機系統(tǒng),具有功能強?功耗低?體積小?靈活性大等特點,極大地方便了用戶?

責(zé)任編輯:gt

-

處理器

+關(guān)注

關(guān)注

68文章

19259瀏覽量

229652 -

dsp

+關(guān)注

關(guān)注

553文章

7987瀏覽量

348745 -

FPGA

+關(guān)注

關(guān)注

1629文章

21729瀏覽量

602998

發(fā)布評論請先 登錄

相關(guān)推薦

FPGA-CPLD在軟件無線電中的工程應(yīng)用

FPGA在軟件無線電中的應(yīng)用

射頻轉(zhuǎn)換器為下一代無線基站提供高效的多波段無線電

軟件無線電的智能天線和多頻段和寬帶天線

軟件無線電結(jié)構(gòu)設(shè)計的器件選擇方法

軟件無線電設(shè)計解決方案

如何利用DSP設(shè)計軟件無線電基頻發(fā)射機?

怎么應(yīng)對多標(biāo)準(zhǔn)無線電基站發(fā)射機測試挑戰(zhàn)?

如何實現(xiàn)軟件無線電的設(shè)計?

一個針對多頻段應(yīng)用的直接RF發(fā)射機例子

如何設(shè)計并制作無線電遙控發(fā)射機和接收機

多標(biāo)準(zhǔn)無線電基站發(fā)射機測試

如何使用DSP設(shè)計軟件無線電基頻發(fā)射機

基于DSP及FPGA器件實現(xiàn)軟件無線電多信道發(fā)射機系統(tǒng)的設(shè)計

基于DSP及FPGA器件實現(xiàn)軟件無線電多信道發(fā)射機系統(tǒng)的設(shè)計

評論