0引言

CPCI總線[1]是由PCI總線發展而來的一種緊湊型32/64 bit局部總線,最高帶寬可達512 MB/s。因其具有高開放性、高可靠性、可熱插拔等優點,被廣泛應用于航空航天、信息通信、工業控制、數據采集等領域。相對于傳統的以單片機、MCU為核心的數據處理系統,現場可編程門陣列(Field Programmable Gate Array,FPGA)以其高速、靈活、高集成度、高性能、抗干擾、現場可編程等優點,在上述領域中得到了廣泛應用[2]。本設計將CPCI總線技術與FPGA技術巧妙結合,以Altera公司的高性能芯片EP3C40F324I7為核心處理器,根據應用需求,研制開發了一款實時性強、可靠性高的多功能通信卡。

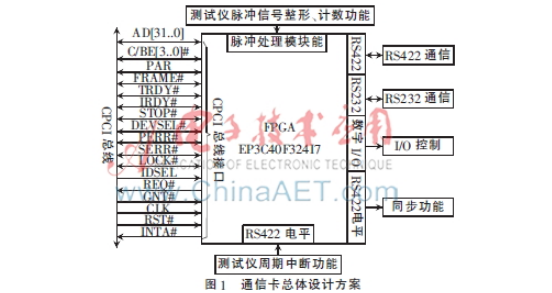

1 多功能通信卡總體方案

FPGA核心處理器EP3C40F324I7通過CPCI總線與主機進行信息交互,主要實現各模塊信號采集、處理、傳輸等功能。主機通過CPCI總線發送命令、數據,FPGA微處理器接到指令后,對相關信號進行處理,將處理結果通過CPCI總線反饋給主機,并通過標準的通信接口外接引出,從而進行分析、計算。該多功能通信卡總體方案如圖1所示。

2 硬件設計

2.1 FPGA芯片選型與設計

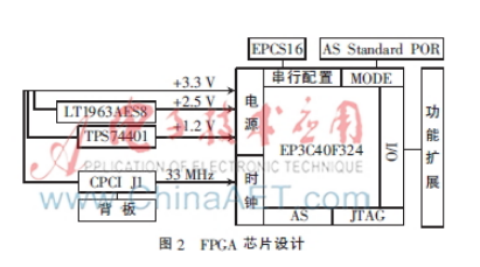

本設計中FPGA微處理器通過CPCI總線實現RS232串行通信、RS422串行通信、脈沖計數、數字輸出等多種功能,綜合考慮FPGA內部存儲單元數量、I/O引腳數量等因素,選擇Altera公司的EP3C40F324用于功能模塊開發。EP3C40F324為FPGA封裝,內部LE 39 600個,M9K 126個,RAM總量為1 161 216 bit,18×18的乘法器126個,鎖相環4個,全局時鐘網絡20個,可用I/O口195個,可用差分通道61個,可以滿足系統開發需求。

EP3C40F324需3種供電電壓,I/O供電電壓為+3.3 V,PLL的模擬供電電壓為+2.5 V,內核及PLL的數字供電電壓均為+1.2 V。其中,+3.3 V由背板經CPCI J1直接供給,+2.5 V通過電源芯片LT1963AES8由+3.3 V轉換而得,+1.2 V通過電源芯片TPS74401由+3.3 V轉換而得。設計中,充分考慮到芯片功耗問題,內核及PLL的數字供電特采用TI公司的TPS74401電源芯片將+3.3 V轉換為+1.2 V,其輸出電流為3 A,保證了電源功率。

FPGA的輸入時鐘由背板經CPCI J1提供,使CPCI總線頻率穩定在33 MHz。FPGA的上電復位模式選擇AS Standard POR。采用增強型配置芯片EPCS16對FPGA進行了主動串行(AS)配置,同時利用微處理器本身進行了基于JTAG的配置。兩種配置方案,保證了FPGA程序燒錄的可靠性、穩定性。FPGA芯片設計如圖2所示。

2.2 總線接口設計

本設計中采用32 bit/33 MHz CPCI總線接口,其傳輸率可達133 MB/s,實現了設備之間的高速通信。通過CPCI連接器,CPCI總線信號與FPGA的I/O口互連。

FPGA微處理器通過地址和數據信號AD[31..00]、總線命令和字節使能信號C/BE[3..0]#與主機進行I/O地址的選擇,以及數據、命令的傳輸。FRAME#、TRDY#、IRDY#、STOP#、DEVSEL#、IDSEL等接口控制信號用于設備選擇、讀寫控制。FPGA微處理器如需占用總線,則需向主機發出總線占用請求信號REQ#,主機收到總線占用請求信號后,通過仲裁向FPGA微處理器發送總線占用允許信號GNT#。由于總線上沒有掛接其他設備,故總線的使用由FPGA微處理器獨占。INTA#用于向總線進行中斷請求,以實現中斷功能。通信過程中如有錯誤發生,則FPGA微處理器通過PERR#、SERR#與主機進行錯誤報告,以保證數據傳輸可靠、完整[3]。

2.3 脈沖信號處理電路設計

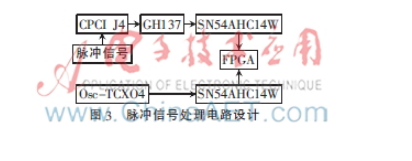

被測設備的脈沖信號通過CPCI J4連接器進入板卡。利用光電耦合器GH137對脈沖進行光電隔離,以減少板上其他信號的干擾,提高脈沖數字信號的抗干擾能力。經過光耦隔離的脈沖數字信號,由TI公司的SN54AHC14W進行波形整形。SN54AHC14W是帶有施密特觸發的6路反相器。施密特觸發器是脈沖波形變換中經常使用的一種電路,不僅能將邊沿變化緩慢的信號波形整形為邊沿陡峭的矩形波,而且可以將疊加在矩形脈沖高、低電平上的噪聲有效地清除。故經過SN54AHC14W整形的脈沖數字信號波形更加理想,易于FPGA微處理器進行處理、計數。

高穩定度溫度補償晶體振蕩器Osc-TCXO4產生的1 024 kHz時鐘脈沖,經SN54AHC14W整形后送入FPGA,供脈沖計數使用。由于本板卡應用于軍工、國防領域,需要非常穩定的晶振,故采用溫度補償晶體振蕩器。TCXO溫度補償通過改變振蕩回路中負載電容,使其隨溫度變化來補償由于環境溫度變化產生的頻率漂移,從而產生精度非常高的時鐘,提高脈沖計數精度。脈沖信號處理電路如圖3所示。

2.4 差分接口設計

本設計中有2路RS232串口,4路RS422串口,最高傳輸率分別為115.2 kb/s、921.6 kb/s。由于應用條件嚴苛,設計中選用了電磁隔離器件,大大提高了通信的可靠性。RS232收發器選用AD公司的ADM3251E,其數據傳輸率最高可達460 kb/s。RS422收發器選用AD公司的ADM2582E,其數據傳輸率最高可達16 Mb/s。二者均在器件內部集成了DC-DC轉換器,有效地降低了干擾,且其傳輸速率也滿足使用需求。同時,由于主機串口傳輸率為9 600 b/s,故選擇22.118 4 MHz的晶振為串行通信提供穩定時鐘。

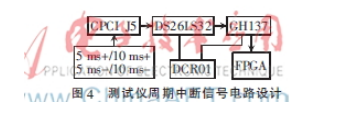

被測設備將周期5 ms和10 ms的時鐘信號輸出給板卡,作為測試儀周期中斷信號。時鐘接口電路采用422差分協議,電平采用422電平。時鐘信號經CPCI J5連接器進入板卡,接收器采用NS公司的4路差分接收器DS26LS32,以滿足422電平標準。調理之后的422電平信號經光電耦合器GH137加以隔離,以減少其他信號的干擾。

由于DS26LS32、GH137內部未集成DC-DC轉換功能,故需要有單獨的DC-DC電源模塊將板上電源進行隔離,以給二者供電。此處選用了TI公司的DCR01系列芯片完成隔離電源供電的功能。測試儀周期中斷信號電路設計如圖4所示。

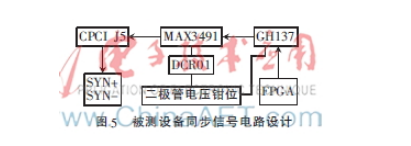

測試儀向被測設備發送RS422差分信號作為被測設備同步信號。同步信號接口電路采用422差分協議,電平采用422電平。同步脈沖從FPGA微處理器送出后,經光電耦合器GH137隔離,進入MAXIM公司的MAX3491收發器。MAX3491的數據傳輸速率可達10 Mb/s,滿足傳輸要求。信號經CPCI J5連接器外送至被測設備,以校準時差,實現被測設備同步功能。

同時,為減少其他信號的干擾,將對時脈沖采取隔離措施,由TI公司的DCR01系列電源芯片單獨供電。由于MAX3491與GH137的供電電壓不同,故通過二極管串聯電壓鉗位的方式獲得合適的供電電壓為GH137供電,有效解決了隔離供電問題。被測設備同步信號電路設計如圖5所示。

2.5 數字輸出電路設計

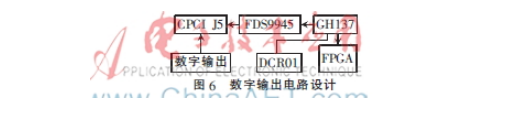

測試儀的I/O功能由數字輸出量來實現。FPGA通過設置寄存器方式向外輸出高低電平,以實現復位、控制等功能。高低電平從FPGA發出,經光電耦合器GH137隔離,提高信號抗干擾性能。經隔離的信號進入FAIRCHILD公司的FDS9945作為電平控制信號。

FDS9945內部為N溝道MOSFET,電平控制信號連接于場效應管的柵極G(Gate),場效應管的源極S(Source)接隔離地,漏極D(Drain)的輸出可作為復位、控制信號。漏極D的輸出電平經CPCI J5連接器外送至被控制的對象。利用MOS管的開關特性,通過改變柵極G的電平來控制場效應管源極S、漏極D的通斷,從而實現復位、控制等功能[4]。數字輸出電路設計如圖6所示。

3 FPGA程序設計

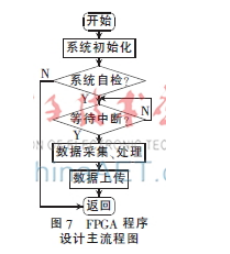

本采集卡FPGA邏輯設計采用Verilog代碼[5]實現,主要實現數據采集、存儲、讀寫等命令控制,其主流程圖如圖7所示。FPGA主要實現CPCI接口到RS232、RS422等接口轉換,以及422電平輸入輸出、數字輸出、脈沖計數等功能。PCI BAR0映射為8 KB IO空間,BAR1映射為1 MB Memory空間。PCI采用中斷復用,通過使能中斷寄存器而觸發不同協議的中斷,如RS232、RS422通信等,從而分別調用相應的中斷服務程序完成通信任務。

4 結果分析

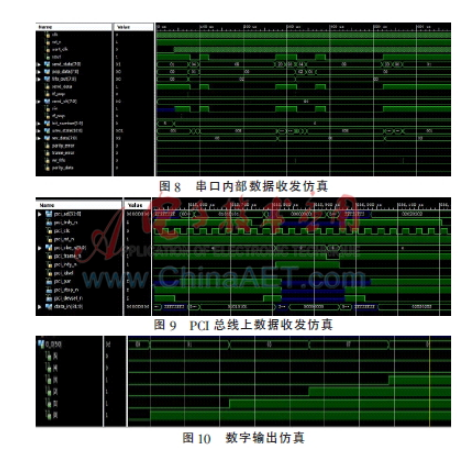

圖8為串口內部數據收發仿真,圖9為總線上數據收發仿真,圖10為數字輸出仿真。由實驗結果可知,該I/O卡在進行數據通信時,無論是串口內部的環回通信,還是PCI總線上的通信,讀寫信息一致,沒有產生通信錯誤。同時,6路數字輸出量也有由默認低電平到輸出高電平的跳變,完成了相應的數字控制功能。可見,該I/O通信卡成功實現了數據的實時采集、處理、上傳等功能,目前已投入實際應用之中,具有較高的使用價值。

參考文獻

[1] PICMG. Compact PCI specification 2.0 R3.0[S]. 1999.

[2] 羅苑棠.CPLD/FPGA常用模塊與綜合系統設計實例精講[M].北京:電子工業出版社,2007.

[3] 李貴山,陳金鵬.PCI局部總線及其應用[M].西安:西安電子科技大學出版社,2003.

[4] 閻石.數字電子技術基礎(第四版)[M].北京:高等教育出版社,2004.

[5] 夏宇聞.Verilog數字系統設計教程[M].北京:北京航空航天大學出版社,2009.

編輯:jq

-

FPGA

+關注

關注

1629文章

21729瀏覽量

603010 -

CPCI總線

+關注

關注

0文章

28瀏覽量

13517 -

通信

+關注

關注

18文章

6024瀏覽量

135950

發布評論請先 登錄

相關推薦

XMC 轉 CPCI 載板轉接卡

CPCI轉PCI載板轉接卡 PCI2CPCI

簡述計算機總線的分類

TCA5013支持1張用戶卡和3張SAM卡的多功能智能卡接口IC數據表

什么是多功能傳感器 多功能傳感器的功能介紹

CPCI設計與制造:提高可制造性的關鍵要素

簡述關于FPGA的CPCI總線多功能通信卡的設計

簡述關于FPGA的CPCI總線多功能通信卡的設計

評論