1 引言

集成電路制造工藝的飛速發展推動了信息技術的發展,而信息技術的核心是微處理器技術。微處理器的總體發展趨勢是功能越來越強大,工作頻率越來越高。由于微處理器芯片從設計過程到生產過程中都可能產生一些缺陷,這些缺陷都將最終影響微處理器的功能和性能,為了保證微處理器功能的正確性,減少設計風險,對其進行測試和調試是必不可少的。但是微處理器的發展趨勢也導致了微處理器芯片的測試與調試變得更加復雜,板級調試系統設計和調試軟件的開發也越來越困難。特別是進入21世紀,集成電路進入了高度集成的系統芯片SoC(System-On-Chip)時代,而嵌入式微處理器是系統芯片的核心。傳統的微處理器的調試方法采用監測并控制其地址與數據總線的方法。對于高度集成化的系統芯片,由于封裝尺寸的限制,不可能將嵌入片內的微處理器信號引出片外,通過外部直接測試和調試。在板級,通過軟件模擬、驗證和分析等系統功能調試已經遠遠不能滿足功能正確性調試和故障定位等要求,所以微處理器芯片,特別是嵌入式微處理器,硬件上支持片上測試和調試功能顯得十分重要。

為了能讓嵌入式微處理器的片上調試功能也能夠像高級語言編程工具那樣支持斷點設置、單步執行、寄存器內容的查看和內存內容查看等功能,文章提出了一種在線調試模塊設計,此設計為嵌入式微處理器增加了一些專用的調試引腳,通過這些引腳可以響應硬件和軟件觸發,提供開始/停止調試模試,單步調試操作以及程序執行的跟蹤。有了這些引腳,還可以對微處理器做調試接口,提供更好的調試性能,查錯功能,從基本停止/ 開始或單步執行到硬件、軟件斷點支持再到對數據存儲區、程序存儲區和SFRs的訪問和修改以及對程序進行跟蹤。

2 嵌入式微處理器的片上調試原理

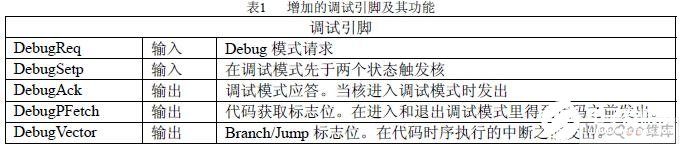

為微處理器增加的調試引腳及其功能如表1所示。

可實現的調試功能:

⑴ 開始/停止debug模式

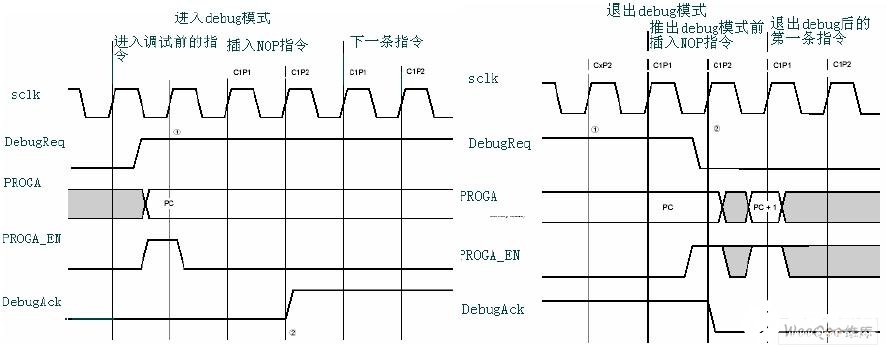

可以通過兩種方式進入調試模式即硬件請求或者軟件中斷指令TRAP。硬件請求進入到debug模式將發出一個DebugReq信號。這個信號在核運行的每個指令操作的最后一個周期的第一個階段進行采樣,若是采樣信號為高,核將完成當前指令,插入一個NOP指令。在NOP指令的第一階段的最后核將發出一個DebugAck信號然后進入debug模式。它的時序圖見圖1。當TRAP指令被執行的時候,核只是簡單的發送一個DebugAck信號,然后在這個單一周期指令第一個階段的結束進入debug模式。

在debug模式,核在每個機器周期的第一階段的最后采樣DebugReq信號,當DebugReq信號為高之后采樣一個機器周期的信號,如果為低則離開調試模式(置DebugAck信號無效)。它的時序圖見圖2。注意:如果在TRAP下進入調試模式,外部硬件必須在重新置信號為低之前置DebugReq信號為高一個機器周期才可以離開試模式。

圖1 進入debug模式的時序圖 圖2 退出debug模式的時序圖

①DebugReq采樣信號為高電平。① DebugRep采樣信號為高電平。

②微處理器內核進入調試模式,置DebugAck 為高電平。 ② DebugRep 采樣信號為低,CPU核置DebugAck為低并離開調試模式。

其中 PROGA 為程序存儲器的地址總線,PROGA_EN 為程序存儲器的地址總線使能。它們是微處理器內核已經設計好的。

⑵單步調試

在調試模式下,把DebugReq 置成無效的低信號,微處理器執行一個用戶指令,等待DebugAck 信號無效的時候指出離開了調試模式,再把DebugReq 信號置成高電平。

⑶程序執行的跟蹤信號 DebugPFetch 和Debug Vector 支持程序追蹤。當程序代碼在下一個上升緣被讀取的時候DebugPFetch信號發出,它并不發送程序數據提取的信號。(例如使用MOVC 指令讀取數據)。當在程序計數器里的下一個代碼表現為一個間斷性程序的時候DebugVector 被發送,(例如Jump,Call 或者Return 指令)。

⑷外部數據存儲器、SFR、內部數據存儲器的讀和寫

提供了一個時序發生器一個RAM,它包含了一些訪問存儲器的指令。當一個時序開始的時候,DebugStep信號發送直到時序結束。因此時序指令以全速的處理器速度運行。在微處理器程序輸入端設計了一個多路選擇器允許時序發生器的指令給內核執行。時序發生器中的指令總是把想訪問的存儲器和SFRs 中的數據加載到累加器A 中,因此只要把XRAMD0 總線的狀態存儲到結果儲存器中,然后通過JTAG 接口把結果儲存器讀出就可以得知存儲器和SFRs 中的數據。給出一個讀內部數據存儲器的時序發生器中的程序。其中Temp1,Temp 是時序發生器中定義的存放中間數據的寄存器。

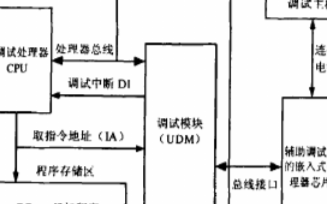

3 微處理器的在線調試模塊的結構設計

在微處理器內核中設計的調試部分為DebugReq 信號鎖存器、調試狀態機、操作碼指示器。

調 試 狀 態 機 是 有 DebugReq 、DebugAck、DebugStep、TRAP 信號來控制的。它有4 種狀態:00、01、10、11。00 表示用戶狀態。01 表示調試開始狀態,此狀態時已檢測到DebugReq 信號有效,插入NOP 指令。01 表示單步調試模式,已檢測到DebugStep 信號有效。11 為調試模式。狀態機為10、11 時都要置DebugAck 為有效信號,進入Debug 模式。

操作碼指示器是有指令譯碼器和狀態機譯碼器控制的。當程序代碼在下一個上升緣被讀取的時候(而不是程序數據的讀取), 操作碼指示器就置DebugPFetch 為有效信號,以實現對程序的跟蹤。當操作碼指示器檢測到程序計數器為不連續數值時置DebugVector 為有效信號。

外部數據存儲器、SFR、內部數據存儲器的讀和寫是基于1149.1 JTAG 的設計。IEEE 1149.1 JTAG 接口是專門為集成電路測試和電路板系統測試制定的國際標準。TDI(數據輸入),TMS(TAP 模式選擇),TCK(測試時鐘輸入),TRST(測試接口復位),TDO(數據輸出)是JTAG 的5 個外部管腳。調試部分電路為:調試掃描鏈、調試數據寄存器、指令譯碼器、時序發生器和多路選擇器(MUX)。時序發生器是一個RAM,它包含了一些訪問存儲器的指令。指令010110xx 表示啟動時序發生器,把預先存好的訪問程序送到微處理器的程序輸入端(PROGDI),微處理器執行這些程序,實現對存儲器、SFR 的訪問。指令譯碼器對調試指令進行譯碼,并發出調試控制信號,比如:設置DebugReq 為有效,進入Debug 模式;啟動時序發生器,控制多路選擇器(MUX),讓PROGDI 上的信號為時序發生器中的指令。調試數據寄存器是為存放中間數據和訪問結果數據的。調試掃描鏈對中間數據和訪問結果進行查看。

4 結論

此設計給微處理器內核增加了一些調試引腳。實現了開始/停止調試模試,單步調試操作以及程序執行的跟蹤的調試功能。這些引腳使內核具有很好的可擴張性,可對芯片增加調試接口,實現更強大的調試功能。基于1149.1 JTAG 接口的對存儲器、SFR 訪問,既可以使芯片原有的測試功能不受影響,又可以節省硬件,減少開銷。帶Debug 模塊的微處理器在SMIC 的0.25um 標準單元庫映射綜合后,可工作在120MHz。仿真的結果表明,擴充Debug 功能的JTAG 接口所增加的芯片面積很少,而且在對存儲器、SFR 進行訪問時不影響處理器的工作速度。

責任編輯:gt

-

芯片

+關注

關注

455文章

50714瀏覽量

423151 -

嵌入式

+關注

關注

5082文章

19104瀏覽量

304816 -

微處理器

+關注

關注

11文章

2258瀏覽量

82403

發布評論請先 登錄

相關推薦

接口調試與測試工具postman安裝說明與基礎功能

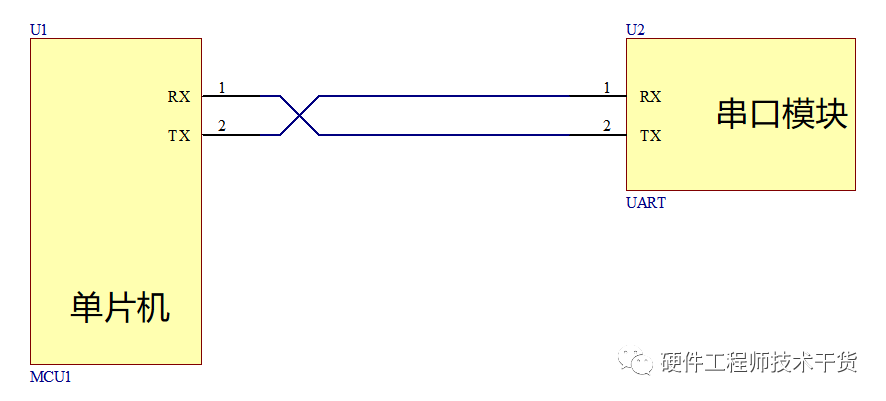

單片機串口模塊調試方法

英創Eclipse支持在線調試Linux應用程序

玩轉Zynq連載5——基于Vivado的在線板級調試概述

總線實現片內硬件調試支持單元設計

總線實現片內硬件調試支持單元設計

基于雙端口RAM中多行代碼設置斷點功能實現新型通用調試模塊的設計

PLC遠程調試模塊是什么?PLC遠程調試模塊的功能

支持片上測試和調試功能的在線調試模塊的應用設計

支持片上測試和調試功能的在線調試模塊的應用設計

評論