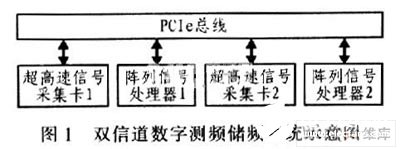

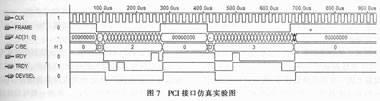

在雷達對抗系統中,需要對于雷達信號進行實時測頻,并可以對感興趣的信號進行儲頻,為假目標欺騙干擾或壓制干擾提供測頻結果和儲頻數據。而數字測頻是當今發展最快的測頻技術之一。數字測頻、儲頻的關鍵技術之一即是超高速、高精度、不間斷的信號采集技術。采樣速率和精度的不斷提高,使得數據傳輸和存儲越來越成為數據采集系統的技術瓶頸。目前大部分高性能數據采集卡都是基于PCI、CPCI、VME等總線,最高持續傳輸速率難以超過400 MB/s,因此大多數采集卡采用采集和存儲分時工作的模式,即在板內設有一定容量的存儲器,當存儲器存儲數據到一定量時,停止采集而開始上傳數據,上傳完畢后再重新啟動采集,不斷循環,文獻也提出采集傳輸的流水工作模式,提高采集的效率。這些工作方式雖然也能滿足大部分數據采集的要求,但是在信號非常密集的環境中,交替工作模式將導致偵察截獲概率降低,帶來干擾的效能下降。基于上述原因,本文論述了一種基于PCIe總線的數據采集卡,該采集卡不但可以達到800 MHz/s采樣率、14 bit采樣精度,還具有不間斷采集、實時上傳的能力(在測頻只取其中8位分辨力,儲頻時取14位分辨力,根據系統的總數據量可編程)。該采集卡可以與高速信號處理器配合使用,構成信道化的數字測頻、儲頻系統,雙信道系統的組成示意圖見圖l。

1 系統總體設計

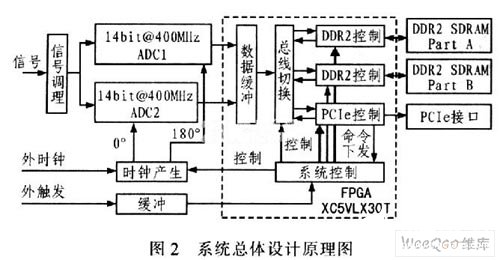

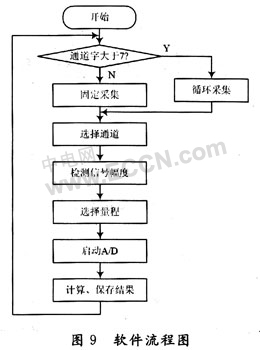

本采集卡的設計主要包括超高速A/D轉換器模塊、時鐘產生模塊、大容量存儲器模塊和基于FPGA的控制模塊。如圖2所示,待采集的模擬信號經過信號調理放大到合適的電平范圍,送入到兩片工作于交叉采樣模式的A/D轉換器,轉化后數字信號直接送至FPGA控制器,在FPGA內部實現信號電平轉換數據緩沖后,首先存儲于A路動態存儲器中,當A路存儲器存滿后,數據立即轉存于B路存儲器,同時啟動數據上傳操作,將A路存儲器的數據通過DMA方式上傳至主機存儲或傳輸到信號處理板中;當B路存儲器存滿后,數據存儲立即切換至A路存儲器,同時也啟動B路存儲器的上傳操作,如此反復循環。由于PCIe接口傳輸速率大于信號采集速率,因此可以保證數據的不丟失。

2 雙路高速高精度A/D轉換器設計

高速A/D轉換器模塊是采集卡工作的最前端,它的設計優劣將決定著采集卡的性能指標。其中信號調理部分的功能就是在保證待測信號不失真的前提下,對輸入的信號進行低噪聲放大、濾波等處理。由于待采集的信號為高頻信號,需要進行阻抗匹配和前置放大,可以選用低失真的有源放大器或射頻變壓器。有源放大器的優點是輸入動態范圍大,在一定帶寬內增益可調,缺點是有源設計會引入一定噪聲;射頻變壓器的優點是無源設計、帶寬相對高,缺點是增益固定不可調,輸入信號的幅度受到限制,并且給系統帶來插入損耗。綜合考慮系統設計指標要求,本系統選用TI公司的THS4509放大器作為信號調理器件,該運放具有非常好的寬帶特性,增益設置為10 dB時,-3 dB帶寬達l900 MH-z,單電源供電以及輸出共模電壓可調的特性使得THS4509非常適合于高性能的信號采集系統中;考慮到目前市場上難以得到單片A/D轉換器可以達到800 MHz/s采樣率和14 bit分辨率的設計指標,因此采用了兩片ADS5474作為本采集卡的A/D轉換器,該A/D轉換器的最高采樣率為400MHz/s,14 bit的分辨率,-3 dB帶寬達l 400 MHz,LVDS電平的信號輸出可以直接連接至FPGA處理器,方便了系統設計,兩片ADS5474 工作于交叉采樣模式,達到了等效于800 MHz/s的采樣效果。

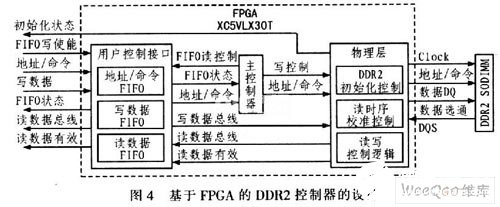

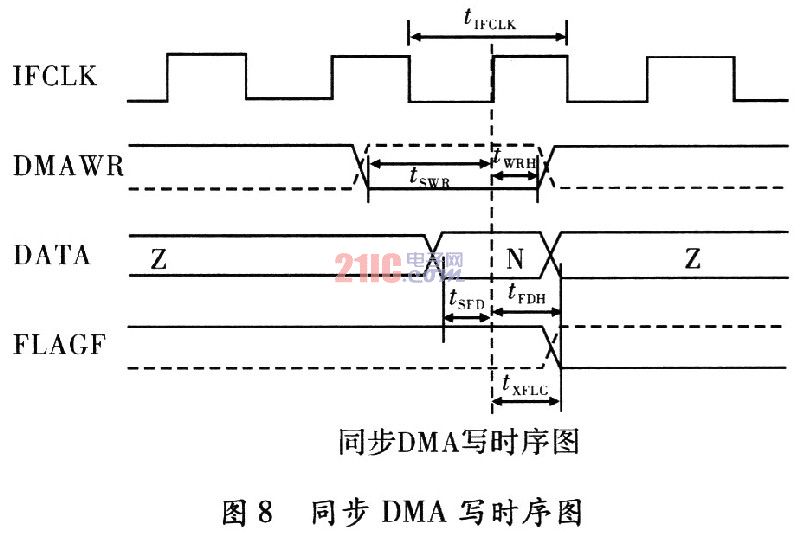

信號采集是連續的,而數據的上傳是由主機軟件通過DMA方式間斷獲取,因此需要設計大容量的存儲器以緩存數據,同時為了達到不間斷采集目的,設計了兩塊存儲區采用乒乓緩存的工作方式,即一塊存儲區用于緩存A/D轉換器高速數據時,另一塊存儲區用于將先前已存儲的數據上傳。大容量內存采用Micron公司的內存模塊MT4HTF3264HY-53E,該內存模塊容量256 MB,數據總線寬度64 bit,采用SODIMM封裝形式,數據訪問帶寬最高可達4.3 GB/s,遠超出本系統的需求。

當采集卡工作于最高采樣率800 MHz/s、14 bit分辨率時,轉換的數據率將會達到1.6 GB/s,給后續的數據傳輸帶來非常大的壓力。常用的總線如PCI,PXI等已經滿足不了如此高的速率要求,本系統采用了8通道的PCIe總線來實現高速數據傳輸,每通道運行速率2.5 Gb/-s,采用8b/10b編解碼方式工作,可以得到總數據帶寬約2 GB/s,達到實時傳輸數據的要求。

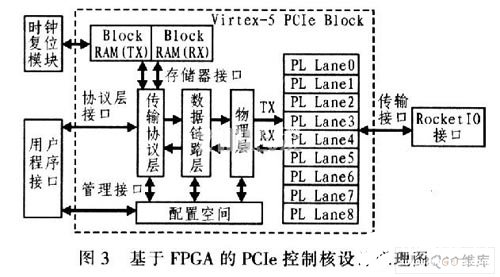

3 基于IPCORE的PCIe控制接口設計

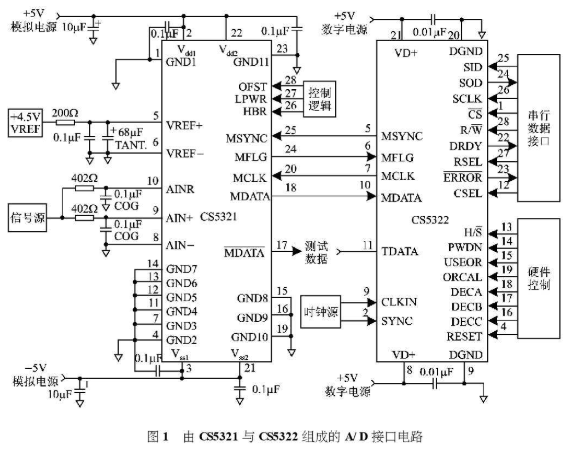

PCIe接口控制電路是本采集卡的關鍵模塊,通過PCIe控制核完成主機與采集卡的數據交互。PCIe擁有多種組件類型,每一類型均采用了復雜的系統級折衷方案,以滿足嚴格的設計目標。為了能加快產品研發進度,本設計采用Xilinx公司的Logicore IP for PCI Express來設計PCIe高性能互連設計接口,該IP核占用FPGA資源少、功耗低,包含有物理層、數據鏈路層、傳輸協議層和配置空間。如圖3所示,層與層之間有明確的分工,相比PCI總線不分層的協議描述更加抽象,傳輸協議層與數據鏈路層負責將采集到的數據按批次組包,包在層與層之間傳遞時會附加對應的校驗和幀信息。PCIe標準使用應答重傳機制,在數據鏈路層包括相應的應答延遲和重傳延遲定時器,這兩個定時器收到串行解串模塊與傳輸介質延遲的影響比較大,太小的重傳延遲往往會造成不必要的重傳,從而顯著降低性能,因此在不同的采集環境下需要進行針對性的調整。設計中這兩個定時器的值可以通過軟件界面進行配置修改,通過驅動軟件來動態修正兩個定時器以達到采集傳輸性能的最優化。

![]()

4.2 系統采集時序控制

系統控制模塊完成采集數據上傳、主機命令的下發和執行:系統控制采用有限狀態機的控制方式,如圖5所示。當系統上電后控制器默認進入初始化狀態,完成默認參數的配置,包括采樣頻率、采樣深度、觸發方式、時鐘源的選擇、模擬輸入的量程和耦合方式等,初始化執行完畢后進入空閑狀態,等待接收主機命令和執行操作;當接收到啟動采集的命令后,控制器首先將AD輸入的數據總線掛接在內存A數據總線上,并啟動內存A的DDR2控制器執行寫操作;當內存A存儲到軟件設定的深度或存滿時,切換AD輸入的數據總線掛接在內存B數據總線上,啟動內存B的DDR2控制器執行寫入操作,同時通過DMA中斷通知主機,等待主機上傳內存A中的數據;如此反復循環工作,直到收到主機停止采集的命令再返回到空閑狀態。

5 結束語

本文介紹了基于PCIe高速串行總線和FPGA控制器的超高速信號采集卡的設計技術,實現了不間斷采樣和連續傳輸等關鍵技術。采集到的信號頻譜見圖6。該采集卡已應用于某雷達偵察和干擾系統,取得了良好的效果,具有重要的實用價值。

責任編輯:gt

-

轉換器

+關注

關注

27文章

8694瀏覽量

147085 -

數據采集

+關注

關注

38文章

6053瀏覽量

113622 -

總線

+關注

關注

10文章

2878瀏覽量

88052

發布評論請先 登錄

相關推薦

基于TMS320F28335與AD7767高精度數據采集模塊設計

FPGA控制CLC5958型A/D轉換器實現的高速PCI數據

基于雙路高速高精度A/D轉換器和PCIe總線實現數據采集系統的設計

基于雙路高速高精度A/D轉換器和PCIe總線實現數據采集系統的設計

評論