Astro-Rail工具為芯片設計提供了在設計和簽核階段進行功耗、電壓降和電遷移分析的功能。用Astro-Rail工具對一個5百萬門的設計進行功耗、電壓降和電遷移分析,所需時間不到一個小時。分析完成后,Astro-Rail將可能出問題的區域用不同的顏色在版圖上清晰地顯示出來,以幫助設計者分析并查找問題。其提供的簽核分析結果和Star-RCXT反標后再分析的結果相差不到5%。Astro-Rail是Synopsys Galaxy平臺的一個重要部件,利用獨有的動態宏模塊技術取得了突破性的速度,是一般rail分析工具速度的2倍“3倍。

文中的FFT芯片是16位的128點FFT/IFFT定點處理器,該處理器主要應用于基于OFDM的UWB系統,采用了N=4×4×4×2的算法實現定點的FFT運算。它采用了兩級流水線的結構,包括三級的基-4運算和一級的基-2運算。該設計的時鐘頻率為62MHz,采用SMIC 0.18mm 1P5M CMOS工藝,用Astro工具完成3.7mm×3.7mm版圖面積平面規劃、電源環和電源條預布線,用PC工具進行基于時序和阻塞的布局,再用Astro工具完成時鐘樹綜合和布線。在滿足靜態時序分析和設計規則檢查的情況下,利用Astro-Rail工具對FFT芯片進行功耗分析來判斷電源和地的Pad對數目是否符合要求,通過電壓降和電遷移分析來判斷電源環和電源條的布線是否符合電壓降和電遷移要求。

Astro-Rail分析門級功耗的方法

用Astro-Rail工具分析門級功耗包含四個部分:開關功率、短路功率、內部功率和泄漏功率。

開關功率

單元門器件的輸出端與地之間會形成一個電容,器件導通或關斷時對該電容進行充電或放電所消耗的功率即為開關功率。Astro-Rail計算開關功率的公式為:P=C×V2×f/2。其中f為信號跳變率,即單位時間內信號在高低電平之間跳變的次數;C為門器件輸出端的線負載電容,其數值可以通過線負載模型提取,也可以在物理設計完成后從版圖中提取,后者具有較高的精度;V為電源電壓。

短路功率

當一個單元的狀態從0變為1或從1變為0時,對應的N型和P型管在短時間內同時導通,從而在單元門器件中產生從電源到地的通路,此過程中消耗的功率稱為短路功率。

內部功率

對一個單元門器件來說,不是每一次輸入信號狀態的變化都會導致輸出信號的狀態改變。這種輸入信號狀態發生變化而輸出信號狀態不變的情況下所消耗的功率被稱為內部功率。以二輸入或門為例,當A、B輸入均為1,則輸出X為1,這時若輸入B從1變為0,輸出X狀態不變,但輸入B控制的管子狀態發生變化,從而消耗內部功率。

泄漏功率

泄漏功率是指晶體管沒有進行開關動作時所消耗的功率。盡管在晶體管漏極和襯底之間的一些反向偏置二極管中存在著漏電流,但大部分泄漏功率來自晶體管關斷時的亞閾值電流。當一個設計已經確定后,其泄漏功率是恒定的,與芯片的工作狀態無關。

FFT芯片的功耗分析

Astro-Rail分析FFT芯片功耗的流程主要包括5個步驟。

查看工藝庫文件

在smic18_apollo_m5.tf工藝庫文件中查看所定義的電壓、功耗、電流等單位,通過搜索關鍵字maxCurrDensity尋找各金屬層和各過孔的最大電流密度值。

在Milkyway環境創建LM目錄

Milkyway 環境是 Synopsys 針對超深亞微米(納米級)設計所建立的一種數據庫,它大大方便了整個物理設計實現的流程。LM目錄為Astro-Rail工具分析門級功耗、電壓降、電遷移提供了所必需的時序信息和功耗信息。由于SMIC 0.18mm CMOS工藝在Milkyway環境中無LM目錄,因此需要在Astro環境下使用gePrepLIbs命令創建LM目錄。具體的方法是:在STD(標準單元庫)目錄下,進入Astro環境,輸入gePrepLIbs命令,執行后會打開對話框,在對話框中進行相應設置即可生成STD的LM目錄。用同樣的方法創建標準IO的LM目錄。

導入VDD網絡的電壓值

Astro-Rail工具用VDD的電壓值來計算芯片的功耗,默認值為0V。指定VDD網絡電壓值的命令為:

tdfSetPowerSupply“VDD”1.621.81.98

將該命令保存在Powersupply.tdf文件,然后執行poLoadPowerSupply命令,彈出對話框輸入該文件進行導入。

導入芯片的信號跳變信息

為正確分析各種單元門器件的功耗,關鍵是要精確計算每個單元門器件的信號跳變率。對于本文使用的0.18mm工藝而言,芯片的功耗主要取決于動態功耗,而動態功耗依賴于不同的輸入向量,通常需要針對芯片各個部分設計大量的輸入向量進行仿真,以記錄信號跳變信息。信號跳變信息由Value Change Dump(VCD)文件記錄。導入芯片的信號跳變信息時,先執行菜單命令Power>Load NetSwitching Activity,在彈出對話框的輸入格式中選擇VCD模式,然后輸入VCD文件名后按OK按鈕即可導入。

功耗計算

執行菜單命令Power>PowerAnalysis,在彈出的對話框中進行適當選擇后,按OK按鈕對FFT芯片進行功耗計算。結果如下 :開關功率為293.88mW,短路功率為293.991mW,內部功率為160.541mW,泄漏功率為0.1159mW,總功耗為748.527mW,總電流為Itotal=415.848mA。根據工藝庫文檔可知:電源和地 PAD允許通過的最大電流都為Imax=51mA,則可確定電源和地 PAD的最小對數n:

n= Itotal/Imax=415.848/51=8.15

在本文的FFT芯片中布置有12對電源和地PAD數,故符合要求。在設計中,應該多放置幾對電源和地PAD,不但可以減少電壓降,冗余的電源、地PAD以及鍵合線(Bonding Wire)都可以減少寄生電容,從而降低順勢電流變化而導致的電壓波動。

FFT芯片的電壓降和電遷移分析

芯片電源完整性分析包含電壓降分析和電遷移效應分析。電壓降分析包含計算對電源網絡VDD的電壓降和對地網絡GND的電壓反彈值。對電源網絡VDD的電壓降是由芯片中電源網絡的金屬連線電阻所造成的,導致電源和地之間電勢差降低;對地網絡GND的電壓反彈主要是由于開關電流流經連線或襯底的電感引起,也可能由于連接電源和地的封裝引線電感引起。電壓降和地電壓反彈都會減小邏輯門的噪聲容限,增加時延。電遷移是由于金屬連線中存在高密度的電流,從而在金屬的正偏壓端和負偏壓端之間形成金屬導電原子流動。這股強烈的原子流有可能導致金屬的斷裂(金屬連線開路)或是擠出(金屬連線短路)。因此,完成功耗分析后對FFT芯片進行電壓降分析和電遷移分析是十分必要的。

抽取電源和地網絡參數

要正確分析電壓降,需要抽取電源和地網絡的電阻和電容值。執行poPGExtraction命令,打開對話框,在PG net name中選擇VDD按Apply按鈕,再選擇GND按OK按鈕,即可完成電源和地網絡參數抽取。

定義理想電源輸入點

在分析電壓降和電遷移的過程中,用poGenUserDefineTap命令自動生成用戶定義的理想源輸入點。具體做法是:先執行poGenUserDefineTap命令,彈出對話框,接著在FFT版圖窗口左邊的快捷按鈕點擊 Layer panel選項,在彈出的對話框中選擇僅顯示M1層(層號為61)。用鼠標左鍵點擊每個VDD的PAD與VDD網絡線連接處,則該點位置會自動加入vddtaps文件中,并在命令窗口顯示:Writing tap (VDD 61 336.750 3514.180)into file ”vddtaps“。用同樣的方法定義分析地電壓反彈時所需的理想電壓輸入點文件gndtaps。

計算最大電壓降

輸入poRailAnalysis命令,彈出對話框,在P/G pad info中選擇用戶定義的Tap,在用戶定義的Tap文件中輸入文件名vddtaps,選中Extract Option選項分析電壓降。從分析結果中可知,最大的電壓降為70.726mV,小于0.1VDD即180mV,證明FFT芯片電源環和電源條的布置符合電壓降的要求。

計算最大地電壓反彈,只需在用戶定義的Tap文件中輸入文件名gndtaps,選中Extract Option選項即可分析地網絡。從分析結果中可知,最大地電壓反彈為46.419mV,小于0.1VDD即180mV,證明FFT芯片電源環和電源條的布置符合地反彈電壓要求。

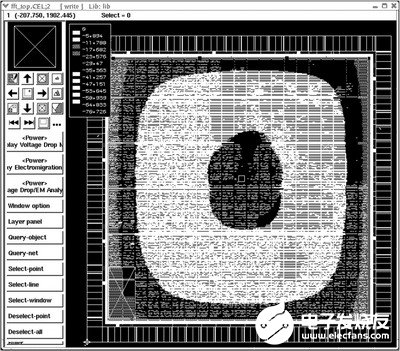

顯示電壓降圖

當軌道分析完成后,可用不同顏色來顯示芯片FFT不同部位的電壓降情況。具體做法為:執行菜單命令Power>Display Voltage Drop Map…,彈出對話框,在PG Net中選擇分析VDD,按Apply按鈕后自動指定最大的電壓降值-70.726mV。對最大的電壓降值-70.726mV進行12等分,并選擇將每一等分范圍及對應的顏色配置顯示在FFT芯片版圖上,按OK按鈕后得電壓降圖,如圖1所示。從圖中可知,中間呈蛋形的區域對應的電壓降大,該區域中的高亮小矩形表示此處的VDD網絡電壓降最大。地電平反彈圖可用同樣的方法分析。

圖1 FFT芯片電壓降圖

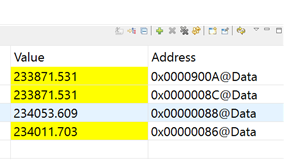

顯示電遷移圖

電遷移圖可用不同顏色來顯示芯片各層及過孔在芯片FFT不同部位的電流密度情況。顯示電遷移圖的具體方法是:執行Power> Display Electromigration Map…菜單命令,彈出對話框,在PG Net中選擇分析VDD,然后點擊Color,Metal,Via Bounds按鈕,打開如圖2所示的對話框。對話框中各金屬層和過孔所允許的最大電流密度按smic18_apollo_m5.tf工藝庫文件中的指定自動填入。可根據實際情況修改各金屬層和過孔所允許的最大電流密度。

選擇圖2中的M1金屬層,并按OK按鈕進行分析,得到M1層電遷移圖,如圖3所示,可在FFT芯片版圖上用12種不同顏色來顯示不同部位的電流密度情況。從圖中可知,M1層中電遷移率較大區域的參數值范圍為6.667”7.5,小于M1層所允許的最大電流密度10。用同樣方法可分析其它金屬層和過孔的電遷移圖,從圖中可判斷出,各金屬層和過孔的電遷移率都小于所允許的最大電流密度,從而證明FFT芯片電源環和電源條的布置符合電遷移要求。

圖2 金屬層和過孔允許最大電流密度

圖3 FFT芯片M1層電遷移率圖

結語

隨著集成電路制造技術的不斷提高,集成度越來越高,對應的功耗、電壓降和電遷移問題也越來越突出。減小芯片功耗的方法與設計有關;解決電壓降的主要方法是增加電源線和地線的寬度及數量,合理布置電源網絡;解決電遷移問題的主要方法是增加電源和地PAD對的數量,增加電源線和地線的寬度及數量,對關鍵路徑設置較寬的連線。通過利用Astro-Rail工具對電源和地網絡進行參數提取,再進行功耗、電壓降和地反彈電壓計算,并顯示電壓降和電遷移分析的結果,能夠確保芯片中與功耗相關的電源和地PAD對數,與電源環和電源條布局布線相關的電壓降、地電壓反彈和電遷移效應等問題得到解決。

責任編輯:gt

-

電源

+關注

關注

184文章

17773瀏覽量

250754 -

處理器

+關注

關注

68文章

19347瀏覽量

230244 -

晶體管

+關注

關注

77文章

9705瀏覽量

138475

發布評論請先 登錄

相關推薦

浮點處理器相對于定點處理器有何不同

基于FPGA的FFT和IFFT IP核應用實例

玩轉Zynq連載48——[ex67] Vivado FFT和IFFT IP核應用實例

FFT和IFFT的Matlab實現

FFT和IFFT的Matlab實現

基于FPGA的FFT處理器的研究與設計

高速定點FFT處理器的設計與實現

基于128點FFT/IFFT定點處理器解決電壓降和電遷移問題

基于128點FFT/IFFT定點處理器解決電壓降和電遷移問題

評論