數字硬盤錄像機,英文名稱為Digital Video Recorder,簡稱DVR,它是視頻監控系統中重要的設備,用于替代早期的長延時錄像機或者磁帶錄像機。目前硬盤錄像機從硬件架構上分主要分為工控式硬盤錄像機(或者工控硬盤錄像機或者PC式硬盤錄像機)、嵌入式硬盤錄像機,從壓縮算法來分有小波壓縮、MJPEG、MPEG4、H.264等。目前工控式硬盤錄像機和嵌入式硬盤錄像機所占市場比重差不多,由于嵌入式硬盤錄像機的穩定性及易維護性,選擇嵌入式硬盤錄像機的用戶會越來越多,市場前景非常大。基于這種應用背景,本文提出了嵌入式硬盤錄像機的設計思路和實現方案。

系統總體方案

1 技術指標

本系統的主要技術指標如下。

● 視頻輸入:16路復合視頻輸入PAL/NTSC。

● 視頻輸出:2路復合視頻輸出PAL/NTSC(BNC接口,1.0VP-P, 75Ω)。

● 音頻輸出:16路音頻輸入20~100mV10kΩ(RCA)。

● 音頻輸出:2路音頻輸出,20~100mV,1kΩ(RCA)。

● 系統資源:同時多路錄像、同時錄像回放、同時網絡操作。

● 圖像壓縮:增強型H.264,視頻和音頻信號壓縮后生成復合的H.264碼流,碼流回放時視頻和音頻保持同步。也可設置單一視頻流。

● 音頻壓縮:G.729

2 設計方案

根據系統要求的技術指標,本文設計的16路嵌入式DVR系統硬件部分采用了主從式雙CPU架構模式。主CPU選用了ARM9處理器,具體型號為三星半導體的S3C2510A,從CPU選用DSP處理器,具體型號為美國德州儀器(TI)的多媒體處理芯片TMS320DM648。主從CPU之間通過PCI總線進行通信。

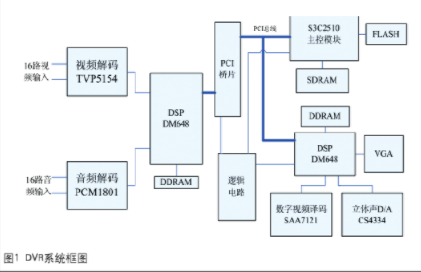

整個系統的工作流程設計為:系統上電或復位后,主CPU S3C2510A從Flash加載程序,完成對芯片的初始化和外圍硬件的配置,之后從CPU TMS320DM648便開始進行圖像采集。從CPU通過I2C口對系統中的視頻解碼芯片進行控制,將從攝像頭采集到的模擬視頻信號轉換為數字視頻信號,送入DM648的視頻通道(VP端口);同步采集到的模擬音頻信號經過音頻編解碼器模/數轉換后,送入DM648的音頻通道(McASP端口)。DM648將接收到的數字視頻信號和數字音頻信號數據分別進行壓縮,再把壓縮視頻流和壓縮音頻流進行同步復合,產生H.264視頻復合流,再通過PCI總線上傳給主CPU,主CPU將從PCI接口收到的數據以文件的格式存儲到本地硬盤,供日后調用;同步將復合數據流傳送給圖像預覽芯片進行顯示。整個DVR系統框架圖如圖1所示。

系統原理設計

1 S3C2510A ARM9處理器簡介

S3C2510A是三星半導體生產的16/32位的RISC微控制器,屬于ARM9處理器系列,是針對基于以太網系統的低成本、高性能的微控制器解決方案。

2 TMS320DM648數字信號處理器簡介

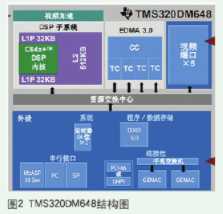

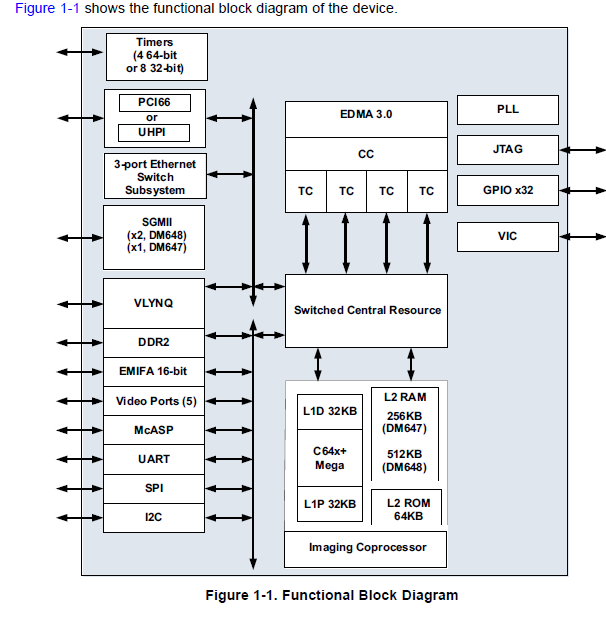

TMS320DM648是TI公司于2007年推出的一款高性能的32位定點DSP,主要面向數字媒體應用,屬于C6000系列DSP。

DM648保留了C64X原有的內核結構,工作頻率由內部倍頻器設置,可以達到720MHz、800MHz或900MHz,相應的時鐘周期為1.39ns、1.25ns或1.11ns,每秒可執行指令數5760、6400和7200MIPS。此外DM648片上帶有5個雙通道(A、B兩通道)數字視頻口(VP口),可同時處理多路數字視頻流,片上帶有多通道串行音頻接口,可同時處理10路立體聲輸入/輸出音頻信號。

核心模塊原理設計

整個數字硬盤錄像機根據功能可以劃分以下幾大核心模塊:

①主控制模塊;

②視音頻采集、壓縮模塊;

③視音頻預覽、回放模塊;

④其他模塊(電源、存儲器擴展、網絡傳輸、邏輯控制等);

本文詳細介紹主控制模塊和視頻處理模塊的設計。

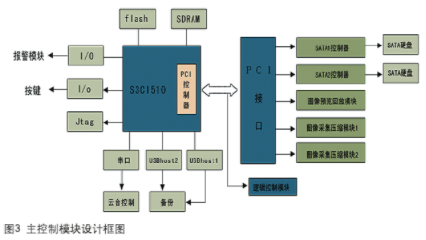

1 主控制模塊

本模塊主要實現系統的控制,對整個系統任務的運行進行分配與調度。S3C2510A本身內置PCI控制器,5個PCI接口可分別和2個音/視頻壓縮模塊,1個圖像預覽,回放模塊,2個數據存儲模塊連接;再加上已有的串口,USB接口,網絡接口,I/O等組成整個系統的控制模塊。設計思路如圖3所示。

2 視音頻采集/壓縮模塊

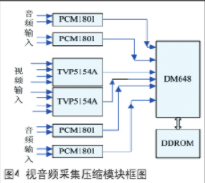

視音頻信號處理的流程如下:模擬視頻信號先經視頻解碼器TVP5154A轉換成8位YUV數字視頻信號Y[7:0],再送至DM648的視頻輸入接口。模擬音頻信號經音頻AD轉換器PCM1801轉換為I2S格式的音頻數據,進入多媒體壓縮芯片的音頻輸入接口,DM648將原始的視頻和音頻數據分別進行壓縮,再把壓縮視頻流和壓縮音頻流進行同步復合,產生H.264視頻復合流。一片DM648可以同時產生8個視/音頻通道的H.264復合數據流。DM648把每個視/音頻通道的復合視頻數據在片外DDRAM的數據緩沖區中排列成固定長度的數據包。當緩沖區內的數據量超過一定的閾值,它就通過PCI中斷向主CPU發出請求,當中斷被響應時,主CPU從包緩沖區內將數據取走。

DM648具有5個視頻端口,支持多種分辨率和標準,如CCIR601、ITU-BT.656、BT.1120等,每個端口為20bit位寬,可以被靈活的配置為一個20/16bit或兩個10/8bit通道。同時,每個端口都可配置為視頻輸入或視頻輸出。

TVP5154A具有4個通道,每個通道均為具有可編程多態換算器(polymorphic scaler)的獨立解碼器,可通過嵌入式同步模塊將NTSC、PAL或SECAM視頻信號轉換成8位ITU-R BT.656格式,或使用分立同步模塊使輸出格式為8位4:2:2。

模擬攝像頭進行視頻數據采集,TVP5154A將采集到的模擬數據進行數字化,然后送給DM648的視頻端口進行壓縮處理。4片TI公司生產的TVP5154A,與2個DM648的連接可組成16路的視頻采集,壓縮模塊如圖4所示(只給出了8路的連接圖)。

圖4中,TVP5154A的CH1_OUT,CH2_OUT,CH3_OUT,CH4_OUT口與1片DM648的VP0,VP1口直接連接,組成1個8路的視頻采集,壓縮模塊,用于數據的傳輸。DM648通過I2C總線對TVP5154A內部寄存器進行讀寫,達到控制該芯片的目的。

音頻輸入采集模塊由8個PCMl801U型音頻采集電路及其外圍電路組成,主要功能是對由拾音器采集輸入的模擬音頻信號進行采樣,然后將其轉換為DSP可以處理的數字音頻數據格式。PCMl801U是采用5V工作電壓的雙聲道16位音頻模/數(A/D)轉換器,包括1個單端-差分模擬前端、1個5階△一∑調制器(64倍重復取樣)、1個內部高通數字均分濾波器。

DM648有專門的McASP,與4個PCMl801U連接,實現音頻的輸入采集功能。用PCMl801U的左、右2個16位音頻聲道獲取4路音頻通道的數字化數據,音頻采集的數據格式為每路單聲道、44.1kHz采樣率,每個采樣數據用8位量化。采集輸出的數字音頻數據通過McASP傳給DSP的輸入緩沖區單元,當設定用于存放音頻采樣數據的緩存器已滿時產生DMA中斷,并在DMA中斷服務程序中根據實際設定情況處理音頻數據,經過實時編碼壓縮后的音頻數據存儲到外部SDRAM中。

本系統的主頻高達166MHz,屬于高頻系統,所以在進行PCB的設計時,必須進行抗高頻干擾的設計與處理。DM648作為高性能數字媒體處理器不僅內部具有很高的運行頻率,而且與外部的DDRAM的總線速度也達到266MHz或333MHz,如果外部的DDRAM由于布線原因達不到設計的希望速度,會降低系統的性能。此外由于100MHz以上的信號總線,存在信號完整性問題。為了保證信號的完整,在設計的時候采用了如下方法:

(1)對DDRAM的時鐘線,盡量走短線,而且到兩個DDRAM的長度盡量做到相等;

(2)FLASH等其他外設不要直接與數據和地址總線連接,而是通過緩沖芯片(如SN74LVT16245B)連接;

(3)高速總線上串入了小阻值電阻,阻值大小通過Protel軟件仿真得到,同時對線路進行了阻抗限制。

此外,由于DM648內部有PLL,對PLL外部所接器件,讓它們盡可能的靠近芯片,而且只放在了線路板的一面上。對于JTAG的連線長度不超過6英寸,如果超過6英寸長的加了驅動。本系統中既有模擬部分又有數字部分,所以在設計的時候,特別注意了模擬電源和數字電源的設計,盡量減少數字信號對模擬信號的干擾,否則對采集的視頻信號會有雪花、條紋,音頻信號產生噪聲等。對視頻、音頻芯片采用了單獨的電源芯片供電,模擬地和數字地通過單點或采用磁珠相連。

以上的抗高頻干擾方法的采用,使得整個系統在調試的過程中能夠順利的進行。

責任編輯:gt

-

處理器

+關注

關注

68文章

19259瀏覽量

229653 -

嵌入式

+關注

關注

5082文章

19104瀏覽量

304822 -

錄像機

+關注

關注

1文章

89瀏覽量

27846

發布評論請先 登錄

相關推薦

TMS320DM648 pdf datasheet

TMS320DM648 highest-performance fixed-point DSP generation

S3C2510A pdf,S3C2510A datashee

TMS320DM648-900,pdf(Digital Me

TMS320DM648-800,pdf(Digital Me

TMS320DM648-720,pdf(Digital Me

TMS320DM647, TMS320DM648 Digit

TMS320DM648-1100,pdf(Digital M

DSP芯片TMS320DM648數字信號處理器簡介

TMS320DM647和TMS320DM648數字媒體處理器英文原版資料詳細概述

TMS320DM648 TMS320DM648 Digital Media Processor

TMS320DM647/TMS320DM648數字媒體處理器數據表

從TMS320DM642遷移至TMS320DM648/DM6437

從TMS320DM642/3/1/0遷移到TMS320DM648/7器件

基于TMS320DM648和S3C2510A芯片實現16路嵌入式DVR系統的設計

基于TMS320DM648和S3C2510A芯片實現16路嵌入式DVR系統的設計

評論