前幾天,臨危受命,幫幾個初學者的學生寫一個簡易AM信號的FPGA實現(xiàn),以幫助他們搭建一個相對完整的系統(tǒng),測試他們的低速ADC,高速DAC,AGC控制等等模塊。本文的FPGA代碼已經(jīng)經(jīng)過上板測試,由于時間緊急沒有保存圖片,所以文章只有仿真圖片。

首先,為什么是AM信號的調(diào)制過程,是因為在短時間情況下,AM信號的實現(xiàn)相對簡單,而且上述提到的幾個模塊都可以得到使用和驗證。因為FPGA的價格因素,做課設/比賽使用最多的還是Altera的Cyclone系列板。所以,本文使用Quartus II 13.1 作為Verilog代碼綜合實現(xiàn)工具。AM信號調(diào)制過程就不做過多介紹了,簡單來說,就是基帶信號和一個直流信號相加,然后與載波相乘。那么,在實現(xiàn)過程中,做了些許改變,先讓基帶信號與載波相乘,然后將截位后的信號與載波相加。如果想要實現(xiàn)更精細的AM信號調(diào)制(變更調(diào)制深度等參數(shù)),可以修改這個地方的先后順序。AM公式表達如下:

為直流信號,是基帶信號,是載波信號。

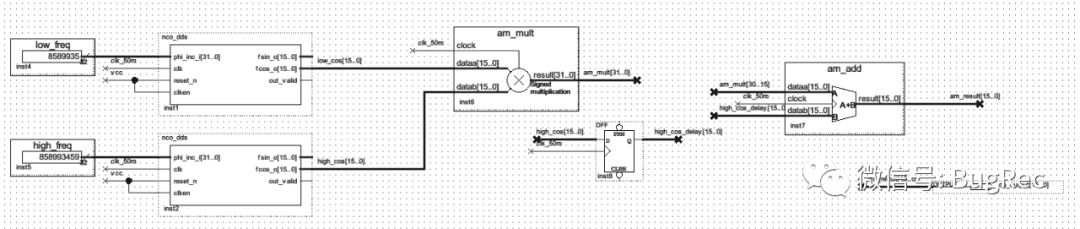

實現(xiàn)過程如上圖,頂層文件使用BSF文件,更為直觀。由上圖可以看出,基帶信號和載波信號是由NCO(DDS)產(chǎn)生,在上板驗證中,低頻部分的NCO被刪去,由低速ADC采樣外部信號替換這部分的低頻信號。所以在剛開始搭建模塊時,低速NCO輸出信號位寬就兼容了低速ADC的16位位寬。根據(jù)資料1可得,Altera提供的NCO是根據(jù)32位輸入信號phi_inc_i而輸出對應的頻率的正弦波。公式為:

是NCO預設輸出正弦波頻率,是輸入時鐘頻率,是NCO的相位精度。這里的設置是32位。NCO(DDS)的本質是ROM表,ROM表存儲著正弦波的波形數(shù)據(jù),相位精度代表波形數(shù)據(jù)的多少。根據(jù)phi_inc_i累加地址,ROM根據(jù)地址輸出波形數(shù)據(jù),最后數(shù)據(jù)計算如下。

基帶載波

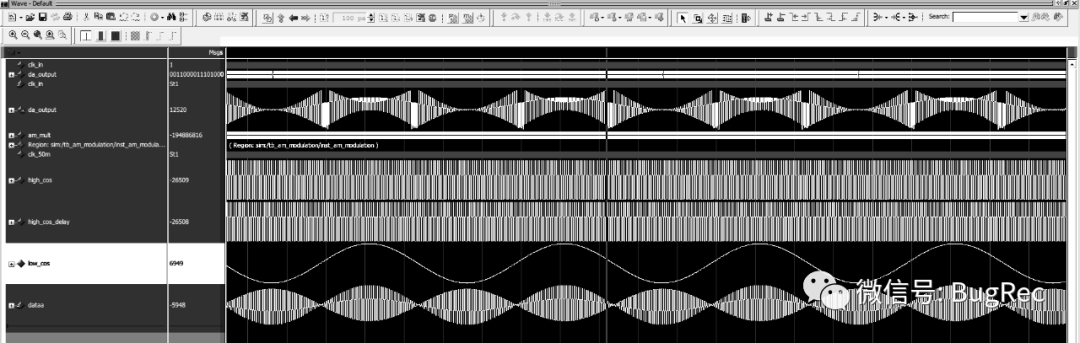

頻率(MHz)0.110

phi_inc_i8589935858993459

然后讓基帶和載波信號相乘,使用LPM_MULT IP核,設置好位寬,數(shù)據(jù)類型設為“signed”,設置流水線(增加clock),延遲設為1,便于后續(xù)通過時序檢查。相乘輸出信號位寬為32位,保險起見我們只截取最高位的符號位,再截取低位的數(shù)據(jù)。但是經(jīng)過上板測試和仿真,符號位實際上有很多位。當然,這部分可以將符號位進行優(yōu)化,或者設置一個模塊,根據(jù)輸入的參數(shù)輸出不一樣的截位信號,相當于在調(diào)整調(diào)制深度。同時,將載波信號延遲一個周期,與乘法器延遲一周期的信號做好時序對齊,然后經(jīng)過LPM_ADD_SUB IP核的加法運算;同樣,LPM_ADD_SUB IP核設置好輸入信號位寬,數(shù)據(jù)類型設為“signed”,設置流水線,延遲設為1。最后輸出的信號就可以經(jīng)過高速DAC輸出。整個調(diào)制過程就結束了。仿真結果:

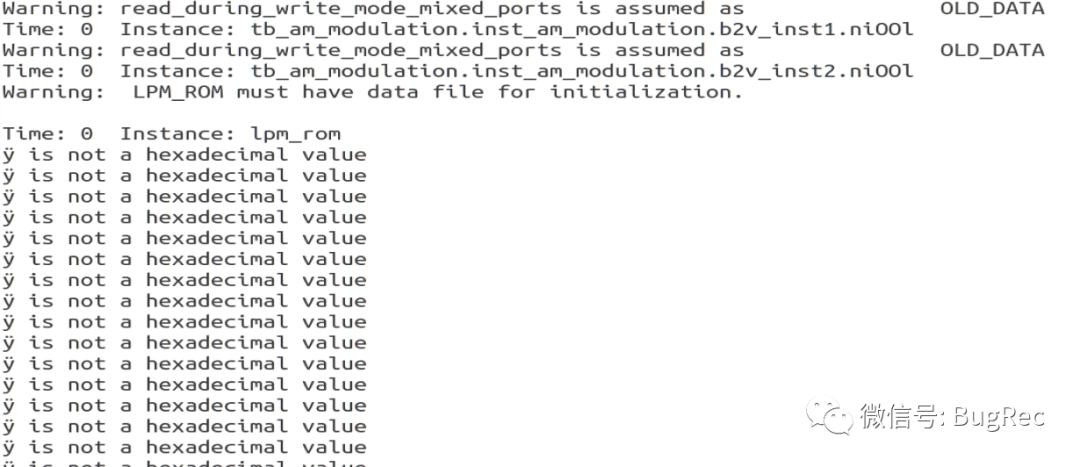

最后思考,可以在加法器和乘法器增加一個enable端口,IP核可以增加這個輸入信號;如果先加再乘,由于直流信號一般不會變動,使能信號可以等待每次低速ADC或低速NCO數(shù)值更新再拉高一次;乘法器也可以使用使能信號控制,這樣的話性能可能沒有變化,功耗或許可降低些。此外,使用VCS仿真NCO的nco.vo文件時,一直遇到一個問題,報錯如下:

大概是說NCO生成的4個hex文件有問題,但是使用modelsim就沒這個問題了。

原文標題:簡易AM信號調(diào)制的FPGA實現(xiàn)過程簡單講解

文章出處:【微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

責任編輯:haq

-

FPGA

+關注

關注

1629文章

21729瀏覽量

603016 -

加速器

+關注

關注

2文章

797瀏覽量

37840

原文標題:簡易AM信號調(diào)制的FPGA實現(xiàn)過程簡單講解

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

相關推薦

使用FPGA構建ADAS系統(tǒng)簡易過程

如何實現(xiàn)FPGA的IO輸出脈沖信號放大?

如何用FPGA實現(xiàn)一個通信系統(tǒng)的發(fā)射端接收機?

用AD630做了一個簡易的鎖相放大器,如何才算成功的把信號提取出來?

AM243x/AM64x單芯片伺服電機控制實現(xiàn)和基準測試

如何寫一個簡易AM信號的FPGA實現(xiàn)?

如何寫一個簡易AM信號的FPGA實現(xiàn)?

評論