據(jù)稱,該GPU計劃是迄今為止最大,設計最多的芯片:將具有1000個執(zhí)行單元(EU),內(nèi)核數(shù)量超過8000個,采用了7種關(guān)鍵技術(shù),包含47個Tile,是有史以來尺寸最大、最復雜的GPU。

英特爾新GPU:Foveros 3D封裝不同代工廠Tile

英特爾的Ponte Vecchio GPU集成了超過1000億個晶體管,47顆XPU Tile以及各種制程節(jié)點的混搭。這款GPU采用了Xe-HPC圖形架構(gòu),該架構(gòu)是基于英特爾7nm EUV節(jié)點的旗艦產(chǎn)品。

除此之外,該芯片還有大量基于不同工藝節(jié)點的Tile,其中一些Xe-HPC Tile由臺積電等外部晶圓代工廠生產(chǎn)。

目前,尚無法確定英特爾是否會采用臺積電的7nm或7nm+ EUV工藝節(jié)點,但是鑒于臺積電代工的Xe Link I/O Tile采用了標準的非EUV 7nm工藝,英特爾可能會繼續(xù)采用標準7nm工藝。

英特爾首席架構(gòu)師Raja Koduri曾經(jīng)說Ponte Vecchio GPU采用了7項先進技術(shù),技術(shù)媒體Wccftech給出了具體名單:

英特爾7nm工藝、臺積電7nm工藝、Foveros 3D封裝、EMIB(嵌入式多芯片互連橋接)技術(shù)、英特爾增強型10nm SuperFin工藝、Rambo Cache(蘭博緩存)與HBM2顯存。

Raja Koduri也在推特上公布了47顆Tile分別是什么:16顆Xe HPC(internal/external)、8顆Rambo(internal、2顆Xe Base(internal)、11顆EMIB(internal)、2顆Xe Link(external)和8顆HBM(external)。

Ponte Vecchio實際上由兩個獨立GPU芯片組成,每個GPU包含六個Xe-HPC計算單元。

一對Xe-HPC計算單元直接與蘭博緩存相連,蘭博緩存采用了英特爾增強型10nm SuperFin工藝。

每個GPU還連接了四個HBM2顯存,HBM2采用4Hi或8Hi堆疊(可以簡單理解為4層或8層)。一共八個HBM2可以提供多GB的內(nèi)存容量和帶寬負載。此外,每個GPU上還有8個Passive Die Stiffeners。

總體來說,英特爾Xe HPC這款MCM結(jié)構(gòu)GPU處理器使用了最先進的Foveros 3D封裝技術(shù),將多個來自不同代工廠,使用不同工藝制作的Tile集成在一個平臺上,EMIB技術(shù)則將HBM2、Xe Link I/O等Tile與GPU互連。

所有這些整合形成了Ponte Vecchio Xe-HPC GPU。

執(zhí)行單元數(shù)量將超1000,提供40倍雙精度浮點算術(shù)能力

英特爾此前曾介紹過,其Xe-HPC GPU將具有1000個執(zhí)行單元(EU)。到目前為止,Xe LP有96個EU,它們構(gòu)成了總共768個內(nèi)核。

新GPU的每個子層(subslice)有8個EU。第12代GPU中的subslice類似于英偉達SM單元或AMD的CU單元。

而在英特爾的9.5和11代GPU上,每個subslice具有8個EU,因此如果12代保持相同的層次結(jié)構(gòu),人們將能看到大量由subslice組成的超級切片。從目前的圖片上看,英特爾第12代GPU將有8個算術(shù)邏輯單元(ALU),與11代和9.5代保持一致。

大致來說,一個GPU芯片將有1000個EU單元,8000個內(nèi)核,而實際內(nèi)核數(shù)量還要更多。而Xe HP GPU的HPC尺寸也將更大。

Wccftech列出了英特爾GPU的實際EU單元、對內(nèi)核數(shù)量的估計。功率和TFLOPS(每秒浮點運算次數(shù))等數(shù)據(jù):

英特爾Xe HP (12.5) 2-Tile GPU: 1024個EU單元,8192個內(nèi)核,20.48 TFLOPS,1.25 GHz,300W;

英特爾Xe HP (12.5) 4-Tile GPU: 2048個EU單元,16384個內(nèi)核,36 TFLOPS,1.1 GHz,400W-500W。

英特爾Xe類GPU具有下面幾種可變矢量寬度(vector width):SIMT(GPU)、SIMD(CPU)、SIMT+SIMD(最高性能)。

Raja Koduri談到,英特爾的Xe HPC GPU能夠擴展到1000個EU,EU通過幾個高帶寬內(nèi)存通道與XE內(nèi)存結(jié)構(gòu)相連,并且每個EU單元都進行了升級,可以提供40倍的雙精度浮點計算能力。

蘭博緩存則將在整個雙精度工作負載中提供可持續(xù)的FP64計算性能。

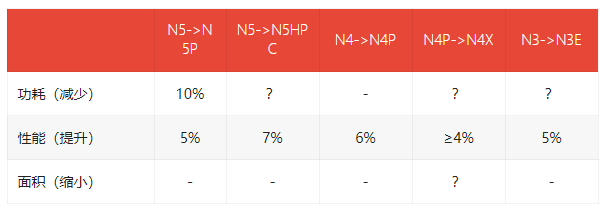

就工藝優(yōu)化而言,以下是英特爾針對7納米工藝節(jié)點的一些關(guān)鍵改進:

1、相較10nm節(jié)點具有兩倍的密度縮放優(yōu)勢;

2、內(nèi)部的節(jié)點優(yōu)化;

3、DR(Design Rules)的4倍縮減;

4、采用了EUV光刻技術(shù);

5、新一代Foveros和EMIB封裝。

責任編輯:pj

-

芯片

+關(guān)注

關(guān)注

456文章

50886瀏覽量

424167 -

英特爾

+關(guān)注

關(guān)注

61文章

9978瀏覽量

171856 -

晶圓

+關(guān)注

關(guān)注

52文章

4922瀏覽量

128046 -

gpu

+關(guān)注

關(guān)注

28文章

4743瀏覽量

128992

發(fā)布評論請先 登錄

相關(guān)推薦

英特爾換帥 英特爾CEO Pat Gelsinger(帕特·基辛格)正式退休

英特爾向聯(lián)想交付首款18A工藝CPU樣品

英特爾開啟新時代:Intel 3制程節(jié)點引領性能與能效飛躍

英特爾推進面向未來節(jié)點的技術(shù)創(chuàng)新,在2025年后鞏固制程領先性

英特爾正在順利推進的Intel 20A和Intel 18A兩個節(jié)點

BittWare提供基于英特爾Agilex? 7 FPGA最新加速板

英特爾Clearwater Forest系列突破高核心數(shù)服務器CPU

英特爾押注18A制程,力爭重回技術(shù)領先地位

英特爾18A工藝節(jié)點推廣激勵措施承諾

英特爾發(fā)力18A工藝節(jié)點,力圖超越三星躍升全球第二大晶圓代工廠

英特爾宣布推進1.4納米制程

英特爾:未來節(jié)點演進版性能提升預計不超過10%

英特爾針對7納米工藝節(jié)點做出哪些關(guān)鍵改進?

英特爾針對7納米工藝節(jié)點做出哪些關(guān)鍵改進?

評論