摘 要: 設(shè)計(jì)了一種基于EPF10KRC208-4的誤碼儀,該設(shè)計(jì)充分利用了FPGA強(qiáng)大的可編程能力和豐富的資源,以及軟件開(kāi)發(fā)平臺(tái)Quartus Ⅱ的完備功能,具有體積小巧、攜帶方便、測(cè)量精確等優(yōu)點(diǎn)。其核心部分分別采用了逐位比較法和移位寄存器法,并在仿真過(guò)程中設(shè)置了多種誤碼情況進(jìn)行對(duì)比。最后,根據(jù)仿真結(jié)果分析了方案的可行性和兩種方法的優(yōu)缺點(diǎn)。

自20世紀(jì)下半葉以來(lái),信息技術(shù)的飛速發(fā)展在軍事領(lǐng)域掀起了軍事變革的浪潮,使武器裝備、作戰(zhàn)模式和作戰(zhàn)理論的本質(zhì)發(fā)生了深刻變化。信息技術(shù)促進(jìn)了衛(wèi)星通信、光纖通信等現(xiàn)代通信手段與現(xiàn)代偵查監(jiān)視系統(tǒng)、計(jì)算機(jī)網(wǎng)絡(luò)和武器控制的結(jié)合,實(shí)現(xiàn)了情報(bào)、通信、指揮與控制一體化的情報(bào)指揮控制系統(tǒng)(C3I系統(tǒng))正改變著傳統(tǒng)的作戰(zhàn)模式,使戰(zhàn)爭(zhēng)形態(tài)由機(jī)械化戰(zhàn)爭(zhēng)轉(zhuǎn)變?yōu)樾畔⒒瘧?zhàn)爭(zhēng)。

隨著通信技術(shù)的不斷發(fā)展,數(shù)字通信正在逐步取代模擬通信成為主要的通信方式。而誤碼是影響數(shù)字通信系統(tǒng)最重要的因素,因?yàn)檎`碼直接破壞了信息傳遞的正確性。然而在信息化戰(zhàn)場(chǎng)上,存在各種各樣復(fù)雜的干擾,人為干擾如雷達(dá)波、各種電器開(kāi)關(guān)通斷產(chǎn)生的短脈沖等的電磁波,敵方的電子干擾、各種干擾彈、機(jī)動(dòng)馬達(dá)和炮擊爆炸等電磁輻射,還有非人為的雷電、宇宙輻射、鄰近通信系統(tǒng)等的干擾,這些干擾往往是導(dǎo)致信道產(chǎn)生誤碼的最重要因素。

為了正確地評(píng)估戰(zhàn)場(chǎng)環(huán)境下通信系統(tǒng)的性能,本文研究了基于FPGA的誤碼儀設(shè)計(jì),采用FPGA使設(shè)計(jì)具有結(jié)構(gòu)小巧,攜帶方便等優(yōu)點(diǎn),其核心部分的設(shè)計(jì)分別采用了逐位比較法和移位寄存器法。

1 基本原理

設(shè)計(jì)過(guò)程中FPGA開(kāi)發(fā)環(huán)境采用Altera公司的開(kāi)發(fā)軟件Quartus Ⅱ 9.0,它集成邏輯分析、功率分析、時(shí)序優(yōu)化和EDA工具等功能,使設(shè)計(jì)變得十分簡(jiǎn)潔。

1.1 逐位比較法的基本原理

逐位比較法誤碼儀示意圖如圖1所示,誤碼儀由發(fā)送和接收兩部分組成[3]。發(fā)送部分由碼型發(fā)生器組成,Select為測(cè)試碼類型選擇輸入,接收部分由時(shí)鐘同步器、本地碼產(chǎn)生器、逐位比較器和誤碼統(tǒng)計(jì)模塊組成。

其原理為:在低頻時(shí)鐘CLK1的驅(qū)動(dòng)下,將碼型發(fā)生器生成的測(cè)試碼m序列輸入到被測(cè)信道,然后由接收端接收,并提取時(shí)鐘同步器進(jìn)行時(shí)鐘同步。在8倍高頻時(shí)鐘CLK8的驅(qū)動(dòng)下,提取數(shù)據(jù)流的時(shí)鐘信號(hào)。時(shí)鐘同步完成后,位同步器輸出頻率同CLK1的同步時(shí)鐘CLK一致,其上升沿對(duì)準(zhǔn)接收數(shù)據(jù)的中間部分,以保證接收數(shù)據(jù)的正確性。

m序列經(jīng)過(guò)被測(cè)信道后,進(jìn)入接收端的本地碼產(chǎn)生器和逐位比較器。接收端把接收到的m序列前N個(gè)碼元(N為m序列發(fā)生器級(jí)數(shù))對(duì)本地碼產(chǎn)生器進(jìn)行灌碼,并把所灌碼作為本地產(chǎn)生器的初值。本地碼產(chǎn)生器的結(jié)構(gòu)與發(fā)送端的碼型發(fā)生器結(jié)構(gòu)相同,因此,如果所灌碼正確,就可以產(chǎn)生與發(fā)送端完全一致的m序列,該序列與接收到的數(shù)據(jù)在逐位比較器中進(jìn)行逐位比較。

如果測(cè)試數(shù)據(jù)在傳輸中有誤碼,則在逐位比較過(guò)程中可以檢測(cè)出來(lái)。逐位比較器將檢測(cè)到的誤碼信號(hào)傳輸給誤碼統(tǒng)計(jì)模塊,該模塊的功能是進(jìn)行誤碼數(shù)累計(jì),累計(jì)的數(shù)據(jù)傳送給計(jì)算顯示模塊。當(dāng)一段時(shí)間內(nèi)誤碼數(shù)量超過(guò)所設(shè)上限,則該模塊給出失步信號(hào)LostSyn,說(shuō)明此時(shí)系統(tǒng)失步,統(tǒng)計(jì)的誤碼數(shù)據(jù)無(wú)效,需重新同步。失步信號(hào)LostSyn使本地碼產(chǎn)生器重新進(jìn)行灌碼,并產(chǎn)生新的本地序列。后續(xù)步驟同上。

1.2 移位寄存器法的基本原理

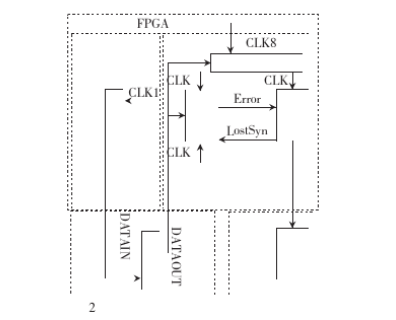

移位寄存器法誤碼儀的示意圖如圖2所示,誤碼儀的設(shè)計(jì)也包括發(fā)送部分和接收部分。發(fā)送部分由碼型發(fā)生器組成,接收部分由時(shí)鐘同步器、誤碼檢測(cè)器和誤碼統(tǒng)計(jì)模塊組成。碼型發(fā)生器與上一種方法工作方式不同,在同一次測(cè)試中要先后產(chǎn)生兩種碼型,先產(chǎn)生時(shí)鐘同步碼,再產(chǎn)生m序列。時(shí)鐘同步碼只用于接收端時(shí)鐘提取,時(shí)鐘同步器工作原理與第一種方法相同。時(shí)鐘同步后時(shí)鐘同步器發(fā)出Syn信號(hào)通知碼型發(fā)生器產(chǎn)生m序列,這樣可以避免測(cè)試數(shù)據(jù)的丟失,保證誤碼檢測(cè)的正確性。

該方法的最大特點(diǎn)是用一個(gè)誤碼檢測(cè)器代替了上一種方法的本地碼產(chǎn)生器和逐位比較器。當(dāng)時(shí)鐘同步后,m序列經(jīng)過(guò)被測(cè)信道直接進(jìn)入接收端的誤碼檢測(cè)模塊進(jìn)行誤碼檢測(cè),而不需要再產(chǎn)生本地碼,這種設(shè)計(jì)方法的優(yōu)點(diǎn)是抗干擾能力更強(qiáng),設(shè)計(jì)也簡(jiǎn)單;缺點(diǎn)是占用FPGA資源多,耗用83%的邏輯單元,設(shè)計(jì)多種碼型時(shí)占用資源更是明顯增多。而逐位比較法對(duì)FPGA資源要求不高,僅占13%的邏輯單元,容易實(shí)現(xiàn)多種碼型測(cè)試。誤碼統(tǒng)計(jì)模塊的工作原理與前一種方法相同。

2 設(shè)計(jì)方法

2.1 逐位比較法的設(shè)計(jì)方法

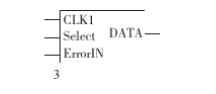

碼型發(fā)生器模型圖如圖3所示,其核心為m序列發(fā)生器。其中,CLK1為產(chǎn)生測(cè)試數(shù)據(jù)的基準(zhǔn)時(shí)鐘;Select為碼型選擇輸入端,在這里設(shè)計(jì)了兩種碼型,通過(guò)控制Select端狀態(tài)來(lái)實(shí)現(xiàn)測(cè)試碼型的切換;ErrorIN為手動(dòng)誤碼輸入端,該端連接一個(gè)按鈕,按一次按鈕產(chǎn)生一個(gè)誤碼;DATA為數(shù)據(jù)輸出端口。

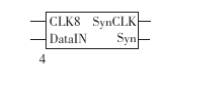

圖4為時(shí)鐘同步器模型,其核心為一個(gè)抽樣電路。CLK8為8倍高頻時(shí)鐘輸入端,DataIN為數(shù)據(jù)輸入端,SynCLK為同步時(shí)鐘輸出端,Syn為時(shí)鐘同步標(biāo)志位。設(shè)計(jì)的方法為:數(shù)據(jù)輸入端DataIN作為抽樣電路的控制端,高電平時(shí)抽樣電路工作,在一個(gè)周期內(nèi)抽樣電路需進(jìn)行3點(diǎn)抽樣,當(dāng)輸入數(shù)據(jù)的寬度無(wú)法滿足3點(diǎn)抽樣時(shí),視為干擾,繼續(xù)進(jìn)行時(shí)鐘同步搜索。當(dāng)3點(diǎn)抽樣皆為高電平時(shí),才視為正常數(shù)據(jù),使該模塊輸出同步時(shí)鐘和時(shí)鐘同步標(biāo)志位。該同步時(shí)鐘作為接收端后續(xù)電路的時(shí)鐘信號(hào)。

圖5為本地碼產(chǎn)生模塊模型圖,其核心為灌碼電路設(shè)計(jì)和m序列發(fā)生器。CLK為時(shí)鐘輸入端(后續(xù)模塊相同),DataIN為數(shù)據(jù)輸入端,Reset為復(fù)位端,DATA為本地碼輸出端。灌碼電路設(shè)計(jì)的關(guān)鍵是,在進(jìn)行灌碼時(shí),將m序列發(fā)生器(最長(zhǎng)線型反饋移位寄存器)的循環(huán)回路斷開(kāi),使其成線性移位寄存器;當(dāng)灌碼完成后,將m序列發(fā)生器循環(huán)回路接通,此后,DataIN輸入的數(shù)據(jù)無(wú)效,即可按照所灌初值自行產(chǎn)生m序列。當(dāng)出現(xiàn)失步或者手動(dòng)復(fù)位時(shí),復(fù)位信號(hào)從Reset端輸入使該模塊重新進(jìn)行灌碼操作。

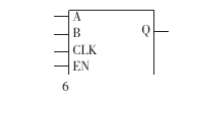

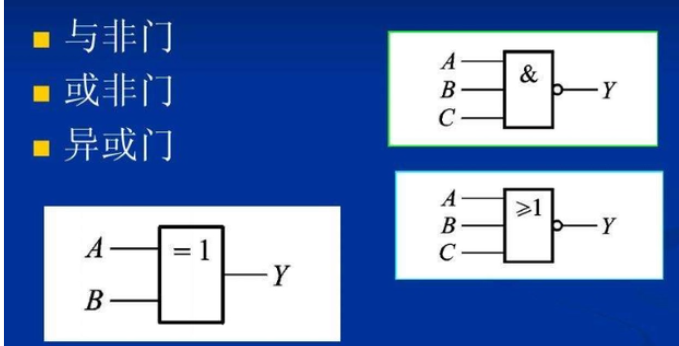

圖6所示為逐位比較器模型圖,其核心為一個(gè)異或門和相應(yīng)的時(shí)延電路。其中A為本地碼輸入端;B為接收數(shù)據(jù)的輸入端,其在內(nèi)部需要經(jīng)過(guò)一定的時(shí)延,再跟A端數(shù)據(jù)接到異或門;EN為使能端。若出現(xiàn)誤碼,則在某時(shí)刻B端的碼元跟A端的碼元相異,經(jīng)過(guò)異或門后輸出一個(gè)高電平,其他相同的碼元經(jīng)過(guò)異或運(yùn)算后輸出為低電平,這樣就能判別誤碼的情況了。Q即為誤碼輸出端,高電平表示有誤碼,一個(gè)時(shí)鐘的高電平表示有一個(gè)誤碼。

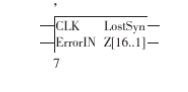

圖7為誤碼統(tǒng)計(jì)模塊模型圖,其核心為高電平到窄脈沖的轉(zhuǎn)換電路和誤碼計(jì)數(shù)電路。其中ErrorIN為誤碼信號(hào)輸入端,其在內(nèi)部經(jīng)過(guò)轉(zhuǎn)換電路轉(zhuǎn)換為窄脈沖信號(hào);LostSyn為失步信號(hào)輸出端;Z[16..1]為誤碼統(tǒng)計(jì)數(shù)據(jù)輸出端。在給定時(shí)間內(nèi)誤碼數(shù)量達(dá)到上限,則給出失步信號(hào)。失步信號(hào)通過(guò)一個(gè)8位計(jì)數(shù)器給出,該計(jì)數(shù)器8位輸出連接到一個(gè)8位與非門,通過(guò)改變連接方法可以設(shè)置0~255的任何一個(gè)定時(shí)值。另外,在其內(nèi)部設(shè)計(jì)一個(gè)清零電路,清零周期即為所設(shè)時(shí)間段,每個(gè)周期結(jié)束時(shí)的一個(gè)時(shí)鐘清零電平將計(jì)數(shù)器清零,以保證每個(gè)周期從零計(jì)數(shù)。誤碼數(shù)據(jù)統(tǒng)計(jì)器為16位計(jì)數(shù)器。

2.2 移位寄存器法的設(shè)計(jì)方法

移位寄存器法的時(shí)鐘同步器和誤碼統(tǒng)計(jì)模塊的設(shè)計(jì)方法與上一種方法相同。下面僅介紹一下碼型發(fā)生器和誤碼檢測(cè)器的設(shè)計(jì)。

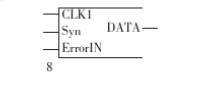

圖8為碼型發(fā)生器模型圖,其核心為m序列發(fā)生器和方波發(fā)生器。其模型圖跟逐位比較法的不同之處在于輸入端沒(méi)有Select端,而有Syn端。Syn信號(hào)來(lái)自時(shí)鐘同步器的同步標(biāo)志位Syn。該輸入通過(guò)控制一個(gè)開(kāi)關(guān)電路來(lái)達(dá)到切換方波發(fā)生器和m序列發(fā)生器的目的。由于移位寄存器設(shè)計(jì)方法耗用資源多,不適合設(shè)計(jì)多種碼型,這里僅設(shè)計(jì)了一種m序列發(fā)生器,所以沒(méi)有Select端。當(dāng)然,如果不考慮成本,也可以設(shè)計(jì)多種碼型。

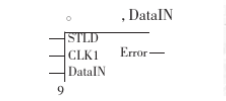

圖9為誤碼檢測(cè)器模型圖,其核心為一個(gè)串入并出移位寄存器和一個(gè)并入串出移位寄存器。其中,DataIN為數(shù)據(jù)輸入端,STLD為并入串出移位寄存器的移位加載端,Error為誤碼輸出端。

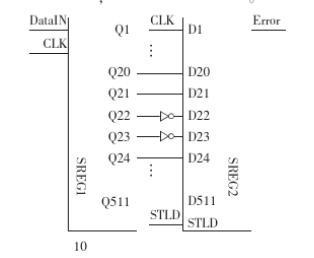

圖10為誤碼檢測(cè)器設(shè)計(jì)思路示意圖。m序列每一周期的排列規(guī)則是固定不變的,即每個(gè)周期中的對(duì)應(yīng)位都是相同的。移位寄存器法就是利用了這種周期性。假設(shè)該方法設(shè)計(jì)的碼型為511碼,又設(shè)每個(gè)周期的第20~24位的排列是“11001”,則移位寄存器對(duì)應(yīng)位設(shè)計(jì)如圖10所示。按照這種設(shè)計(jì)方法,當(dāng)一個(gè)周期的511個(gè)碼元正好出現(xiàn)在SREG1的輸出端口上時(shí),如果傳輸?shù)拇a元無(wú)誤碼,則SREG2的輸入端口全是低電平,否則,對(duì)應(yīng)的高電平即為誤碼,此時(shí)給STLD端口一個(gè)低電平,則將SREG1的511個(gè)輸出數(shù)據(jù)經(jīng)過(guò)上述處理后加載到SREG2。SREG2在CLK的驅(qū)動(dòng)下,將加載進(jìn)來(lái)的數(shù)據(jù)從Error端口串行輸出,高電平即代表誤碼。

3 仿真分析

下面利用Quartus Ⅱ開(kāi)發(fā)平臺(tái)對(duì)上述兩種方法在給定多種條件下進(jìn)行時(shí)序仿真,并進(jìn)行分析。

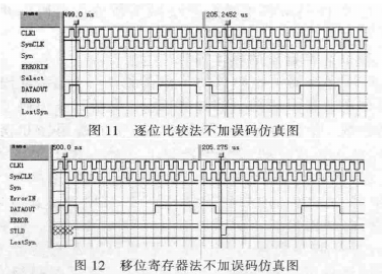

圖11、圖12所示是在沒(méi)有手動(dòng)加入誤碼的情況下(即ErrorIN為低電平)兩種方法的仿真截圖,所用碼型皆為511碼,所用時(shí)鐘頻率相同,分別在兩個(gè)不同的時(shí)間段進(jìn)行了截取。從圖11、圖12可以看出,逐位比較法在時(shí)間t=499.0 ns處完成了時(shí)鐘同步,移位寄存器法在時(shí)間t=500 ns處完成了時(shí)鐘同步,在所給時(shí)間段內(nèi),兩種方法的誤碼輸出皆為低電平。對(duì)于移位寄存器法,在時(shí)間t=205.275 ?滋s處移位加載端STLD加載有效,把一個(gè)周期的511個(gè)碼元經(jīng)過(guò)處理后同時(shí)加載到SREG2,此后每隔一個(gè)周期就給出一個(gè)加載有效信號(hào)。

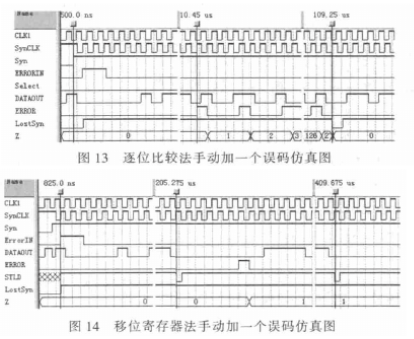

圖13、圖14所示是手動(dòng)加了一個(gè)誤碼的情況下兩種方法的仿真截圖,碼型和頻率同前,分別在3個(gè)不同時(shí)間段進(jìn)行了截取。由圖13、圖14可以看出,在時(shí)鐘同步之后,ErrorIN有一段高電平,此操作即給測(cè)試碼手動(dòng)加入了一個(gè)誤碼。在此必須注意,加入的誤碼是落在測(cè)試碼的前9個(gè)碼元之內(nèi)的。對(duì)于逐位比較法,這種誤碼將會(huì)使逐位比較法灌碼碼元出現(xiàn)誤碼。如圖13所示,在時(shí)間t=10.45 ?滋s之后連續(xù)出現(xiàn)了誤碼,直到t=108.85 ?滋s誤碼數(shù)在設(shè)定時(shí)間內(nèi)達(dá)到了上限,系統(tǒng)判斷為失步并給出LostSyn信號(hào)后,又重新進(jìn)行灌碼等一序列操作,才使誤碼數(shù)歸零,繼續(xù)進(jìn)行測(cè)試。而逐位比較法則可以正確地檢測(cè)出誤碼。

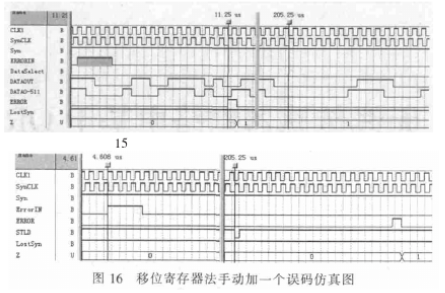

圖15、圖16也是手動(dòng)加了一個(gè)誤碼的情況下兩種方法的仿真截圖,截取了兩個(gè)時(shí)間段。與前一仿真相比,所給條件唯一不同就是加入的誤碼落在測(cè)試碼的前9個(gè)碼元之外,即逐位比較法首次灌碼碼元正確。由圖15、16中可以看出,在給定條件下,兩種方法都沒(méi)有出現(xiàn)失步現(xiàn)象,而且都能正確檢測(cè)出誤碼信息。結(jié)果說(shuō)明,逐位比較法能否正確檢測(cè)出誤碼,取決于所灌碼元正確與否,也即抗干擾能力差,如果出現(xiàn)連續(xù)的灌碼碼元誤碼,則也會(huì)連續(xù)出現(xiàn)失步現(xiàn)象。而移位寄存器法不會(huì)出現(xiàn)這個(gè)問(wèn)題。

通過(guò)對(duì)誤碼儀兩種實(shí)現(xiàn)方法的設(shè)計(jì)、仿真與分析可以看出,逐位比較法耗用邏輯單元少,擴(kuò)展性能也好,適合設(shè)計(jì)多種PN碼的測(cè)試。但它的抗干擾能力也相對(duì)較差,一旦灌碼碼元出現(xiàn)誤碼,則后續(xù)測(cè)試會(huì)出現(xiàn)一連串誤碼,導(dǎo)致測(cè)試結(jié)果錯(cuò)誤,直到系統(tǒng)判斷為失步,才能再次進(jìn)行灌碼操作,重新測(cè)試。而移位寄存器法的抗干擾能力好,但耗用資源多,不適合多種PN碼測(cè)試的設(shè)計(jì)。結(jié)果表明,兩種方法都是可行的,但各有優(yōu)缺點(diǎn),在實(shí)踐中可以根據(jù)實(shí)際需求進(jìn)行選擇。

參考文獻(xiàn)

[1] 樊昌信,曹麗娜。通信原理(第六版)[M]。北京:國(guó)防工業(yè)出版社,2006.

[2] 褚振勇,齊亮,田紅心,等.FPGA設(shè)計(jì)及應(yīng)用[M]。西安:西安電子科技大學(xué),2006.

[3] 李斌。基于FPGA的誤碼儀的研究與設(shè)計(jì)[D]。武漢:武漢理工大學(xué),2006.

[4] 吳繼華,王誠(chéng).Altera FPGA/CPLD設(shè)計(jì)(初級(jí)篇)[M]。北京:人民郵電出版社,2005.

編輯:jq

-

FPGA

+關(guān)注

關(guān)注

1629文章

21729瀏覽量

603010 -

EDA工具

+關(guān)注

關(guān)注

4文章

267瀏覽量

31787 -

開(kāi)發(fā)軟件

+關(guān)注

關(guān)注

1文章

25瀏覽量

12927

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

ADS1292R有 \"1 ch ECG + 1 ch呼吸偵測(cè)\" 或 \"2 ch ECG\" 兩種模式,是否可以在產(chǎn)品上實(shí)現(xiàn)自行切換兩種使用模式?

Linux應(yīng)用層控制外設(shè)的兩種不同的方式

比較分析兩種不同的可提高柵極驅(qū)動(dòng)電流的方法

晶閘管的阻斷狀態(tài)有兩種是什么

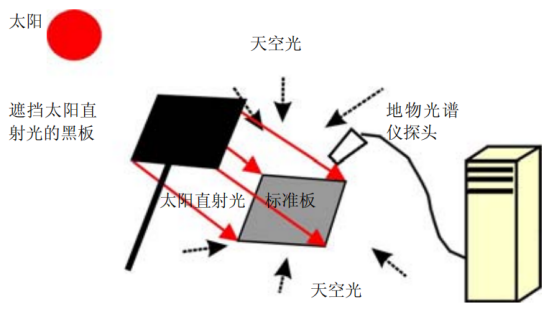

地物光譜儀的兩種天空光測(cè)量方法比較

wdm設(shè)備的兩種傳輸方式

控制器有哪兩種實(shí)現(xiàn)方式?各有何優(yōu)缺點(diǎn)?

GYFTA、GYFTY兩種光纜的區(qū)別

兩種簡(jiǎn)單、精確、靈活的熱電偶溫度測(cè)量方法

異或門兩種常見(jiàn)的實(shí)現(xiàn)方式

OpenCV兩種不同方法實(shí)現(xiàn)粘連大米分割計(jì)數(shù)

什么是浪涌電流,關(guān)于浪涌抑制的兩種方案

一種關(guān)于FPGA的兩種誤碼儀實(shí)現(xiàn)方法設(shè)計(jì)

一種關(guān)于FPGA的兩種誤碼儀實(shí)現(xiàn)方法設(shè)計(jì)

評(píng)論