從2019年開始,晶圓廠就開始有限度地將極紫外線(EUV)光刻技術(shù)用于芯片的大批量制造(HVM)。在當(dāng)時(shí),ASML的Twinscan NXE系列光刻機(jī)能夠滿足客戶的基本生產(chǎn)需求,然而整個(gè)EUV生態(tài)系統(tǒng)卻還沒做好所有的準(zhǔn)備,其中影響EUV的因素之一就是缺少用于光掩模的防護(hù)膜(protective pellicles for photomasks),這限制了EUV工具的使用并影響了產(chǎn)量。

幸運(yùn)的是,由于最近推出了可用于生產(chǎn)的EUV防護(hù)膜,因此防護(hù)膜的狀況終于得到了改善,而且情況有望在未來幾年得到改善。

近年來,憑借其Twinscan NXE EUV光刻工具取得了長(zhǎng)足進(jìn)步,ASML改善了EUV光刻機(jī)的光源性能,可用性時(shí)間和生產(chǎn)率。其業(yè)界同行也做了很多工作,以使使用EUV設(shè)備的大批量制造(HVM)成為可能。盡管如此,EUV生態(tài)系統(tǒng)仍需要進(jìn)一步發(fā)展。半導(dǎo)體供應(yīng)鏈面臨EUV的最臭名昭著的挑戰(zhàn)之一就是防護(hù)膜(pellicles)的開發(fā),在兩年前,這種防護(hù)木(pellicles)還沒有面世,這也就是為什么TSMC和Samsung Foundry必須發(fā)明如何使用沒有保護(hù)膜的EUV掃描儀的方法。

薄膜(Pellicle)通過將其與可能落在其表面上的顆粒隔離開,從而在芯片生產(chǎn)流程中保護(hù)6×6英寸光掩模(掩模版),否則在這個(gè)過程中可能會(huì)損壞它們或在生產(chǎn)中給晶圓造成缺陷。每個(gè)EUV工具的reticle要花費(fèi)30萬(wàn)美元,因此芯片制造商迫切希望能找到新的方法保護(hù)它們的晶圓免受微粒甚至EUV輻射本身的損害,因?yàn)檫@樣可以降低成本。同時(shí),降低與收益率相關(guān)的風(fēng)險(xiǎn)也許更為重要。

與此同時(shí),對(duì)薄膜(pellicles)的需求則根據(jù)制造商和所用光掩模的類型而有所不同。英特爾以其大的CPU裸片而聞名,它傾向于使用單裸片,這意味著粒子引入的僅一個(gè)掩模缺陷會(huì)自動(dòng)殺死整個(gè)裸片。同時(shí),如果使用25個(gè)die的光掩模,粒子加法器將“僅”導(dǎo)致產(chǎn)率降低4%(一個(gè)死die),這就是為什么對(duì)于較小的芯片和多die的光掩模,無(wú)需使用防護(hù)膜(pellicles)即可擺脫困境的原因。

在得知沒有人能夠保證超復(fù)雜的EUV掃描儀100%不含有害顆粒后,該行業(yè)開始為EUV工具開發(fā)保護(hù)膜,這是相對(duì)較晚的時(shí)間,這就是為什么它們?cè)?019年尚未準(zhǔn)備就緒的原因。

與深紫外線(DUV)光刻設(shè)備一起使用的光掩模膜盒是常見且便宜的。相比之下,由于EUV的光掩模與DUV的光掩模不同(EUV掩模本質(zhì)上是250到350nm厚的堆疊,在基板上具有40到50個(gè)交替的硅和鉬交替層),因此這種標(biāo)線的防護(hù)膜也大不相同。特別是,極紫外光的波長(zhǎng)非常短,這意味著其防護(hù)膜有許多要求,使其不易生產(chǎn)且價(jià)格昂貴。EUV防護(hù)膜必須非常薄,不應(yīng)影響掩模版的反射特性,應(yīng)具有較高的透射率(透射率越高,掃描儀的生產(chǎn)率越高),應(yīng)維持較高的EUV功率水平并承受極端溫度(從600oC至1,000oC的未來)。

IMEC的Emily Gallagher說:“大多數(shù)材料在13.5nm EUV波長(zhǎng)上都具有非常強(qiáng)的吸收能力,即使選擇了大多數(shù)EUV透明材料,其膜也必須非常薄才能達(dá)到90%的透射率。”“這種薄膜通常不能保持足夠的強(qiáng)度,無(wú)法在所需的尺寸下獨(dú)立放置。此外,EUV掃描儀的環(huán)境與許多材料不兼容,會(huì)使防護(hù)膜經(jīng)受抽氣—排氣循環(huán)的作用。”

根據(jù)SemiEngineering的說法,迄今為止,已經(jīng)出現(xiàn)了許多EUV防護(hù)膜選項(xiàng)包括:

ASML于2019年推出了首款EUV防護(hù)薄膜,并將該技術(shù)授權(quán)給三井化學(xué),該公司計(jì)劃在2021年第二季度開始批量銷售。此后,ASML改進(jìn)了防護(hù)薄膜

Imec已公開了其基于碳納米管的防護(hù)膜的測(cè)試結(jié)果

Graphene Square, Freudenberg Sealing Technologies (FST)和一些大學(xué)正在開發(fā)自己的防護(hù)膜

到目前為止,只有ASML設(shè)法為實(shí)際可用的EUV工具創(chuàng)建了商業(yè)上可行的防護(hù)膜。ASML的防護(hù)膜基于厚度為50 nm的多晶硅。早在2016年,他們就展示了在模擬175W光源上的78%的傳輸率。目前,ASML可以出售透射率達(dá)88%的防護(hù)膜。不久之后,三井將開始大量供應(yīng)此類防護(hù)膜。ASML推出的,由金屬硅化物制成的最新原型展示了90.6%的透射率,0.2%的不均勻性以及在400W光源下反射率小于0.005%的情況。

ASML防護(hù)薄膜產(chǎn)品經(jīng)理Raymond Maas在接受Bits&Chips.nl采訪時(shí)說:“此次升級(jí)支持我們的路線圖,最終將使電源功率高達(dá)400瓦。” “在該功率水平下,薄膜被加熱到600oC,而多晶硅則無(wú)法承受。” 相比之下,Imec的原型防護(hù)膜的透射率為97.7%。實(shí)際上,從長(zhǎng)遠(yuǎn)來看,當(dāng)可以使用更高級(jí)的光源時(shí),將需要更復(fù)雜的防護(hù)膜,這就是Imec基于碳納米管的防護(hù)膜將發(fā)揮作用的地方。

“很少有材料具有超過90%的高EUV透射率的潛力,甚至更少的材料可以同時(shí)兼容超過600W的EUV功率。此外,防護(hù)膜必須堅(jiān)固,才能懸掛在大面積的光罩上(? 110mm x 140mm),”來自Imec的研究人員Joost Bekaert說。不幸的是,目前尚不清楚Imec的基于碳納米管的防護(hù)膜何時(shí)準(zhǔn)備就緒。

現(xiàn)在,臺(tái)積電(TSMC)和三星(Samsung Foundry)發(fā)明了使用EUV光刻工具生產(chǎn)較小芯片的多die掩模,而不需要防護(hù)膜的方法,但是這種方法存在風(fēng)險(xiǎn),因?yàn)槿魏晤w粒添加劑都可能成為導(dǎo)致產(chǎn)量下降的缺陷。此外,這樣的方法對(duì)于較大的芯片和單die光掩模來說是有風(fēng)險(xiǎn)的,因此,防護(hù)膜對(duì)于使用EUV工具制造大型die至關(guān)重要。也就是說,無(wú)論光掩模的尺寸大小如何,都需要使用防護(hù)膜來提高EUV產(chǎn)量并降低整個(gè)領(lǐng)域的風(fēng)險(xiǎn)。

總體而言,EUV防護(hù)膜的使用和改進(jìn)將是一個(gè)循序漸進(jìn)的過程。由ASML開發(fā)和制造的初始防護(hù)膜,不久將由三井制造,足以滿足當(dāng)今的某些需求,但其透射水平仍有改進(jìn)的空間,這由ASML和Imec的下一代原型證明。由于這些機(jī)器將擁有更強(qiáng)大的光源,因此也需要更好的防護(hù)膜來應(yīng)對(duì)未來的掃描儀。但是,由于這樣的防護(hù)膜具有許多無(wú)可爭(zhēng)議的優(yōu)點(diǎn),它們將被芯片制造商使用,因?yàn)榧词挂砸恍┥a(chǎn)率為代價(jià),它們也可以幫助提高產(chǎn)量。

原文標(biāo)題:ASML的EUV光刻技術(shù)將迎來重大改進(jìn)

文章出處:【微信公眾號(hào):皇華電子元器件IC供應(yīng)商】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

責(zé)任編輯:haq

-

芯片

+關(guān)注

關(guān)注

455文章

50732瀏覽量

423266 -

晶圓

+關(guān)注

關(guān)注

52文章

4895瀏覽量

127939 -

光刻機(jī)

+關(guān)注

關(guān)注

31文章

1150瀏覽量

47384

原文標(biāo)題:ASML的EUV光刻技術(shù)將迎來重大改進(jìn)

文章出處:【微信號(hào):ameya360,微信公眾號(hào):皇華電子元器件IC供應(yīng)商】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

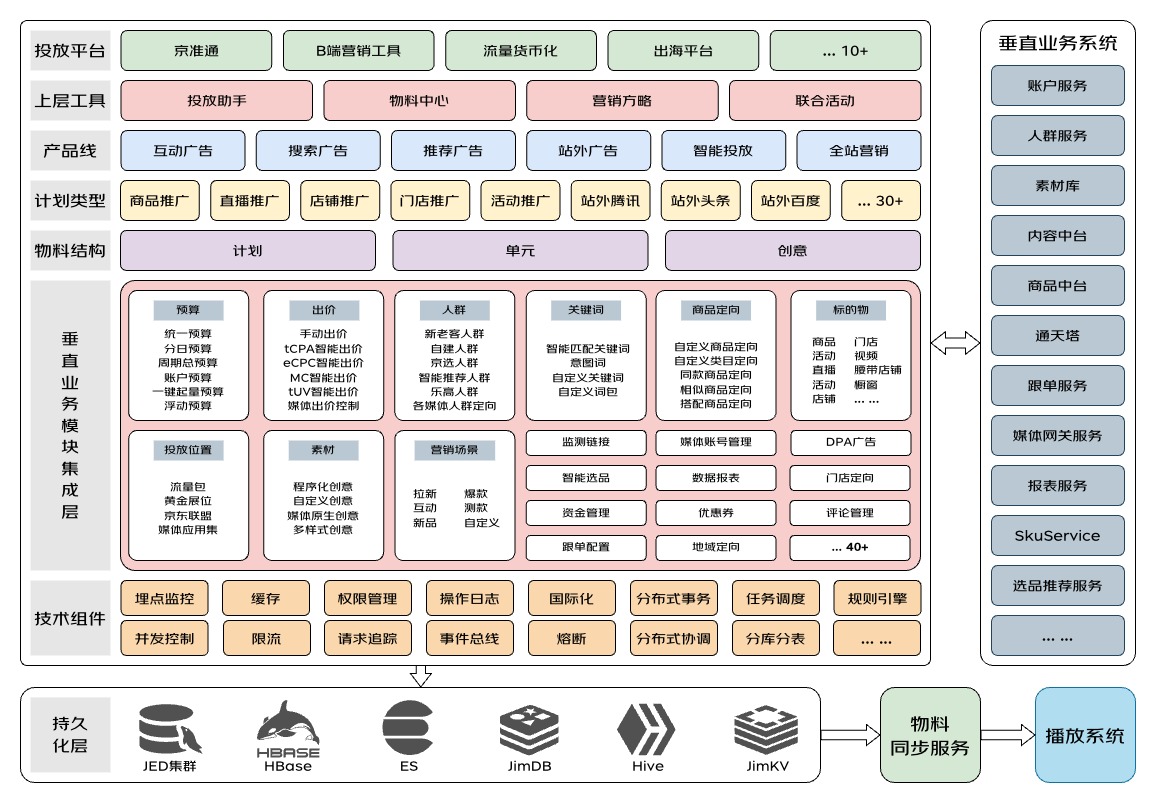

循序漸進(jìn)搭建復(fù)雜B端系統(tǒng)整潔架構(gòu)

一文了解嵌入式軟件開發(fā)的對(duì)象

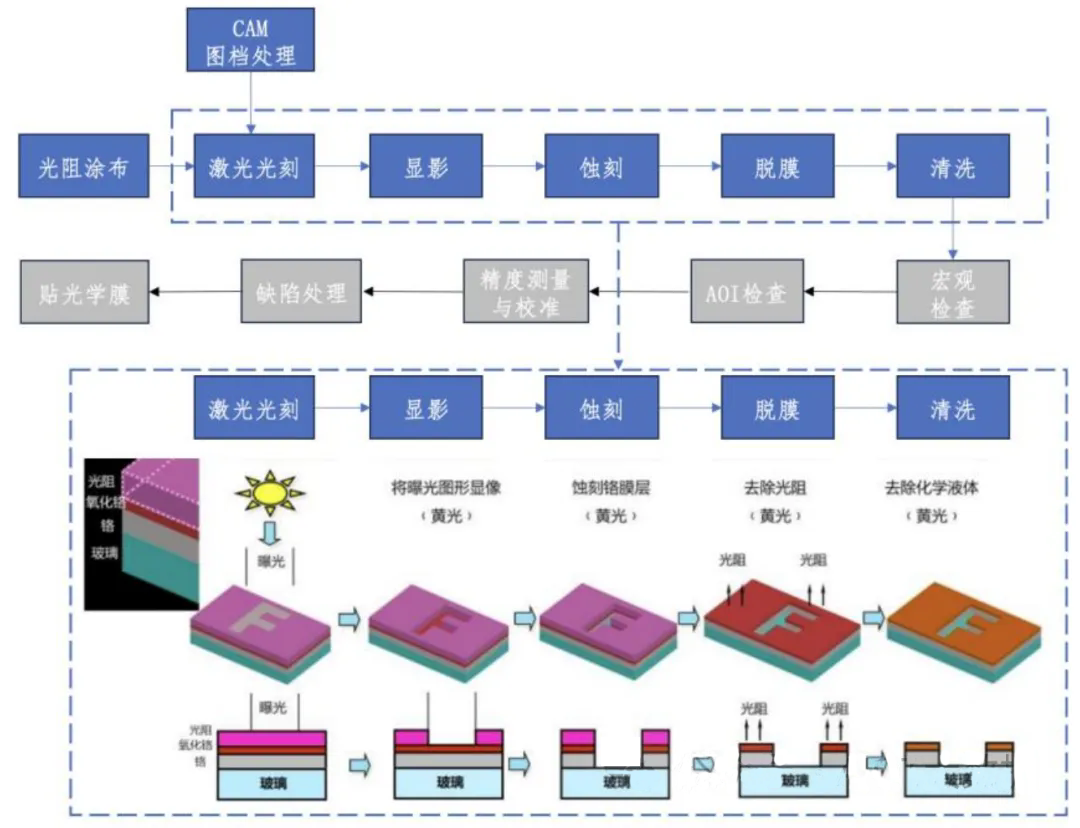

PCB樹脂膜產(chǎn)品制造工藝過程

sio2膜層鍍膜如何解決膜裂

【全新課程資料】正點(diǎn)原子《ESP32物聯(lián)網(wǎng)項(xiàng)目實(shí)戰(zhàn)》培訓(xùn)課程資料上線!

光刻掩膜版制作流程

PCB抗氧化膜:為電子線路板披上堅(jiān)固防護(hù)衣

膨體聚四氟乙烯e-PTFE透氣膜的IP防護(hù)等級(jí)要考濾哪些因素?

《DNK210使用指南 -CanMV版 V1.0》第一章本書學(xué)習(xí)方法

【《大語(yǔ)言模型應(yīng)用指南》閱讀體驗(yàn)】+ 俯瞰全書

M9航空插頭3針的外殼有防護(hù)膜嗎

電機(jī)控制中Iq與Id都是什么意思?

一文弄懂半導(dǎo)體掩膜版制造工藝及流程

高效在線監(jiān)測(cè)POLY膜厚方案——POLY5000在線膜厚測(cè)試儀

EUV防護(hù)膜的使用和改進(jìn)將是一個(gè)循序漸進(jìn)的過程

EUV防護(hù)膜的使用和改進(jìn)將是一個(gè)循序漸進(jìn)的過程

評(píng)論