一、主要概念

同步邏輯和異步邏輯:時鐘域?yàn)橛蓡蝹€時鐘或具有固定相位關(guān)系的時鐘驅(qū)動的設(shè)計部分。也就是說,在一個模塊中一個時鐘和他的翻轉(zhuǎn)或者分頻時鐘認(rèn)為是相同的時鐘域,其所驅(qū)動的邏輯是同步邏輯。在一個模塊中不具有相同相位和時間關(guān)系的時鐘被視為不同的時鐘域,其所驅(qū)動的邏輯是異步邏輯。

亞穩(wěn)態(tài):如果數(shù)據(jù)傳輸中不滿足觸發(fā)器的建立時間和保持時間,或者復(fù)位過程中復(fù)位信號的釋放相對于有效時鐘沿的恢復(fù)時間(recovery time)不滿足,就可能產(chǎn)生亞穩(wěn)態(tài)。亞穩(wěn)態(tài)就是無法避免的,亞穩(wěn)態(tài)主要發(fā)生在異步信號檢測、跨時鐘域信號傳輸以及復(fù)位電路等常用設(shè)計中。

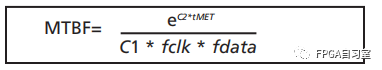

MTBF: 平均無故障工作時間,英文全稱:Mean time between failures;利用平均故障間隔時間(MTBF)公式可以預(yù)測亞穩(wěn)態(tài)的發(fā)生,MTBF越大則說明亞穩(wěn)態(tài)對電路產(chǎn)生的影響越小,反之亦然。

其中C1和C2是常數(shù),依賴于構(gòu)建觸發(fā)器所使用的技術(shù);tMET為在不引起同步失敗的前提下亞穩(wěn)態(tài)輸出持續(xù)時間,時間越長MTBF指數(shù)級增大,所以高頻電路兩級觸發(fā)器不夠可能要用三級觸發(fā)器來保證;fclk和fdata分別是同步時鐘和數(shù)據(jù)翻轉(zhuǎn)率;所以在不影響功能前提下,可以降頻工作頻率和數(shù)據(jù)的翻轉(zhuǎn)頻率,都可以有效的增大MTBF。

二、CDC典型錯誤場景

在芯片設(shè)計過程中,CDC正向確認(rèn)時經(jīng)常會發(fā)現(xiàn)幾種典型的錯誤場景:沒有處理直接裸跨、輸入同步器前組合邏輯輸出以及多路扇出和重新聚合場景等,還有一些不太常見情況未列出,請參閱文末資料。

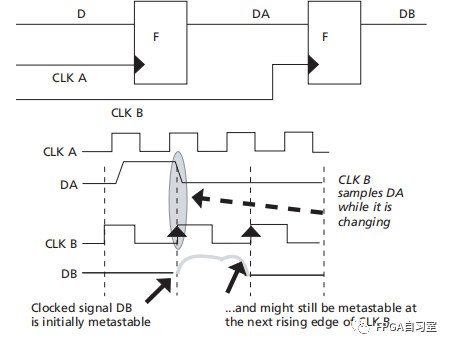

2.1直接裸跨

如上圖,如果CLK B采樣DA,而DA是變化的(在CLK的上升邊緣和下降D)的邊緣,則DB將是亞穩(wěn)態(tài)的,這種就是沒有使用同步器,顯然是不合理的。

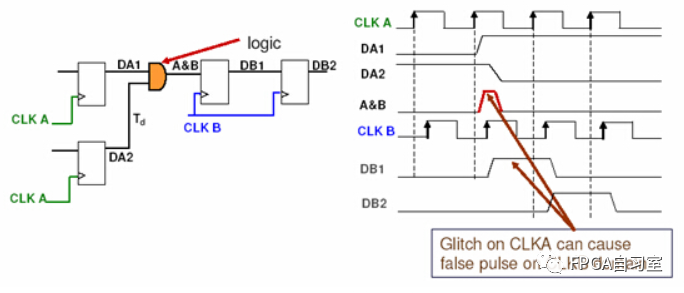

2.2毛刺(Glitch)

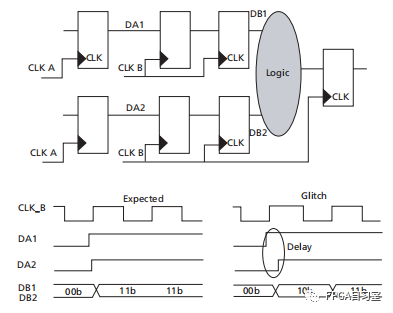

異步路徑時序工具不會進(jìn)行時序分析,這條道路上的任何邏輯都必須謹(jǐn)慎精心設(shè)計并驗(yàn)證,因?yàn)檫壿嬁赡軐?dǎo)致故障并在下游產(chǎn)生功能錯誤。如下圖所示,盡管兩個源觸發(fā)器同時給出脈沖,但由于布局布線以及環(huán)境原因而引起的傳播延遲(Td)不同,導(dǎo)致DA1和DA2信號不能同時到達(dá),因此在CLKA時鐘域下A&B會產(chǎn)生毛刺,而在CLKB時鐘域下產(chǎn)生一個假脈沖,導(dǎo)致后繼電路異常。正確的做法是將A&B在CLKA時鐘域下打一拍寄存器輸出。

此外,還有另外一種情況出現(xiàn)漏采,如下圖所示,DB1在CLKB時鐘域下應(yīng)有的高電平信號,由于DA1和DA2的傳輸延時不同,導(dǎo)致在CLKB下沒有傳遞出去。

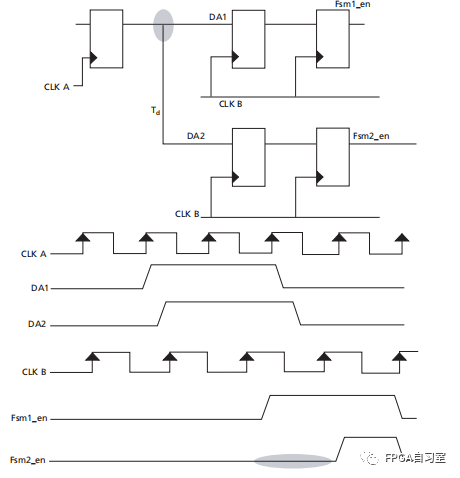

2.3多路扇出

單個信號扇出輸入到多個同步器時,由于輸入信號到達(dá)的同步器的時間不同(傳輸延時Td不同),同步可能需要一拍或者兩拍完成同步,此時同步后的各個信號之間可能存在錯拍問題。如下圖所示,DA1和DA2信號同步后分別是Fsm1_en 和 Fsm2_en信號,設(shè)計時如果仍認(rèn)為它們是相同的信號,就會導(dǎo)致邏輯功能錯誤。

2.4重新聚合(RECONVERGENCE)

在多bit跨時鐘傳輸過程中,如果各個bit之間分別使用單bit同步器進(jìn)行跨時鐘處理,在目的時鐘域又重新聚合起來。如下圖所示,DA1和DA2由于傳輸delay不同,在 CLKB上升沿采樣時,就會有2’10不期望值的出現(xiàn),這樣DB1和DB2進(jìn)行邏輯處理(聚合)時,也會得到不期望的值,這也是總線不能采用單bit同步器進(jìn)行跨時鐘處理的原因。此外,格雷碼是可以使用單bit同步器進(jìn)行處理的,AFIFO就是其典型設(shè)計。

擴(kuò)展:上述指的兩個兩級觸發(fā)器的單bit同步器,可以擴(kuò)展為兩個AFIFO總線跨時鐘,如果設(shè)計不當(dāng),只使用其中一個AFIFO的empty作為兩個AFIFO讀判斷,由于格雷碼同步的不確定性,導(dǎo)致兩個AFIFO的empty信號不一致,當(dāng)出口兩組總線聚合時,就會發(fā)生錯拍問題,從而導(dǎo)致功能異常。解決辦法是兩個AFIFO的讀條件應(yīng)該關(guān)聯(lián)或者使用一個大的AFIFO.

Referencecadencecdc(1)

Reference Spyglass cdc(2)

編輯:jq

-

CDC

+關(guān)注

關(guān)注

0文章

57瀏覽量

18164 -

復(fù)位電路

+關(guān)注

關(guān)注

13文章

325瀏覽量

45184

原文標(biāo)題:CDC(四) CDC典型錯誤案例

文章出處:【微信號:FPGA_Study,微信公眾號:FPGA自習(xí)室】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

如何用AN75779實(shí)現(xiàn)CDC通信?

求助,關(guān)于IMXRT1062主機(jī)CDC USB問題求解

多板 PCB 組裝中最常見的邏輯錯誤

STM32 HID和CDC組合設(shè)備無法枚舉成功是哪里出了問題?

cdc減振器控制原理是什么

CDC318A高性能時鐘緩沖器數(shù)據(jù)表

CDC2351高性能時鐘驅(qū)動器電路數(shù)據(jù)表

CDC2510C鎖相環(huán)時鐘驅(qū)動器數(shù)據(jù)表

CDC341時鐘驅(qū)動器數(shù)據(jù)表

具有三態(tài)輸出的CDC339時鐘驅(qū)動器數(shù)據(jù)表

CDC328A1時鐘驅(qū)動器數(shù)據(jù)表

關(guān)鍵指南針-NXP USB CDC_VCOM虛擬串口例程

評論