摘要: 針對數(shù)字圖像處理與傳輸領域數(shù)據(jù)量大而傳統(tǒng)接口無法滿足其高速率傳輸要求的現(xiàn)狀,提出了一種基于LVDS和PCI接口的高速圖像傳輸系統(tǒng)的設計,對系統(tǒng)總體設計和各電路模塊進行了詳細介紹和分析,并對系統(tǒng)整體功能進行了測試。該系統(tǒng)以FPGA作為控制核心,采用乒乓操作實現(xiàn)數(shù)據(jù)的無縫緩沖,重點研究了LVDS接口和PCI總線技術,保證圖像數(shù)據(jù)的高速、可靠傳輸。測試結果表明,該傳輸系統(tǒng)性能穩(wěn)定,能可靠地實現(xiàn)圖像數(shù)據(jù)傳輸,最大傳輸速率可達18 MB/s,具有一定的實用價值。

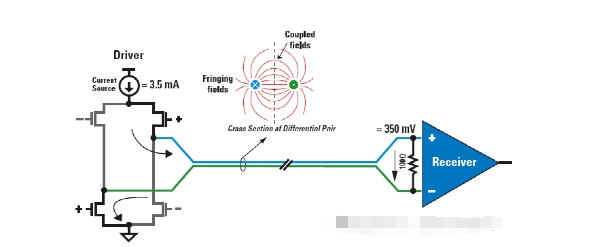

近年來,隨著電子信息、多媒體技術的快速發(fā)展,在圖像處理和視頻傳輸?shù)阮I域中傳輸?shù)臄?shù)據(jù)量越來越大,這對數(shù)據(jù)傳輸?shù)乃俣群唾|量提出了很高的要求[1]。然而,一些傳統(tǒng)的點對點物理層接口由于在速度、可靠性、功耗、成本等方面的限制,已經(jīng)無法滿足高速數(shù)據(jù)傳輸?shù)膽靡螅虼似惹行枰环N速率快、可靠性高、功耗低的數(shù)據(jù)傳輸方式。低壓差分信號技術LVDS(Low Voltage Differential Signaling)使用極低的擺幅通過雙絞電纜傳輸數(shù)據(jù),是一種最高傳輸速率可達1.923 Gb/s的通用接口技術,并且由于其低壓差分的傳輸方式,具有較強的抑制信號干擾能力,大大提高了數(shù)據(jù)傳輸?shù)木嚯x、速率和可靠性[2]。此外在計算機測量領域,PCI總線憑借其出色性能以及良好的兼容性,在工業(yè)控制、數(shù)據(jù)采集、信息通信、航空航天等領域得到廣泛的應用[3],為圖像數(shù)據(jù)高速傳輸提供了有力的保障。

結合LVDS接口與PCI總線能夠滿足高速傳輸?shù)奶匦裕疚闹饕獜南到y(tǒng)總體設計、硬件設計和邏輯設計等方面介紹一種基于LVDS和PCI接口的高速圖像傳輸系統(tǒng)。

1 系統(tǒng)總體設計

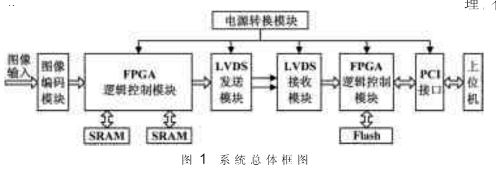

本文設計的高速圖像傳輸系統(tǒng)主要實現(xiàn)對數(shù)字圖像信息的編碼、傳輸以及顯示功能,突出傳輸系統(tǒng)的高效與可靠。系統(tǒng)采用模塊化設計思路,各個模塊之間既相互獨立又相互配合,主要由電源轉換模塊、圖像編碼模塊、LVDS收發(fā)模塊、FPGA邏輯控制模塊和PCI接口等模塊組成。其中,圖像編碼模塊的功能由軟件完成,根據(jù)圖像格式進行相應的二進制編碼; FPGA邏輯控制模塊實現(xiàn)系統(tǒng)對硬件高集成度的要求。系統(tǒng)總體框圖如圖1所示。

該系統(tǒng)的圖像信息輸入主要包括單幅圖片以及視頻流數(shù)據(jù),圖像編碼模塊首先根據(jù)內部協(xié)議規(guī)范的幀格式對圖像信息進行二進制編碼,之后將數(shù)據(jù)幀依次發(fā)送到FPGA邏輯控制模塊中;FPGA邏輯控制模塊對兩片SRAM采用乒乓操作,將接收到的數(shù)據(jù)交替讀/寫進行緩沖,然后通過LVDS發(fā)送模塊發(fā)送出去;在接收端,LVDS接收模塊對接收的數(shù)據(jù)進行串/并轉換,F(xiàn)PGA邏輯控制模塊將數(shù)據(jù)寫入Flash存儲芯片進行備份,同時將數(shù)據(jù)通過PCI接口傳輸給上位機進行處理及顯示。在此過程中,系統(tǒng)指令的下發(fā)均由上位機完成。

2 硬件設計

2.1 LVDS收發(fā)單元

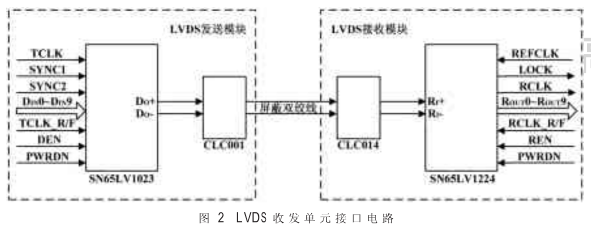

LVDS收發(fā)單元由LVDS發(fā)送模塊和LVDS接收模塊兩部分組成。設計選用美國德州儀器公司的10位總線型低壓差分信號串化器SN65LV1023A和解串器SN65LV1224A作為數(shù)字圖像數(shù)據(jù)高速傳輸?shù)腖VDS接口芯片,接口電路如圖2所示。

SN65LV1023/1224A芯片組采用主動工作模式,可輸入的頻率范圍為10~66 MHz,芯片最高傳輸速率可達792 Mb/s,具有初始化、同步、數(shù)據(jù)傳輸、休眠、高阻5種工作狀態(tài)[4]。該芯片組在正常工作之前必須經(jīng)過時鐘同步操作。當系統(tǒng)上電后,芯片組首先將輸出管腳置為高阻態(tài)并啟動鎖相環(huán),再由串化器發(fā)送SYNC(“000000111111”)同步信息,若解串器LOCK管腳置“0”,則說明時鐘已同步,可以進行數(shù)據(jù)傳輸。

在數(shù)據(jù)傳輸過程中,串化器將接收到的10 bit電平數(shù)據(jù)進行并/串轉換,然后將內嵌有時鐘信息的串行數(shù)據(jù)發(fā)送到差分端口經(jīng)由屏蔽雙絞線輸出;在接收端,解串器在REFCLK時鐘下將接收到的串行數(shù)進行串/并轉換并存入鎖存器中,根據(jù)重建的同步時鐘信號RCLK將10 bit并行數(shù)據(jù)輸出,從而完成整個傳輸過程。設計中采用內嵌時鐘恢復技術進行數(shù)據(jù)處理,有效地解決了由于時鐘與數(shù)據(jù)同步不嚴格而引起的制約其性能的一系列問題。

由于高頻信號在PCB導線和電纜上的損耗會使邊沿變化速率降低,引入碼間串擾,但這會導致傳輸信號衰減。所以為了保證數(shù)據(jù)的傳輸質量,設計中配合使用LVDS芯片和電纜延展器芯片。采用CLC001驅動器和CLC014均衡器實現(xiàn)高速傳輸?shù)男盘栒{理作用,降低了信號損耗,補償了信號衰減,從而保證數(shù)據(jù)傳輸?shù)姆€(wěn)定性和可靠性。

2.2 PCI接口單元

本設計采用PCI接口單元實現(xiàn)底層電路與上位機之間的數(shù)據(jù)傳輸。上位機通過PCI接口單元實現(xiàn)指令下發(fā)和數(shù)據(jù)上傳,并完成數(shù)據(jù)處理和顯示功能。PCI(Peripheral Component Interconnect)總線規(guī)范是一種高性能32/64 bit地址數(shù)據(jù)復用的高速外圍設備接口標準[5]。該總線具有眾多優(yōu)點,當采用33 MHz時鐘,32 bit數(shù)據(jù)總線最大傳輸速率可達132 MB/s,當擴展到64 bit數(shù)據(jù)總線后,其數(shù)據(jù)吞吐量可達264 MB/s的峰值。

如果換用66 MHz時鐘,數(shù)據(jù)傳輸速率理論峰值高達528 MB/s[6]。考慮到PCI協(xié)議復雜性較高,如果直接使用FPGA對其進行設計難度較大,因此采用PLX公司的PCI總線通用接口芯片PCI9054作為PCI總線與本地總線的橋接芯片,其控制方便、成本低廉、通用性強。PCI接口電路如圖3所示。

PCI接口單元主要由PCI9054、HT93LC56和外部晶振組成。PCI9054芯片提供PCI、LOCAL和E2PROM 3個接口,分別實現(xiàn)與PCI總線、本地總線和配置芯片的物理連接。本設計采用32 bit數(shù)據(jù)寬度,數(shù)據(jù)與地址不復用,故配置PCI9054工作在C模式下。測試指令的下發(fā)采用直接從模式,應用程序首先利用API將指令數(shù)據(jù)復制到主機內核空間,然后CPU通過驅動程序獲得PCI總線的控制權,實現(xiàn)對本地總線和配置寄存器的訪問;

而數(shù)據(jù)上傳過程由于數(shù)據(jù)量大、速率快,所以采用DMA方式,DMA方式無需CPU的參與即可實現(xiàn)本地總線與PCI總線的數(shù)據(jù)交換,能夠完成高速傳輸?shù)娜蝿铡?shù)據(jù)上傳操作同樣由應用程序發(fā)起,首先申請用戶空間用于存儲上傳的數(shù)據(jù),并通過API將其地址映射到內核空間地址,然后配置PCI內部的DMA寄存器,啟動DMA傳輸。在DMA方式下,PCI9054作為PCI總線和本地總線的主控設備,將本地總線中的數(shù)據(jù)傳輸至內核空間,此時應用程序通過訪問用戶空間處理上傳的數(shù)據(jù)。指令下發(fā)和數(shù)據(jù)上傳過程分別如圖4、圖5所示。

3 系統(tǒng)邏輯設計

3.1 FPGA邏輯程序

設計中,F(xiàn)PGA采用Xilinx公司的SPARTAN系列芯片,該芯片具有很高的邏輯資源,易于配置。系統(tǒng)發(fā)送端的FPGA邏輯控制模塊主要完成高速數(shù)據(jù)的接收緩存以及LVDS接口的時序控制。為了提高傳輸速度,避免數(shù)據(jù)流不連續(xù),系統(tǒng)采用“乒乓操作”,交替對兩片SRAM進行讀/寫。當FPGA接收到數(shù)據(jù)時,首先對SRAM 1進行寫操作,接著將下一幀圖像寫入SRAM 2;

同時對SRAM 1進行讀操作,并將讀出的數(shù)據(jù)轉發(fā)到LVDS發(fā)送模塊。系統(tǒng)在對一片SRAM進行寫操作的同時,可以對另一片SRAM進行讀操作,如此交替讀/寫有效地節(jié)省了等待時間,從而提高了數(shù)據(jù)的傳輸速度,實現(xiàn)數(shù)據(jù)的無縫緩沖與處理。“乒乓操作”控制時序流程如圖6所示。

3.2 固件配置

PCI9054內部寄存器的初始化配置由Microchip公司的E2PROM HT93LC56完成,主要包括PCI和Local配置寄存器、DMA寄存器、Runtime寄存器等寄存器組[7]。本設計采用從方式和DMA兩種數(shù)據(jù)傳輸方式,配置LAS0BA(0)=1、LAS0RR(0)=0、LBRD0(1:0)=11,將地址空間0作為指令下發(fā)的本地空間并設置數(shù)據(jù)寬度為32 bit;對DMA寄存器的配置包括:DMAMODE0(1:0)=11表示數(shù)據(jù)寬度為32 bit,DMAMODE0(8:7)=00表示傳輸采用單周期方式等。這些配置信息均可借助PLX公司提供的PLXMon工具進行燒寫。

4 測試結果

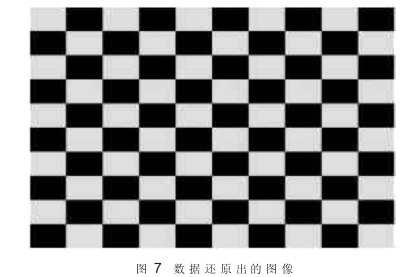

為了驗證本系統(tǒng)圖像數(shù)據(jù)處理與高速傳輸?shù)目煽啃裕瑢ζ湔w進行了功能測試。圖像信息源采用大小為720×480的黑灰規(guī)律變化的圖像,將二進制數(shù)據(jù)還原成圖片之后通過肉眼觀察并進行軟件分析來判斷是否發(fā)生錯誤。

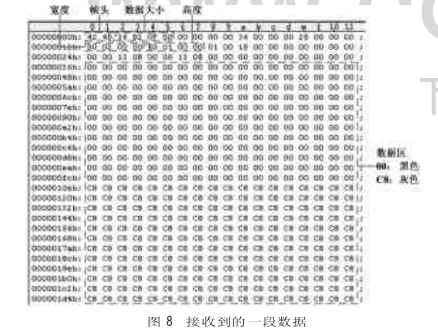

圖7是接收到的一幀數(shù)據(jù)還原出的圖像,圖像清晰明了,沒有明顯的異常現(xiàn)象。圖8是測試系統(tǒng)功能時計算機記錄的一段數(shù)據(jù),虛框內的“42 4D”為幀頭,“36 D2 0F 00”為一幀圖像的數(shù)據(jù)大小,“D0 02 00 00”和“E0 01 00 00”分別表示圖像的寬度與高度,隨后是圖像數(shù)據(jù)區(qū)域(“00”代表黑色,“C8”代表灰色)。經(jīng)過軟件對比分析,接收到的數(shù)據(jù)準確無誤碼,所以該系統(tǒng)可以實現(xiàn)設計功能并具有較高的穩(wěn)定性。

本文充分利用了LVDS技術的傳輸特點與應用優(yōu)勢,結合“乒乓”讀寫操作和PCI總線傳輸技術設計了一種基于LVDS和PCI接口的高速圖像傳輸系統(tǒng),并通過實驗驗證了該系統(tǒng)的可靠性和準確性。該系統(tǒng)可以應用到工業(yè)數(shù)據(jù)采集、測試等領域,具有較高的可靠性。

參考文獻

[1] 陳偉,宋燕星。基于LVDS技術的高速數(shù)圖像傳輸系統(tǒng)[J]。電子測量技術,2008,31(11):172-174.

[2] 彭鄉(xiāng)琳.LVDS在長距離信號傳輸中的應用[J]。兵工自動化,2006,25(7):60-61.

[3] 鄧鳳軍,張龍,王益忠。基于PCI總線的HDLC通信卡的設計與實現(xiàn)[J]。電子技術應用,2012,38(8):30-36.

[4] Texas Instruments.SN65LV1023A/SN65LV1224A 10-MHz to 66-MHz,10:1 LVDS serializer/deserializer[Z].2003.

[5] 安冬冬,劉文怡,郅銀周。基于PCI9054從模式的數(shù)據(jù)采集卡設計與應用[J]。計算機測量與控制,2010,18(10):2439-2440.

[6] 葉勇,沈三民,郭錚,等。基于PCI總線的高速串口通信卡的設計[J]。電視技術,2013,37(3):82-85.

[7] PLX Technology.PCI 9054 data book version 2.1[Z].2000.

編輯:jq

-

芯片

+關注

關注

456文章

50936瀏覽量

424677 -

PCI

+關注

關注

4文章

670瀏覽量

130332 -

lvds接口

+關注

關注

1文章

128瀏覽量

17439

發(fā)布評論請先 登錄

相關推薦

lvds接口與其他接口比較

lvds接口在工業(yè)顯示中的應用

lvds接口適用于哪些設備 lvds接口兼容性問題解析

lvds接口傳輸距離限制 lvds接口優(yōu)勢及劣勢分析

lvds接口和HDMI的區(qū)別 lvds接口電路設計技巧

lvds接口用途與應用 lvds接口連接方法指南

常見視頻高速接口MIPI,LVDS,RGB,HDMI分析

PCIe接口的工作原理 PCIe與PCI的區(qū)別

高速ADC與FPGA的LVDS數(shù)據(jù)接口中避免時序誤差的設計考慮

lvds接口需要驅動嗎

PCI 接口的反射內存卡

淺談LVDS和PCI接口的高速圖像傳輸系統(tǒng)設計

淺談LVDS和PCI接口的高速圖像傳輸系統(tǒng)設計

評論