1前言:

無線通信技術(shù)與網(wǎng)絡(luò)技術(shù)的迅猛發(fā)展推動了無線網(wǎng)絡(luò)技術(shù)深入應(yīng)用,針對能夠滿足軍事應(yīng)用需要的、可快速展開、高抗毀性的移動信息系統(tǒng)產(chǎn)生了無線自組織網(wǎng)絡(luò)。這種網(wǎng)絡(luò)沒有絕對的控制中心,所有節(jié)點(diǎn)的地位平等,網(wǎng)絡(luò)中的節(jié)點(diǎn)通過分布式算法來協(xié)調(diào)彼此的行為,無需人工干預(yù)和任何其它預(yù)置的網(wǎng)絡(luò)設(shè)施,可以在任何時(shí)刻任何地方快速展開并自動組網(wǎng)。要實(shí)現(xiàn)這樣的功能,對無線終端有著很高的要求,根據(jù)這種應(yīng)用需求,本文設(shè)計(jì)并實(shí)現(xiàn)了一種適合無線網(wǎng)絡(luò)的移動終端硬件平臺。

移動網(wǎng)絡(luò)終端的組成主要有兩部分:移動終端硬件平臺(以下簡稱硬件平臺)和主機(jī)。其中硬件平臺主要由射頻單元、基帶模擬單元、物理層基帶處理單元和MAC層處理單元組成,主要完成基于UTRA-TDD LCR的物理層協(xié)議的數(shù)據(jù)的發(fā)送和接收以及純無線網(wǎng)絡(luò)的MAC層的數(shù)據(jù)處理功能;主機(jī)部分主要由接口驅(qū)動單元、網(wǎng)絡(luò)層處理單元和應(yīng)用層處理單元組成,主要完成網(wǎng)絡(luò)層以及網(wǎng)絡(luò)層以上的處理數(shù)據(jù)處理功能。

其中移動網(wǎng)絡(luò)終端硬件平臺主要完成以下功能:能夠完成射頻信號的收發(fā)功能;能夠完成基帶模擬、數(shù)字信號的相互轉(zhuǎn)換功能;完成物理層基帶處理算法功能;MAC層、路由和主控的全部處理功能。目前實(shí)現(xiàn)該硬件平臺的方法主要有三種:OMAP+DSP+FPGA結(jié)構(gòu)、OMAP+DSP或OMAP+FPGA結(jié)構(gòu)以及主機(jī)+DSP+FPGA結(jié)構(gòu)。其中OMAP是TI公司以2.5代及第3代手機(jī)為應(yīng)用目標(biāo)推出的開放式多媒體應(yīng)用平臺,其內(nèi)核采用ARM及DSP相結(jié)合,具有很高的技術(shù)特性,同時(shí)具備支持3G標(biāo)準(zhǔn)。是目前通訊、PDA等廠家開發(fā)智能手機(jī)等通訊終端理想的開發(fā)實(shí)驗(yàn)平臺。

2 移動終端硬件平臺總體設(shè)計(jì)方案

上述的三種實(shí)現(xiàn)方案各有優(yōu)缺點(diǎn),對于第一種方案,優(yōu)點(diǎn)是:能夠做成一個(gè)相對完整的移動終端;電路設(shè)計(jì)相對簡單。缺點(diǎn)主要有:如果所有物理層基帶處理算法都放到一個(gè)FPGA或者DSP中實(shí)現(xiàn),那么對FPGA或者DSP的處理能力的要求則會非常的高: 開發(fā)難度和復(fù)雜度要求非常高,開發(fā)周期長。對于第二種方案,優(yōu)點(diǎn)和方案一一樣,移動終端的結(jié)構(gòu)相對完整;

并且采用DSP+FPGA結(jié)構(gòu)能夠較好的分配物理層基帶發(fā)送和接收算法,大大降低所需DSP和FPGA的處理能力。但其缺點(diǎn)是:對OMAP芯片的開發(fā)難度和復(fù)雜度依然很高,開發(fā)周期長;電路板設(shè)計(jì)的難度和復(fù)雜度提高,因?yàn)樯厦娉松漕l和基帶模擬部分以外,還要有DSP、FPGA、OMAP以及外圍器件。第三種方案,優(yōu)點(diǎn)是:能夠很好的分配物理層基帶算法,大大降低對DSP和FPGA的處理能力的要求;

并且將OMAP的功能放在了主機(jī)上,不僅簡化了電路設(shè)計(jì)的復(fù)雜度,而且也進(jìn)一步降低了開發(fā)成本和開發(fā)難度以及復(fù)雜度,同時(shí)縮短了開發(fā)周期。但缺點(diǎn)是設(shè)備不夠整體化,移動終端將分為物理層收發(fā)設(shè)備和主機(jī)設(shè)備,不便于移動。經(jīng)過分析比較,綜合考慮開發(fā)復(fù)雜度、成本等因素以后我們最后決定采用方案三的結(jié)構(gòu)設(shè)計(jì)。

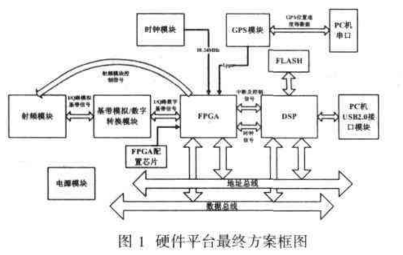

移動終端做更具體的設(shè)計(jì)是根據(jù)所確定的總體方案制定的。方案中的結(jié)構(gòu)分為兩部分:一部分是主機(jī),負(fù)責(zé)MAC、路由和主控等,一部分是物理層收發(fā)設(shè)備。主機(jī)部分無需硬件設(shè)計(jì),考慮的核心是物理層收發(fā)硬件平臺的設(shè)計(jì)。經(jīng)過分析,我們將物理層基帶處理算法在FPGA和DSP之間進(jìn)行了分配:FPGA主要完成基帶數(shù)據(jù)接口、AGC處理、基帶發(fā)送、除主徑載頻估計(jì)外的Midamble碼搜索及多徑分離、解擾、解擴(kuò)、RAKE合并以及相關(guān)控制功能的算法實(shí)現(xiàn);FPGA的配置程序存儲在配置芯片中。DSP主要完成主徑載頻估計(jì)、載頻精確估計(jì)、解速率適配、信道譯碼和CRC校驗(yàn)部分算法實(shí)現(xiàn)。DSP的運(yùn)行程序存儲在FLASH芯片中,啟動時(shí)由FLASH將程序加載至DSP。硬件平臺與主機(jī)之間的接口采用常用的USB2.0的接口方式。具體結(jié)構(gòu)框圖如下:

圖 一:硬件平臺最終方案框圖

3 DSP及FPGA芯片的選擇

首先是對DSP芯片的選取,DSP主要完成載頻估計(jì)、頻精確估計(jì)、速率適配、信道譯碼和CRC校驗(yàn)等算法的實(shí)現(xiàn)功能,經(jīng)過初步估算,這些算法所需實(shí)乘103120次;實(shí)加230752次。上面的運(yùn)算量評估沒有考慮程序運(yùn)行中一些大量的數(shù)據(jù)的讀寫和搬移的操作。DSP單元做完上面的運(yùn)算處理使用半個(gè)slot時(shí)間,那么對DSP的處理能力要求大約為1000 MIPS。

存儲量分析如下:這里存儲量包括載頻估計(jì)中包括本地訓(xùn)練序列的存儲、CZT運(yùn)算參數(shù)的存儲、中間變量的存儲和CZT運(yùn)算結(jié)果的存儲,頻偏信號表的存儲,載頻重置后數(shù)據(jù)的存儲,交織圖樣和解速率適配圖樣的存儲等,我們估計(jì)出總共需要存儲空間:231K字節(jié)。根據(jù)上面的資源評估,我們需要一個(gè)處理能力超過1000MIPS,存儲超過300K字節(jié)的DSP,最后我們選擇了TI公司的TMS320C64167E3作為移動終端硬件平臺的DSP。

DSP6416是 TI公司的TMS320C6000系列DSP中一款性能極高的32位定點(diǎn)DSP芯片。它是TI公司基于第二代、高性能的超常指令集結(jié)構(gòu)(VelociTI.2TM)而研發(fā)的一款DSP。在工作時(shí)鐘為720MHz時(shí),其最高處理能力能夠達(dá)到5760MIPS,并且具有極強(qiáng)的并行處理能力,內(nèi)部RAM存儲也能達(dá)到1M字節(jié)。

其二對于FPGA芯片,主要完成基帶數(shù)據(jù)接口、AGC處理、基帶發(fā)送、除主徑載頻估計(jì)外的Midamble碼搜索及多徑分離、解擾、解擴(kuò)、RAKE合并以及相關(guān)控制功能的算法實(shí)現(xiàn)。對于FPGA而言,處理速度基本都能滿足要求,重要的是芯片所含的資源能否滿足要求。經(jīng)過估算,這些算法大概需要500000門左右的資源,我們最終選擇了Altera公司Stratix系列的EP1S25B672芯片。該芯片包括有25660個(gè)LEs(邏輯單元)合600000左右個(gè)邏輯門,還含有10個(gè)高速DSP模塊和6個(gè)PLLs等資源。

4 主要硬件電路的設(shè)計(jì)

由于電路中的元器件比較多(包括FPGA、DSP、GPS模塊、射頻模塊、A/D、D/A等),而且FPGA和DSP都是5、6百個(gè)管腳的BGA封裝,再加上一些外圍芯片,要想在一塊電路板上設(shè)計(jì)所有的電路會很難將電路板做的很小,而且數(shù)字基帶電路比模擬部分的電路復(fù)雜的多,電路板的層數(shù)也會增加,如果把數(shù)字和模擬設(shè)計(jì)在一塊電路板上,模擬部分的多出的電路板層數(shù)就會顯得有些浪費(fèi)。為縮小電路板的面積,降低設(shè)計(jì)成本,我們將硬件平臺分為兩部分,一部分是基帶數(shù)字部分,包括所有與基帶數(shù)字解調(diào)有關(guān)的電路;另一部分是模擬部分,包括數(shù)字/模擬、模擬/數(shù)字的轉(zhuǎn)換電路和射頻模塊。兩塊電路板之間靠雙排插針連接,模擬射頻電路板在數(shù)字基帶板的上面。

硬件平臺中各器件所需電壓的種類比較多,一共有4種:DSP核電壓1.4V、FPGA核電壓1.5V、射頻模塊供電電壓3.6V以及其它器件所需電壓3.3V。因此電源模塊的設(shè)計(jì)是一個(gè)重點(diǎn)部分,如果用線性穩(wěn)壓模塊,由于輸入電壓12V與電路板上所需電壓之間的壓差較大,穩(wěn)壓模塊將消耗大部分電壓,造成供電功耗的浪費(fèi)。

因此我們選擇了基于PWM脈寬調(diào)制的DC/DC穩(wěn)壓模塊(凌特公司的LT1940)。該芯片支持3.6~25V的直流電壓輸入,提供兩個(gè)最大1.4A的直流穩(wěn)壓輸出。我們使用了3片LT1940來提供這4種電壓,其中一片專門提供3.3V的電壓,因?yàn)檫@是電路板中80%元器件的供電電壓(包括DSP和FPGA的I/O電壓、它們的外圍器件的供電電壓以及A/D、D/A的供電電壓等),消耗的電流較大,大約為1.5~2A左右;還有一片提供FPGA和DSP的核電壓,其中DSP內(nèi)核最高消耗900mA電流,F(xiàn)PGA內(nèi)核最高消耗450mA電流;第三片用來給射頻模塊提供3.6V的電壓,因?yàn)樯漕l模塊消耗的電流也較大,最高可達(dá)2A。

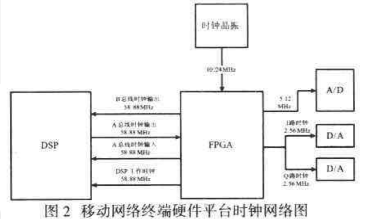

另外,時(shí)鐘網(wǎng)絡(luò)是電路板設(shè)計(jì)中十分重要的環(huán)節(jié)之一。在本硬件平臺中,晶振是WINTRON的10.24MHz TCXO型的(穩(wěn)定度是±3Hz,電流消耗小余2mA,TTL輸出)。晶振將10.24MHz的時(shí)鐘輸入到FPGA,然后FPGA產(chǎn)生出自己內(nèi)部和其它器件的工作時(shí)鐘。整個(gè)硬件平臺的時(shí)鐘網(wǎng)絡(luò)如下圖所示:

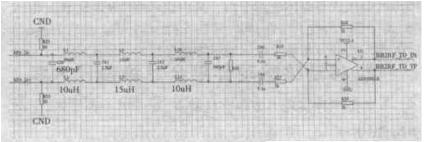

輸出與差分運(yùn)放AD8138之間,這樣既能夠使其較小的輸入阻抗適合D/A的電流輸出,也能夠有效的限制輸出頻帶,同時(shí)AD8138起到了低通網(wǎng)絡(luò)與射頻模塊之間的阻抗隔離作用。

信號經(jīng)過低通網(wǎng)絡(luò)以后,阻抗特性或多或少帶有一些容性或者感性,直接接到射頻模塊上信號就會有所失真,而差分運(yùn)放能夠起到很好的隔離作用,使輸出的信號阻抗具有較純的阻性,提高輸入射頻模塊的信號質(zhì)量,其電路圖如圖三所示。對于接收而言,由于射頻模塊自帶有接收的低通濾波器,因此電路較發(fā)送要簡單許多,只需在接收A/D之間接一個(gè)差分運(yùn)放起隔離驅(qū)動作用即可。

圖 三:模擬基帶發(fā)送電路原理圖

另外,在PCB板設(shè)計(jì)過程中還應(yīng)采取一些必要的措施,盡可能地避免或減少一些干擾因素的產(chǎn)生。比如,在PCB布板時(shí),電路各部按模塊分區(qū),各分區(qū)模塊內(nèi)相對集中,分區(qū)模塊之間相對獨(dú)立,這樣能減少相互間干擾。此外PCB板的布局時(shí)首先要考慮PCB尺寸大小。PCB尺寸過大時(shí),印制線條長,阻抗增加,抗噪聲能力下降,成本也增加;過小,則散熱不好,且鄰近線距過小易受干擾。在確定PCB尺寸后,先確定特殊元件的位置。最后,根據(jù)對電路的各功能模塊分區(qū),對電路的全部元器件進(jìn)行布局。

5 創(chuàng)新點(diǎn)總結(jié)

本文的創(chuàng)新點(diǎn)是通過分析選取并實(shí)現(xiàn)了一種基于DSP的移動網(wǎng)絡(luò)終端硬件平臺的設(shè)計(jì)方案,在總體結(jié)構(gòu)方案確定以后的對分析了主要元器件的選型依據(jù)。接下來重點(diǎn)闡述了硬件電路的原理圖設(shè)計(jì),包括各個(gè)主要部分的具體設(shè)計(jì),最后講述了PCB電路板的實(shí)際設(shè)計(jì)中需要注意的一些實(shí)際問題。

參考文獻(xiàn):

1 Altera Corporation,Stratix Device Handbook[M] ,May 2003

2 許永和。 EZ-USB FX 系列單片機(jī)USB外圍設(shè)計(jì)和應(yīng)用[M]。 北京:北京航空航天大學(xué)出版社,2002

3 劉繼承等,DS/FH混合擴(kuò)頻接收機(jī)解擴(kuò)及同步技術(shù)的FPGA實(shí)現(xiàn)[J],電子技術(shù)應(yīng)用,2003年第1期

4 張紹軍 黃 振,高速數(shù)字系統(tǒng)中的信號完整性及實(shí)施方案[J],電子技術(shù)應(yīng)用,2003年第2期

5 王春海張?jiān)隽?數(shù)控機(jī)床的螺距誤差檢測及補(bǔ)償[J],微計(jì)算機(jī)信息,2006, 1-1:228-229

編輯:jq

-

dsp

+關(guān)注

關(guān)注

553文章

8014瀏覽量

349196 -

AGC

+關(guān)注

關(guān)注

0文章

161瀏覽量

51690 -

主機(jī)

+關(guān)注

關(guān)注

0文章

998瀏覽量

35168

發(fā)布評論請先 登錄

相關(guān)推薦

DSP平臺與RTB的關(guān)系

移動數(shù)字網(wǎng)絡(luò)連接不上怎么辦

ip網(wǎng)絡(luò)音頻終端是什么

AM57XX處理器平臺ARM和DSP通信的實(shí)現(xiàn)

探究DSP的移動網(wǎng)絡(luò)終端硬件平臺如何實(shí)現(xiàn)

探究DSP的移動網(wǎng)絡(luò)終端硬件平臺如何實(shí)現(xiàn)

評論