摘 要: 通過在MEMS信號處理電路中設計一個異步結構的FIFO,可以有效地降低系統對MEMS的頻繁訪問。設計一個具有多種工作模式的FIFO,可以滿足一些特殊的姿態檢測需求,更好地滿足系統智能化操作需要。實現了一個具體可行的方案,可以實際應用到各種MEMS電路模塊中。

MEMS傳感器是采用微電子和微機械加工技術制造出來的新型傳感器。目前,加速度計已普遍用于智能終端(如智能手機)中,未來幾年,陀螺儀也將普遍應用到智能終端中。同時,組合傳感器,如3軸加速度計+3軸磁力計,3軸加速度計+3軸陀螺儀,甚至9軸組合傳感器未來都會得到廣泛應用,相應地也會帶來數據處理量的增加。

目前的加速度計、陀螺儀和磁力計等MEMS電路的數據輸出速率一般在幾赫茲到幾百赫茲之間。主系統處理單元一般通過串行通信接口I2C或者SPI訪問MEMS電路來獲取數據,除了需要實時響應的一些數據以外,主系統單元有時可能不希望頻繁地用串行接口去檢測MEMS電路狀態,看內部數據是否已經準備好,然后讀取有效數據,因為這樣會降低整個系統的工作效率。對于類似于智能手機的智能終端而言,隨著功能越來越強大,系統處理的任務也越來越多,如何平衡將是一個問題。

針對上述情況,本文設計了一個48 bit數據寬度、64級存儲深度的異步FIFO(First In First Out),可以有效解決主系統單元頻繁訪問MEMS電路的問題。這個FIFO具有旁路模式、連續模式、先入先出模式和中斷模式4種工作模式,在中斷模式下,通過設置不同的條件,可以在不需要主系統單元干涉的情況下自動抓取一些特殊狀態的數據。這樣可以節省很多系統資源。

1 FIFO系統設計

傳統異步FIFO[1-2]采用觸發器同步異步輸入信號來降低出現亞穩態的幾率,然后地址通過格雷碼編碼方式來消除地址多位變化導致的空滿狀態誤判,需要用到真正的雙端口RAM。采用觸發器同步雖然可以降低亞穩態的幾率,但也帶來了時序分析和綜合后仿真的難點。格雷碼帶來了設計的復雜性,可以通過時序邏輯的設計方式,在布局布線時插入時鐘樹來避免空滿狀態的不定。同時真正的雙端口RAM不是每個集成電路工藝線都支持的,采用偽雙端口RAM更實際,也能使設計適用范圍更廣泛。

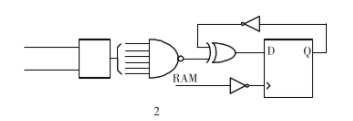

整個系統實現還要包括I2C和SPI接口模塊、信號處理模塊以及中斷檢測模塊,本文僅僅描述FIFO模塊。FIFO模塊的實現框圖如圖1所示。寫時鐘是MEMS數據采樣時鐘,讀時鐘是串口I2C或者SPI讀數據時鐘。為了消除讀寫同時進行產生的沖突,增加了一個寫使能信號,其與寫時鐘同時由內部邏輯產生,寫時鐘比讀時鐘優先級高。

這樣可能會引入一個問題,那就是讀寫恰好同時進行的時候,讀的數據依然是上一個數據,但可以設置為先入先出模式,數據滿了之后不再更新,這樣就不會有這個問題。模式設置和水印閾值設置通過串口I2C或者SPI寫入。同步雙端口RAM采用SMIC 0.18 m工藝Memory Compiler綜合出來的64×48 bit的IP模塊,這是一個偽雙端口RAM,讀寫時鐘是共用的。48 bit數據寬度可以同時存儲3個軸的MEMS檢測數據,每個軸16 bit數據寬度,基本可以滿足目前的MEMS精度要求。

2 功能模塊設計

2.1 讀地址產生邏輯

讀地址產生邏輯,根據工作模式和FIFO的狀態,生成讀地址指針。假如讀時鐘有效,并且FIFO不為空,則讀地址加1,假如FIFO為空,則讀地址保持不變。在連續工作模式下,由于數據不斷滾動更新,當數據滿的情況下,假如寫入有效,讀地址加1,保證讀地址指針指向最先寫入的數據地址。

2.2 寫地址產生邏輯

假如寫入有效,寫地址指針自動加1。通過控制RAM時鐘,在先入先出模式下,假如FIFO滿,終止寫入新的數據到RAM中,因此寫地址指針不再更新,除非重新使能整個FIFO模塊。

2.3 狀態生成邏輯

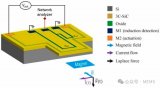

FIFO的狀態可以直接用寫地址指針減去讀地址指針來獲得,但也需要考慮到當FIFO滿的時候,讀地址指針和寫地址指針是指向同一個地址的,這時候減出來數據就為0了。因此需要增加中間寄存器,在未滿的時候輸出減法器的數值,在滿的時候輸出全1數值。滿和空狀態信號、水印標記信號和FIFO停止信號都由時序邏輯生成,滿信號邏輯電路圖如圖2所示,用RAM時鐘的反相信號來觸發。

水印標記可以通過設置水印的閾值來獲得,閾值范圍可以是0~63。當FIFO的狀態值超過設置的閾值,就產生水印標記中斷;當FIFO的狀態小于設置的閾值,水印標記中斷就清除,這可以讓主系統根據應用場合靈活選擇。FIFO停止信號有兩種情況,在先入先出模式下,滿了之后產生FIFO停止信號,RAM數據停止更新;在中斷模式下,在中斷信號產生之前,不產生FIFO停止信號,中斷信號產生之后,根據滿狀態信號產生FIFO停止信號。

3 工作模式

3.1 旁路模式

在旁路模式下,復位信號有效,FIFO不工作,主系統單元直接讀出ADC輸出的數據。

3.2 連續模式

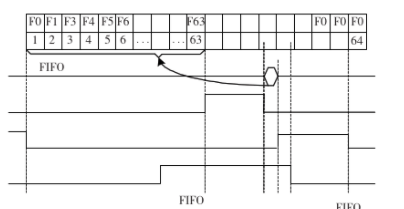

在連續模式下,數據在FIFO里面不斷更新,相應地,讀地址指針和寫地址指針也不斷滾動更新,讀地址指針指向最先輸入的RAM地址。在連續模式下,假如數據滿了之后,寫時鐘有效,讀地址指針和寫地址指針需要同時加1,因為最先的數據已經被覆蓋了。同時在寫時鐘無效的時候,讀時鐘有效,讀地址指針也要加1。

3.3 先入先出模式

在先入先出模式下,數據填充滿了就自動終止,產生滿中斷信號。在沒有讀時鐘的情況下,最終讀地址指針和寫地址指針將會同時指向地址0。相應地,在未充滿的情況下,假如讀時鐘有效,最終讀地址指針和寫地址指針會同時指向中間某一個地址。

3.4 中斷模式

在中斷模式下,數據先是以連續模式工作,假如中斷信號有效,進入先入先出模式,數據填充滿了就自動終止。工作時序圖如圖3所示,數據在未填充滿的情況下,產生中斷信號,數據填充滿了就產生終止信號,滿中斷信號置1,數據開始讀出之后,滿中斷信號清0,當數據完全讀完后,空中斷信號置1。假如FIFO需要重復上面的工作流程,需要清中斷,重新啟動FIFO,在數據開始重新寫入FIFO時,空中斷信號清0。

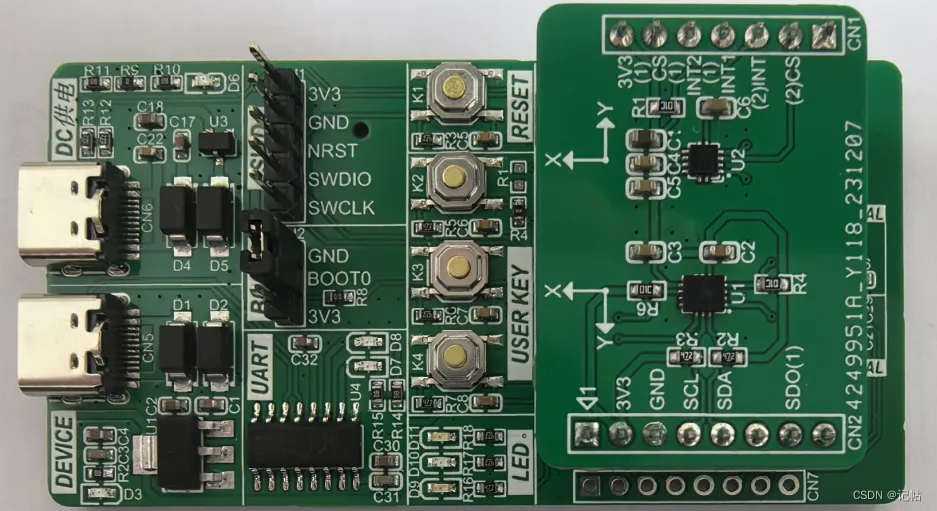

與傳統的異步FIFO不同,本文實現了一個更加簡單、并且實際可行的FIFO結構,操作靈活可靠。通過在MEMS信號處理電路中加入異步FIFO設計,可以更好地滿足系統對低功耗和操作靈活性的需求。通過DC綜合并流片驗證,該FIFO電路已經應用到多個MEMS電路產品中,得到很好的效果。特別對于未來MEMS組合傳感器、數據量的增加以及特殊姿態的處理,引入更多靈活性的FIFO將會帶來更多的優越性。

參考文獻

[1] 于海,樊曉椏.基于FPGA異步FIFO的研究與實現[J].微電子學與計算機,2007(3):210-213.

[2] 劉祥遠,陳書明.一種高性能的異步FIFO結構[J].電子學報,2007(11):2098-2104.

編輯:jq

-

mems

+關注

關注

129文章

3945瀏覽量

190780 -

RAM

+關注

關注

8文章

1369瀏覽量

114768 -

fifo

+關注

關注

3文章

389瀏覽量

43738 -

智能終端

+關注

關注

6文章

882瀏覽量

34787

發布評論請先 登錄

相關推薦

一種高靈敏的化學檢測系統

盤點5種應用最廣MEMS傳感器

FIFO Generator的Xilinx官方手冊

mems傳感器是什么意思_mems傳感器原理是什么

陀螺儀LSM6DSOW開發(4)----中斷獲取FIFO數據

意法半導體新款MEMS IMU LSM6DSV32X實現精確姿態識別應用

驅動LSM6DS3TR-C實現高效運動檢測與數據采集(8)----中斷獲取FIFO數據并應用MotionFX庫解析空間坐標

同步FIFO和異步FIFO區別介紹

一種常用的電流檢測電路,收藏!

蘋果公司申請一種新型MEMS揚聲器或微型揚聲器設計

淺談一種用于MEMS姿態檢測的FIFO設計

淺談一種用于MEMS姿態檢測的FIFO設計

評論