1引言

隨著現代電子技術和大規模集成電路的發展,DDS技術是一種新穎的頻率合成技術,并得到了飛速的發展,已成為最重要的頻率合成技術,其具有易于控制、相位連續、輸出頻率穩定度高、頻率轉換速度快和分辨率高等優點。SOPC(system on a programmable chip)片上可編程系統是一種靈活、高效的SOC解決方案,它具有雙重含義,首先是片上系統,有單個芯片完成整個系統的主要的邏輯功能,其次他是可編程的系統,具有靈活的設計方式,可裁減、可擴充、可升級,并具有軟硬件在系統可編程的功能。通過NiosII嵌入式系統實現SOPC,設計一種基于FPGA的多波形發生器,可以輸出正弦、余弦、方波、三角波和鋸齒波等常見波形,同時可以完成AM調制、FM調制、FSK調制等多種調制信號,具有很強的實用價值。

2系統設計

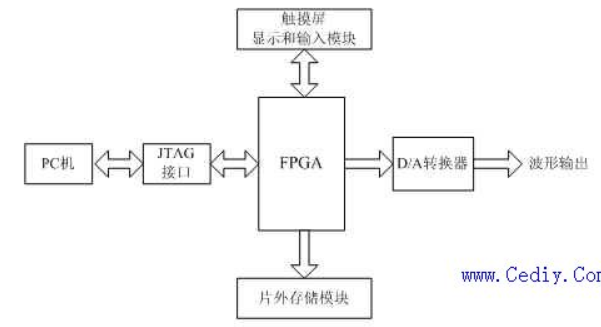

系統包括FPGA、觸摸屏顯示和輸入模塊、片外存儲模塊、D/A轉換器和JTAG接口,FPGA中配置NiosII軟核CPU、信號發生模塊和相關的接口控制邏輯電路,所述觸摸屏顯示和輸入模塊、片外存儲模塊、D/A轉換器和JTAG接口均與FPGA相連,FPGA通過JTAG接口和PC機連接,FPGA通過D/A轉換器后波形輸出。觸摸屏顯示和輸入模塊為TFT液晶觸摸屏,提供人機交互界面,負責界面顯示和外部輸入。片外存儲模塊為SDRAM存儲器。D/A轉換與濾波電路主要由D/A轉換、濾波、幅值調節和電源模塊組成。PC端軟件有Matlab編程實現,完成用戶界面(GUI)、編輯產生波形數據、頻率控制和與片上系統通訊等功能,系統框圖如圖1所示。

3 SOPC硬件設計

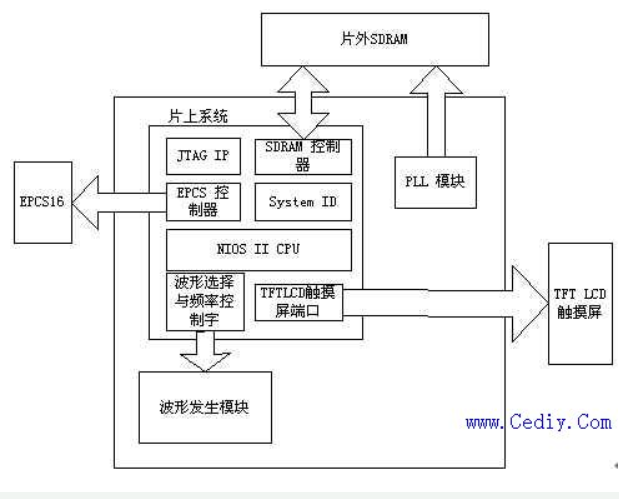

SOPC系統主要包括NIOSIICPU、SDRAM控制器、和I/O接口,通過調用Altera公司提供對應的IP進行定制設計,整個NiosII系統如圖2所示。

圖2.片上系統總體框圖

該模塊通過SOPC Builder中調用IP庫組建實現,主要由NiosII CPU、SDRAM控制器、通用IO、EPCS控制器、system ID、JTAG UART,與外部鏈接的端口主要五個部分,分別是系統時鐘與復位、TFT LCD控制信號線、觸摸屏控制信號線、SDRAM接口控制線、序列信號發生器控制信號線等,構成了整個系統的軟件底層硬件平臺部分,系統時鐘100MHZ。

設計中考慮到片上RAM存儲的數據量較大而NIOSII CPU只負責UART串口的數據傳輸可簡單的接口控制,故NIOSII CPU選擇NiosII/f經濟型內核。SDRAM控制器用來連接板上集成的64MByte SDRAM。SDRAM控制器的數據端dq[15.。.0]連接輸入輸出端口bidir。在Presets中選擇第一項Custom,在Bits中選擇16,完成SDRAM控制器的設置。IO口主要用于TFT LCD觸摸屏的控制以及相關信號線,還包括信號的輸出、SDRAM的控制信號線等。System ID是一種標示符,類似校驗,在下載程序之前或者重啟之后,都會對其進行檢驗,以防止Quartus和NIOS程序版本不一致的錯誤發生。JTAG UART是實現PC和NiosII系統間的串行通信接口,它用于字符的輸入輸出,在NiosII的開始調試過程中扮演了重要的角色。PLL模塊通過調用QuartusII內嵌的器件函數實現,QuartusII內嵌了許多常用器件的函數,用戶只需要進行設置即可直接調用,而不需要自己編程,這大大提高了系統開發的效率。SDRAM芯片必須和Avalon接口一樣以相同的時鐘驅動,片內的鎖相環(PLL)通常用于調整SDRAM控制器內核與SDRAM芯片之間的時鐘相位差。由于PLL不是包括在SDRAM控制器內,所以必須手動添加生成PLL模塊。設計中,片外SDRAM的時鐘輸入必須比系統的時鐘滯后-75度相位(注意不同型號的SDRAM器偏移角度不同)。

4波形發生模塊的設計

4.1 DDS原理

DDS技術是一種把一系列數字量形式的信號通過DAC轉換成模擬量形式的合成術,目前使用最廣泛的一種DDS方式是利用高速存儲器作為查尋表,然后通過高DAC產生已經用數字形式存入的波形。DDS的主要思想是從相位的概念出發合成所需要的波形,其結構由相位累加器、波形存儲器、數模轉換器、低通濾波器和參考時鐘五部分組成。相位累加器由N位加法器與N位累加寄存器級聯構成,每來一個時鐘脈沖fs,加法器將頻率控制字k與累加寄存器輸出的累加相位數據相加,把相加后的結果送至累加寄存器的數據輸入端。累加寄存器將加法器在上一個時鐘脈沖作用后所產生的新相位數據反饋到加法器的輸入端,以使加法器在下一個時鐘脈沖的作用下繼續與頻率控制字k相加。這樣,相位累加器在時鐘作用下,不斷對頻率控制字進行線性相位累加。由此可以看出,相位累加器在每一個時鐘脈沖輸入時,把頻率控制字累加一次,相位累加器輸出的數據就是合成信號的相位,相位累加器的溢出頻率就是DDS輸出的信號頻率。用相位累加器輸出的數據作為波形存儲器(ROM)的相位取樣地址,把存儲在波形存儲器內的波形抽樣值(二進制編碼)經查找表查出,完成相位到幅值轉換。波形存儲器的輸出送到D/A轉換器,D/A轉換器將數字量形式的波形幅值轉換成所要求合成頻率的模擬量形式信號。低通濾波器用于濾除不需要的取樣分量,以便輸出頻譜純凈的正弦波信號。

4.2頻率和幅度調節

用上述方法產生的波形,其波形頻率由兩方面決定:

(1)波形的頻率由地址計數器的計數時鐘決定,當波形存儲器的點數一定時,計數器的計數時鐘頻率越快,讀出一周期波形數據的時間就越短,輸出波形的頻率就越高,反之則波形頻率低。

(2)波形的頻率也由組成一周期波形的點數來確定,當地址計數器的時鐘頻率一定時,一周期波形的發生器點數越多,讀完一周期波形所需的時間越長,波形頻率就越低,反之則越高。

由于相位累加器字長的限制,相位累加器累加到一定值后,其輸出將會溢出,這樣波形存儲器的地址就會循環一次,即意味著輸出波形循環一周。故改變頻率控制字即相位累加器步進,就可以改變相位累加器的溢出時間,在時鐘頻率不變的條件下就可以改變輸出頻率。

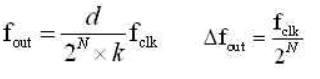

由此,可推出該系統的輸出頻率fout與系統時鐘頻率fclk之間的關系為:

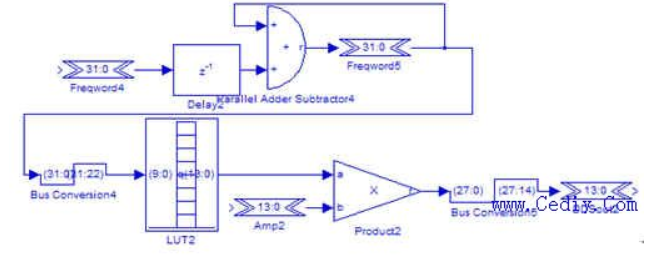

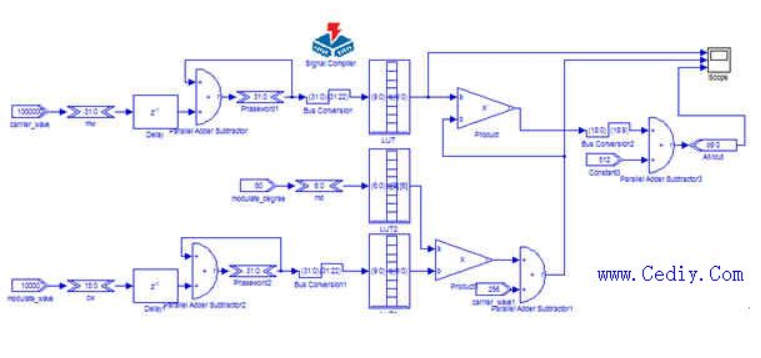

4.3 Matlab/DSP Builder中的常規波形設計

根據DDS工作原理,在Matlab下建立DDS基本原理圖的模型如圖3所示,設計中頻率控制字Freqword為32位,ROM表中LUT2中共存儲了位寬為14位的2048個波形數據,其中在波形ROM查找表的MatlabArray中根據輸出的波形填寫不同的數據公式,詳細公式如下:

正弦波:8191*sin([0:2*pi/(2^11):2*pi])

方 波:8191*square([0:2*pi/(2^10):2*pi])+8192

三角波:8191*sawtooth([0:2*pi/(2^10):2*pi],0.5)+8192

鋸齒波:8191*sawtooth([0:2*pi/(2^10):2*pi])+8192

Delay為延時單元,綜合后為寄存器,Haraller Adder Subtractor是并行加法器,Bus Conversion是總線寬度轉換,Product為加法器,Amp為波形幅度控制數據14位寬。

4.4 Matlab/DSPBuilder中的調制信號的設計

4.4.1 AM調制信號

AM幅度調制函數可簡單表示為F=Fdr*(1+Fa*m),其中Fdr,Fa,F分別是載波信號,調制波信號及調制后AM輸出的信號,他們都是有符號函數;m是調制度(0《m《1)。根據AM調制信號的工作原理,利用Matlab建立AM基本原理圖的模型如圖4所示,首先根據公式構建一個載波信號Vo(t)=VoCOSωot頻率carrier_wave為1000000的載波信號,波形函數為511*sin([0:2*pi/(2^10):2*pi]),其次再構建一個諧調制信號:VΩ(t)=VωcosΩt頻率modulate_wave為10000,波形函數為255*sin([0:2*pi/(2^10):2*pi]),與調制度modulate_degree為0.5相乘后再與載波信號經過Product相乘便可得到AM調制信號,由于ADC輸出的正信號因此再將信號由-512~+512轉換成0~1024,以便于后期輸出轉換。

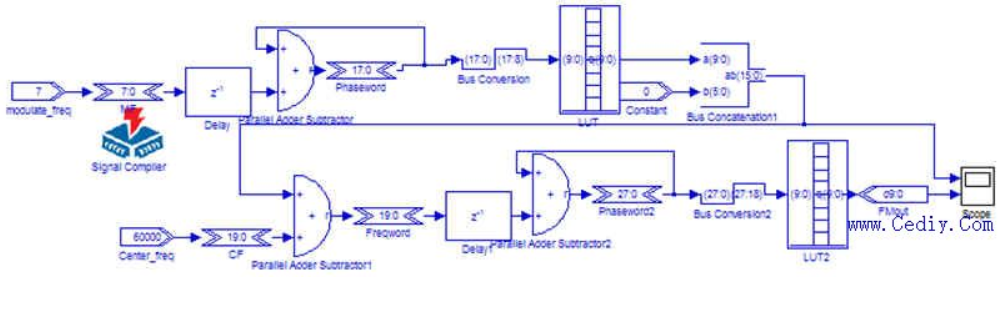

4.4.2 FM調制信號

根據FM調制信號的工作原理,利用Matlab建立FM基本原理圖的模型如圖5所示,先構建調制信號函數為511*sin([0:2*pi/(2^10):2*pi])將輸出數據向左移動6位,低6位補0構成16位數據再與中心頻率控制字相乘控制中心頻率的輸出,中心頻率ROM函數511*sin([0:2*pi/(2^10):2*pi])+512。

圖5.FM調制模型

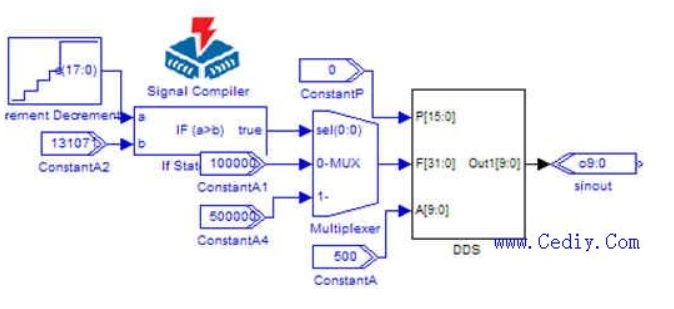

4.4.3 FSK調制信號

根據FSK調制信號的工作原理,利用Matlab建立FSK基本原理圖的模型如圖6所示,incerment Decerment是一個遞增的時鐘計數模塊位寬是18位與131071相比較生產二進制序列,控制選擇模塊Multiplexer來選擇送給DDS模塊的頻率控制字,在此分別設置了兩個頻率Constant1和Constant2,DDS模塊負責頻率的輸出結構與前面常規波形設計形似,在此不再贅述。

5 PC端軟件設計

系統另一大特點就是能與PC聯機使用,通過個人計算機對FPGA進行調度指揮控制,并能監控設備的運行狀態,使波形輸出。在GUI界面中,設置了公式波的公式輸入文本編輯框,只需要在文本編輯框中輸入公式,根據它已有的條件就可以產生信號波形,由于輸入的公式是用戶自定義的,用戶可以使用多種算法或者運用MATLAB自帶的函數庫。文本編輯框里輸入文本后,MATLAB會把輸入的文本默認成字符串。當想對這些輸入在文本編輯框里的公式進行計算時,MATLAB無法識別,故使用Eval函數對字符串進行處理。Eval符號表達式轉化為數值表達式,這樣就能使MATLAB執行公式,公式法產生的波形更精確。

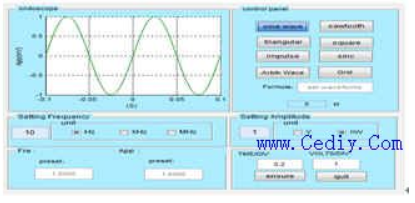

用戶界面軟件如圖7所示,波形選擇按鈕中,用戶可以選擇正弦波、方波、鋸齒波、三角波、sinc波、線性調頻信號等,選擇波形的同時將波形數據發送給信號發送給信號發生器。用戶也可以自定義編輯波形,有公式法編輯和繪圖法編輯,使用繪圖法編輯波形,只需點擊“任意波形”按鈕,然后按照提示在坐標軸內點擊鼠標右鍵取點畫出所要波形的大概形狀,再點擊鼠標左鍵就可以產生用戶想要的波形;當使用公式法編輯波形,只需按提示在編輯框中寫入所要產生的波形公式,點擊“任意波”按鈕,系統就會立刻對輸入公式進行計算,并向硬件傳送改變波形類型的字符,然后再把數據發送到硬件上。界面幅頻預值設定中頻率單位在Setting Frequency中選擇,幅度單位在Setting Amplitude中選擇。用戶可以在Fre和App一欄中預設幅頻大小,通過改變文本框中的數值,可以改變輸出波形的值以及界面圖形的顯示比例。

6 系統仿真和測試

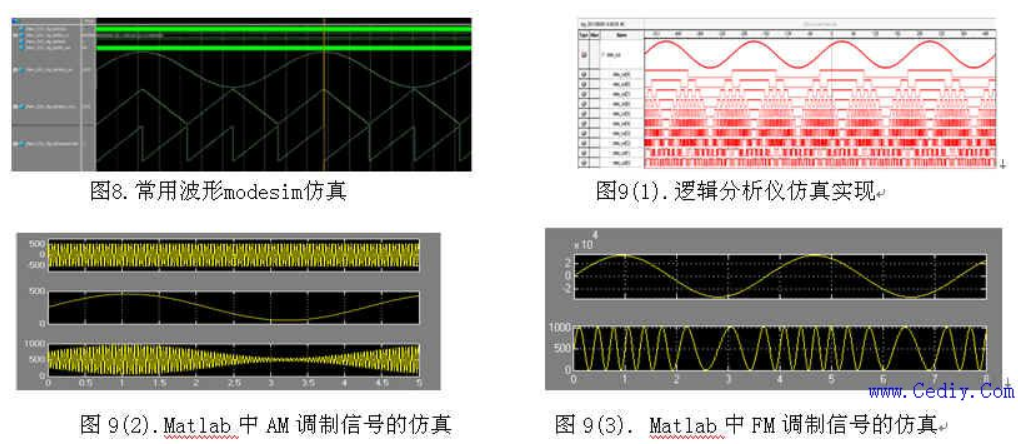

系統使用第三方仿真工具Modelsim對DDS模塊進行功能仿真,也就是前仿真,仿真結果如圖8所示。由于Modelsim只在功能上進行仿真,對器件的延時沒有考慮在內,因此將系統下載配置到FPGA當中,使用QuartusII自帶的signalTapII邏輯分析儀對波形輸出端口數據進行采集,能夠真實的反映本設計在硬件上的實現情況,如圖9所示。

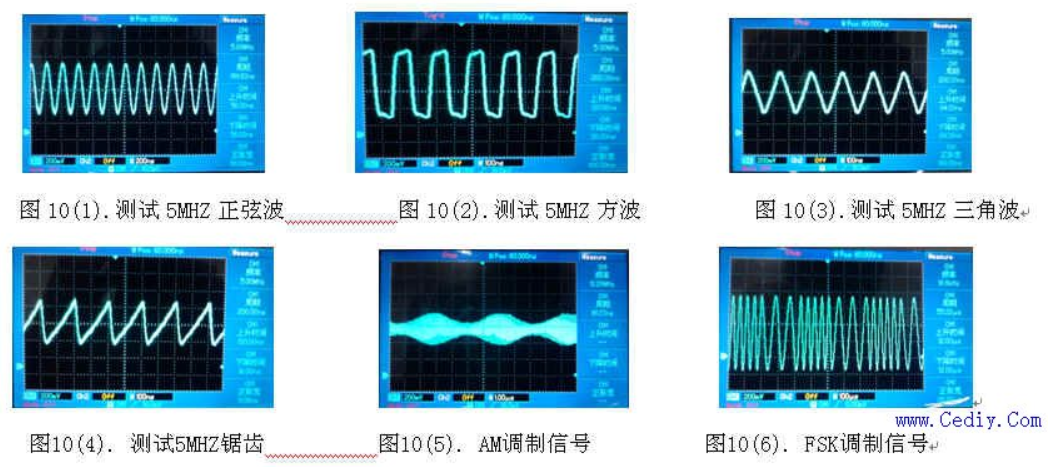

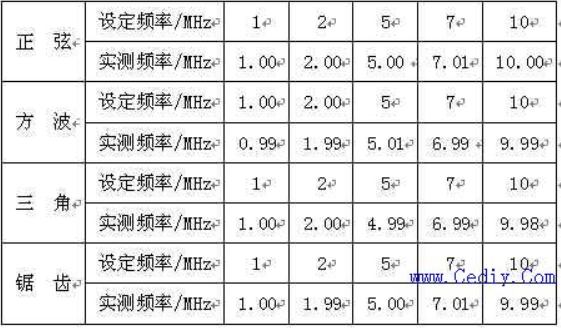

將輸出信號連接至示波器對系統的各項指標進行測試,測試條件:(示波器UTD2062CEL,60MHZ,1GS/s,輸出5MHZ正弦波、三角波、方波、鋸齒波),顯示的頻率為5.00MHZ。主要分以下幾個步驟:在波形選擇界面分別選擇正弦波、三角波、方波、鋸齒波的波形和頻率;選擇AM調制信號輸出,在示波器觀察AM信號的調制;選擇FM調制信號輸出,在示波器觀察FM信號的調制;選擇FSK調制信號輸出,在示波器觀察FM信號的調制;連接至PC端測試在PC端控制波形輸出和頻率控制,示波器輸出如圖10所示,測量數據結果如表1示:

表1.波形頻率數據測試表格

可以計算出,數據率平均誤差約為0.1576%。在測試為隨機信號的時鐘時發現其時鐘信號有信號的反射現象,進過分析發現如果IC之間的互連線比較長,線的特性阻抗又不均勻,或者終端沒有匹配,會引起反射,如果始端也不匹配,則會來回反射而造成振鈴。該現象的決定因素:特性阻抗、匹配方式、失配大小終端反射系數、始端反射系數、線長,分析原因是因為電路板是手工焊接的,信號完整性不是太好,同時也由于傳輸阻抗不匹配,因此通過在時鐘信號線的終端和源端分別串接一個33Ω的電阻發現這種振鈴現象得到了很大的抑制。

7 結束語

系統采用DDS技術,通過基于NIOSII的SOPC系統實現了任意發生器在相對帶寬、頻率轉換時間、相伴連續性、正交輸出、高分辨率及集成化的性能方面較好,同時基于NiosII的SOPC系統可以根據用戶需要自由定制CPU及其個性,具有較強的靈活性和通用性。

參考文獻

[1]魏麗娟,肖鐵軍,郎沁爭等。基于SOPC的任意波形發生器人機交互系統設計[J]。計算機測量與控制,2012,10:2860-2862

[2]楊守良。利用Matlab/DSP Builder實現DDS的設計[J]。微計算機信息,2006,20:211-212

[3]吳麗華,劉洪濤,李勝明等。基于FPGA的程控多波形發生器的研制[J]。電測與儀表,2007,12:52-54

[4]劉暢,李智。基于FPGA的任意波形發生器的設計[J]。微計算機信息.2010(02):130-131

[5]周俊峰,陳濤。基于FPGA的直接數字頻率合成器的設計和實現[J]。電子技術應用.2002(12):74-76

[6]孫超,林占江。基于DDS的雷達任意波形信號源的研究[J]。電子測量與儀器學報.2008(02):31-35

[7]陳科,葉建芳,馬三涵。基于DDS+PLL技術頻率合成器的設計與實現[J]。國外電子測量技術.2010(04):43-47

[8]陳風波,冒燕,李海鴻。基于FPGA的直接數字頻率合成器的設計[J]。微計算機信息.2006(05):189-190

[9]張芳芳,周火鳳,宋麗輝等。基于DSP和USB的數據采集系統的設計[J]。儀表技術與傳感器.2010(07):66-68

[10]鄧岳平,肖鐵軍。基于FPGA的并行DDS信號發生器的設計與實現[J]。計算機工程與設計.2011(07):2319-2323

編輯:lyn

-

FPGA

+關注

關注

1638文章

21879瀏覽量

610716 -

sopc

+關注

關注

2文章

248瀏覽量

62821 -

信號發生器

+關注

關注

28文章

1525瀏覽量

109732

發布評論請先 登錄

相關推薦

評論