在FPGA開發過程中不可避免的要使用到一些IP,有些IP是很復雜的,且指導手冊一般是很長的英文,僅靠看手冊和網絡的一些搜索,對于復雜IP的應用可能一籌莫展。

這里以Xilinx為例,在Vivado中使用SRIO高速串行協議的IP演示如何使用官方例程和手冊進行快速使用,在仔細閱讀參考官方例程后進行一些修改就可以應用在實際項目中。

一、導入IP

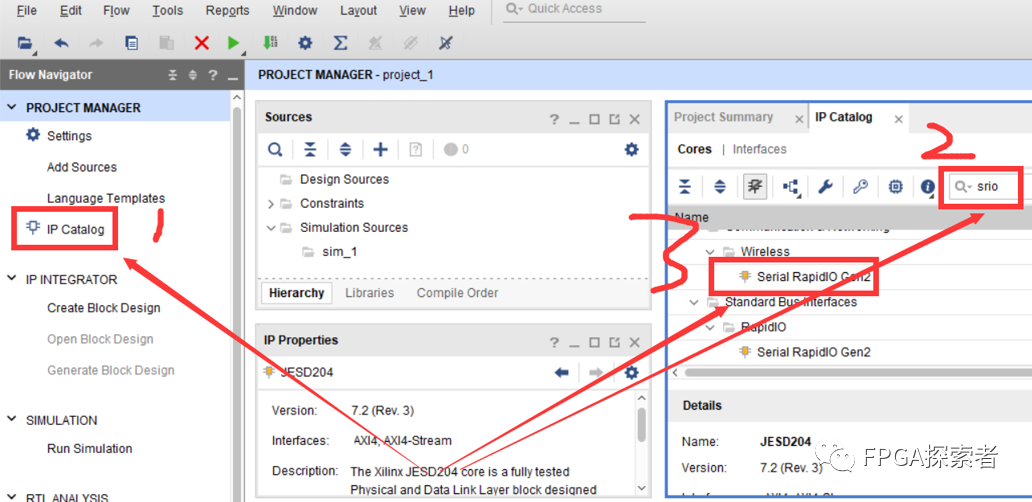

點擊“IP Catalog”,選擇要使用的IP,雙擊3處配置IP。

二、配置IP

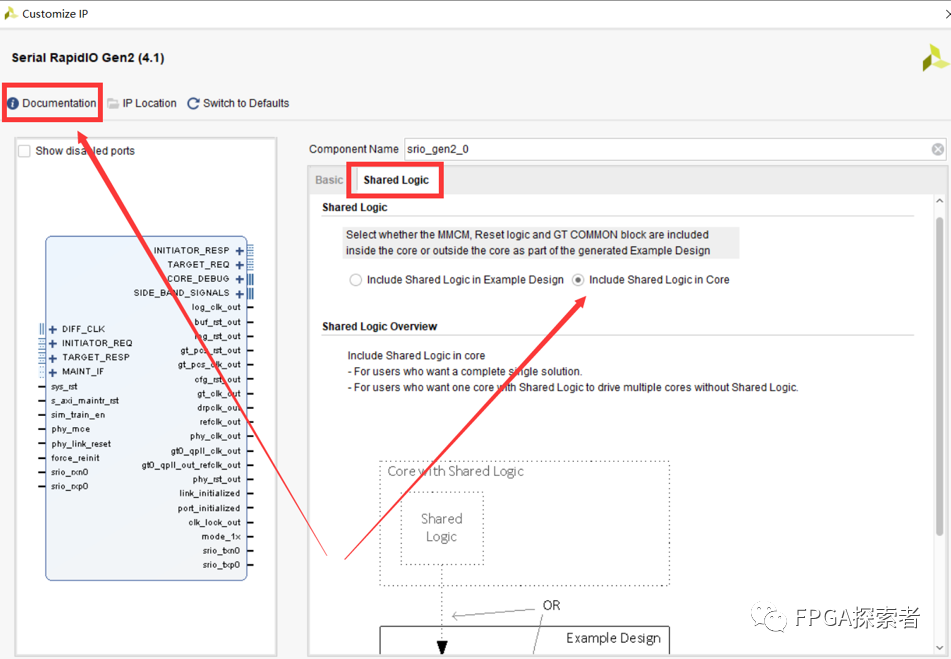

點擊左上角可以閱讀官方的IP說明手冊、IP更新信息、常見問題及解決方式。根據實際的需求配置IP的參數,如工作時鐘等。

在“Shared Logic”選項中(SRIO、Aurora、JESD204等使用GT的IP核中常常有此選項),如果選擇“Include Shared Logic inExample Design”(推薦方式),則在IP核外部的示例工程中生成時鐘、復位等必要邏輯,且這些邏輯作為共享邏輯,加入使用多個IP核時,可以共享一些復位等信號,且這些時鐘、復位可以被使用者修改;

當選中“Include Shared Logic in Core”(簡單)選項時,時鐘、復位邏輯等邏輯被包含在IP核中,對其他的IP不可見,這些邏輯也不能被修改(Read-Only)。

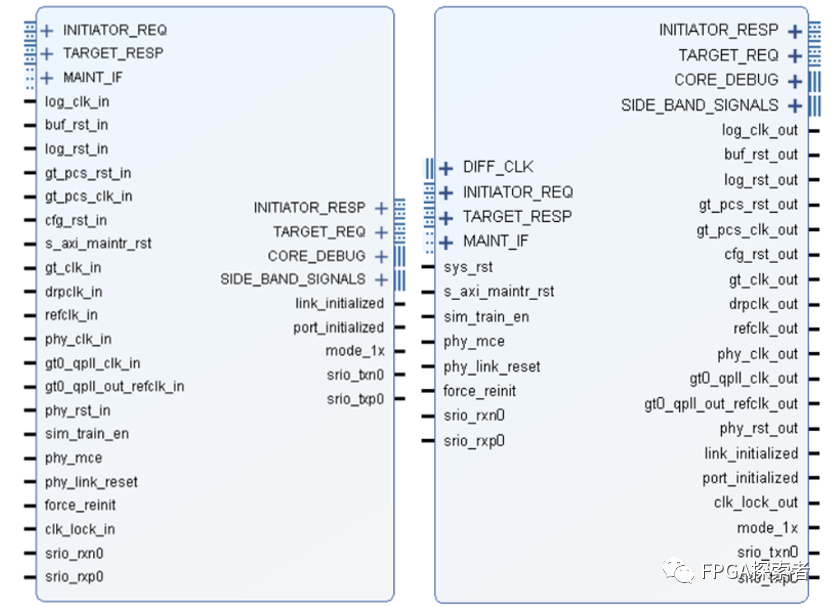

下圖中左邊是“IncludeShared Logic in Example Design”,右邊是“Include Shared Logic in Core”,可見不同配置下IP對外呈現的時鐘、復位和GT的一些引腳是不同的。

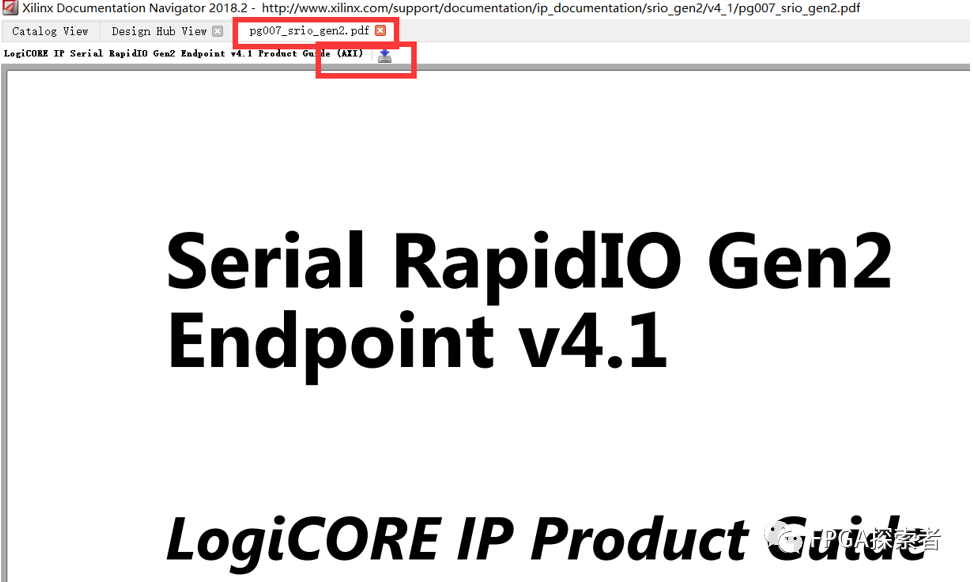

三、閱讀手冊

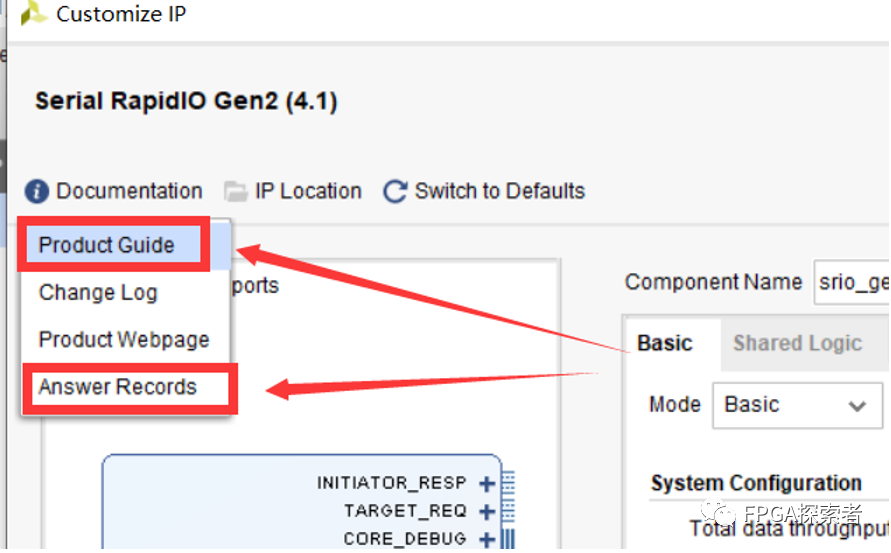

點擊“Product Guide”可以轉到Xilinx的DocNav中,查看、閱讀、下載各FPGA器件手冊、開發板資料、IP手冊。Xilinx官方手冊和配套例程是最具參考價值的資料,沒有其他。雖然是英文版,但是借助翻譯軟件及關鍵詞查找,還是能夠進行閱讀。

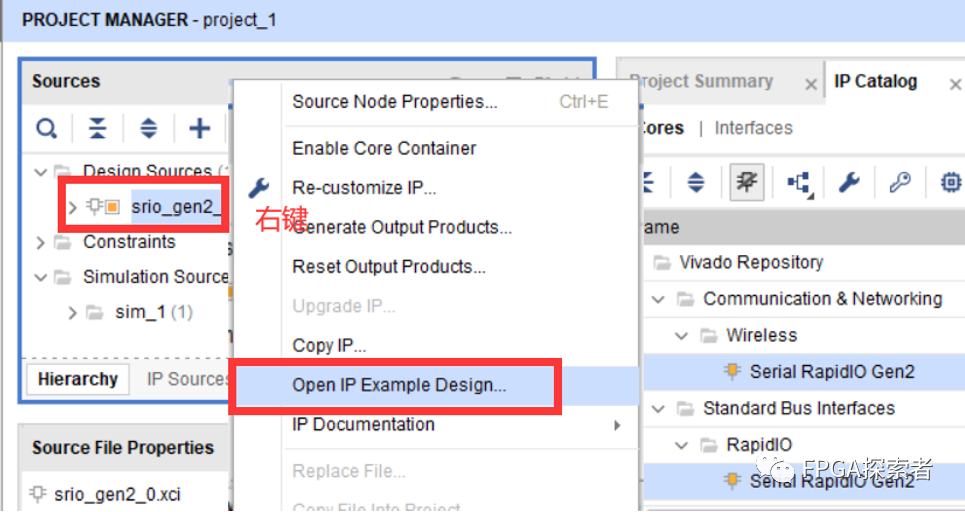

四、生成例程

選擇OOC編譯,等編譯完成后,右鍵“Open IPExample Design”,打開IP對應配置下的測試工程,選擇指定路徑,自動打開新生成的測試工程。

五、閱讀示例工程,仿真分析

工程中包含了時鐘、復位及輸入輸出、AXI總線協議等必要的配置,包含TestBench仿真測試文件,閱讀分析源碼,仿真查看波形,通過少量更改可以下板測試,ILA監測,參考示例工程,在實際應用中即可使用。

選擇“Include Shared Logic inExample Design”(推薦方式),則在IP核外部的示例工程中生成時鐘、復位等必要邏輯,且這些邏輯作為共享邏輯,加入使用多個IP核時,可以共享一些復位等信號,且這些時鐘、復位可以被使用者修改;

選中“Include Shared Logic in Core”(簡單)選項時,時鐘、復位、GT收發器配置是包含在IP核內部,對其他的IP不可見,這些邏輯也不能被修改(Read-Only),不對外呈現。

運行仿真即可查看波形,加入內部信號的波形到窗口,可以分析內部的信號,包括物理層PHY、協議層LOG等多個信號。(加入內部信號的方式可以參考matlab與FPGA數字濾波器設計(6)—— Vivado 中使用 Verilog 實現并行 FIR 濾波器/截位操作)

其余 IP 類似使用,多閱讀官方的IP手冊和例程。

原文標題:如何使用Xilinx官方例程和手冊學習IP核的使用,以高速接口SRIO為例

文章出處:【微信公眾號:FPGA技術江湖】歡迎添加關注!文章轉載請注明出處。

責任編輯:haq

-

FPGA

+關注

關注

1629文章

21729瀏覽量

603016 -

Xilinx

+關注

關注

71文章

2167瀏覽量

121311

原文標題:如何使用Xilinx官方例程和手冊學習IP核的使用,以高速接口SRIO為例

文章出處:【微信號:HXSLH1010101010,微信公眾號:FPGA技術江湖】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

SRIO介紹及xilinx的vivado 2017.4中生成srio例程代碼解釋

【米爾-Xilinx XC7A100T FPGA開發板試用】+03.SFP光口測試(zmj)

vivado導入舊版本的項目,IP核心被鎖。

捷米特EtherNet/IP轉MODBUS網關將變頻器接入EtherNet/IP

FPGA的SRIO接口使用應注意的事項

高速串行通信協議都有哪些

高速串行通信協議詳解

交換板設計方案原理圖:473-SRIO_Switch_Gen2_ZD交換板卡

在Vivado中使用SRIO高速串行協議的IP演示官方例程

在Vivado中使用SRIO高速串行協議的IP演示官方例程

評論