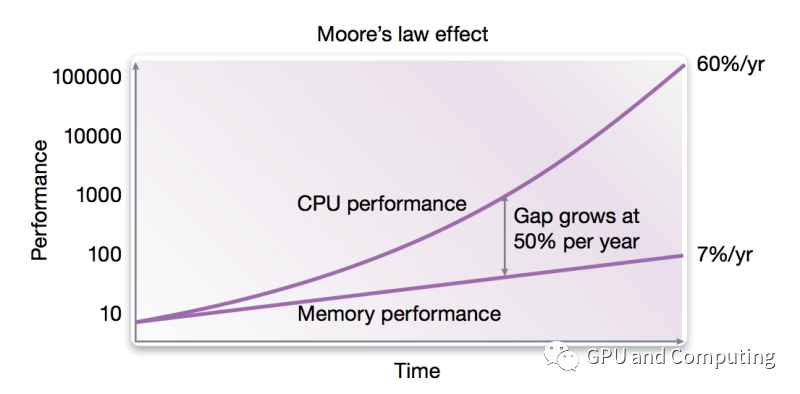

上期我們講了現(xiàn)代計算機體系結構通過處理器(CPU/GPU)和內(nèi)存的交互來執(zhí)行計算程序,處理輸入數(shù)據(jù),并輸出結果。實際上,由于CPU是高速器件,而內(nèi)存訪問速度往往受限(如圖所示,CPU和內(nèi)存的性能差距從上個世紀80年代開始,不斷拉大),為解決速度匹配的問題,在CPU和內(nèi)存之間設置了高速緩沖存儲器Cache。

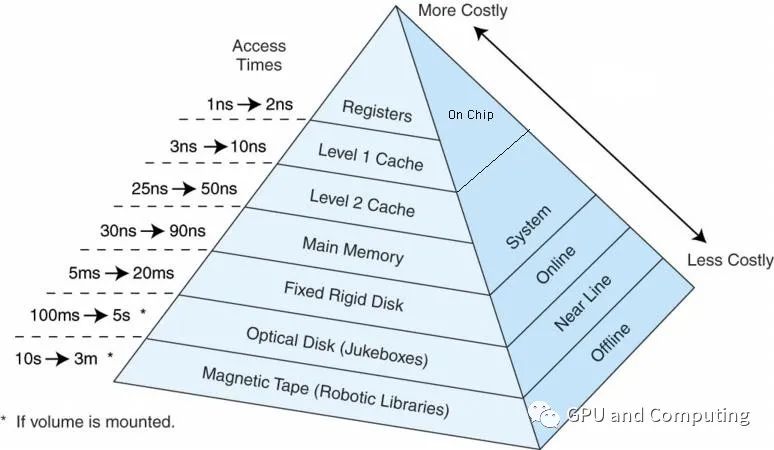

而且Cache往往分幾個層級,與內(nèi)存以及其它外部存儲器共同構成計算機系統(tǒng)的存儲器層次結構(Memory Hierarchy),如下圖所示,使得整個系統(tǒng)在性能,成本和制造工藝達到平衡。

我們可以看到,各個存儲層次在訪問時間上存在數(shù)量級別的差異,訪問速度越快,單位制造成本越高,容量越小。在這里,我們并不打算討論Cache具體設計和實現(xiàn),只是希望針對Cache及其命中率對性能的影響有一個直觀的認識。為了簡化討論問題的復雜性,我們這里做如下假設。

整個流水線分為5個階段,分別為《1》取指、《2》譯碼、《3》運算執(zhí)行、《4》訪存讀寫 (可選)、《5》寫回結果至寄存器。

這里只考慮一級Cache,而且指令、數(shù)據(jù)共享L1 Cache。Cache命中的情況下,每個階段都是1個時鐘(cycle),而cache不命中的情況,階段《1》,《5》各耗時100個時鐘(cycles)。

訪存指令占所有指令1/3。下面我們來分別計算3種情況下的CPI。

= 100 cycles + 3 * (1 cycle) + ((1 cycle * 2/3) + (100 cycles * 1/3))

= 137 cycles.

= (1 cycle * 0.9 + 100 cycles * (1 - 0.9)) + (3 cycles) + ((1 cycle * (2/3 + 0.9/3)) + (100cycles * (1 - 0.9) * 1/3))

= 18.2 cycles.

= (1 cycle * (0.99) + 100 cycles * (1 - 0.99)) + (3 cycles) + ((1 cycle * (2/3 + 0.99/3)) + (100 cycles * (1 - 0.99) * 1/3))

= 6.32 cycles.

Cache完全缺失。

CPI = 《1》階段的時鐘+《2, 3, 5》階段的時鐘+《4》階段的時鐘

Cache命中率達到90%。

CPI = 《1》階段的時鐘+《2, 3, 5》階段的時鐘+《4》階段的時鐘

Cache命中率達到99%

CPI = 《1》階段的時鐘+《2, 3, 5》階段的時鐘+《4》階段的時鐘另外在上期文章里我們也提到同樣32b數(shù)據(jù)的訪問,DRAM的耗能是SRAM的百倍(640pJ vs 5pJ)。完全可見正確配置Cache對高能效高性能計算的重要作用。

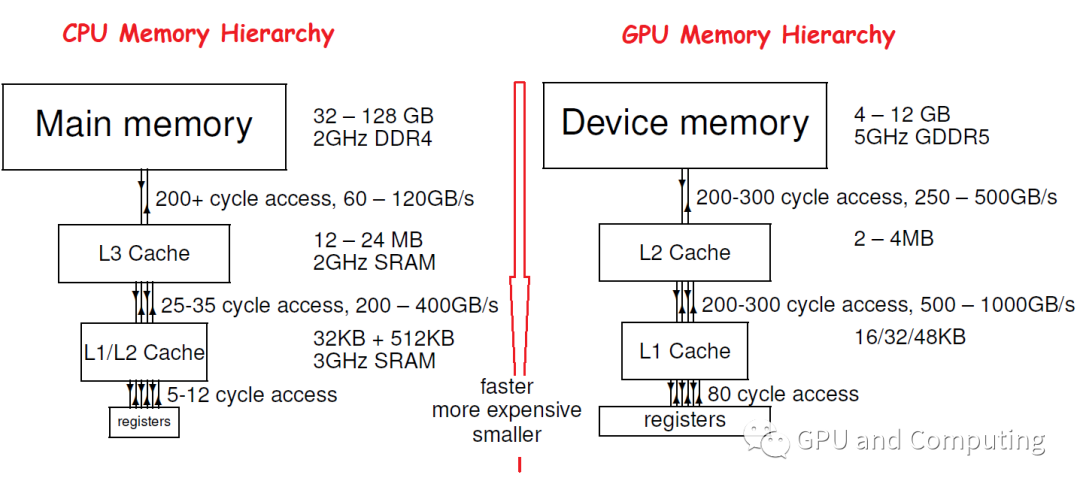

值得一提的是,由于CPU和GPU設計面向的差異,他們的Memory Hierarchy存在明顯的區(qū)別,一個典型的對比如下圖,可以看到GPU的Memeory Hierarchy設計的時候更注意帶寬或者說Throughput,而相比之下對Latency就沒有CPU重視, GPU Cache容量也相對比較小。

那我們不禁要問,GPU的Latency指標這么糟糕,按照我們先前的計算,Cache不命中的后果是不是很嚴重?不過不要擔心,CPU的Cache不命中可能會導致叫停流水線的嚴重后果,而對GPU,只要計算任務量足夠,它的硬件調(diào)度器(Hardware Scheduler)能夠自動在不同的任務間無縫切換,來掩藏特定任務訪問memory帶來的延遲。關于GPU的Latency hiding,值得大書特書,我們以后會詳細討論。

編輯:lyn

-

cpu

+關注

關注

68文章

10854瀏覽量

211587 -

Cache

+關注

關注

0文章

129瀏覽量

28331

原文標題:GPU: 衡量計算效能的正確姿勢(3)

文章出處:【微信號:LinuxDev,微信公眾號:Linux閱碼場】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

相關推薦

芯原推出新一代高性能Vitality架構GPU IP系列

云端超級計算機使用教程

《CST Studio Suite 2024 GPU加速計算指南》

靶式流量計的工作原理 靶式流量計和渦街流量計比較

GPU加速計算平臺是什么

GPU計算主板學習資料第735篇:基于3U VPX的AGX Xavier GPU計算主板 信號計算主板 視頻處理 相機信號

云端超級計算機怎么用

大模型單卡的正確使用步驟

賦能產(chǎn)業(yè)互聯(lián)網(wǎng),高通量計算讓世界更高效!

淺談GPU: 衡量計算效能的正確姿勢(3)

淺談GPU: 衡量計算效能的正確姿勢(3)

評論