隨著5G技術的發展,射頻前端(RFFE)設計變得越來越復雜,而系統級封裝(SiP)技術因其可集成多顆裸芯片與無源器件的特點,開始被廣泛用于射頻前端的設計中。 芯片設計與封裝設計傳統上是由各自工程團隊獨立完成,這樣做的缺陷是增加了迭代時間和溝通成本。如果能夠實現芯片和封裝協同設計,不僅可大幅減少迭代次數,提高設計成功率,而且使能芯片工程師在設計流程中隨時評估封裝性能。 目前在市場上,要實現快速的芯片和封裝協同仿真的方法并不多。芯和半導體獨創的這套聯合仿真流程中,三維建模簡單易用,并配有專門針對聯合仿真的優化求解器,能夠提供更高的仿真加速和仿真效率。

三維建模和仿真流程

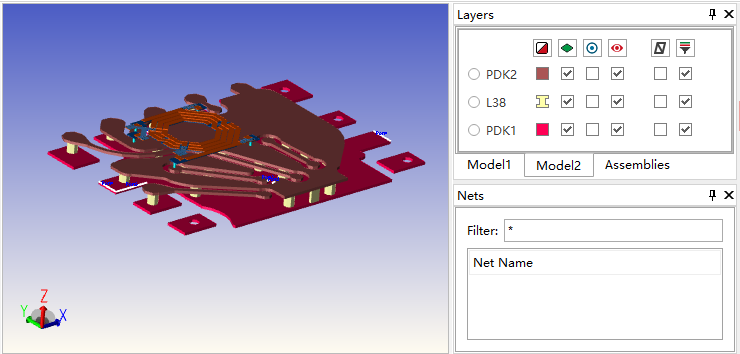

1.導入芯片和封裝版圖文件

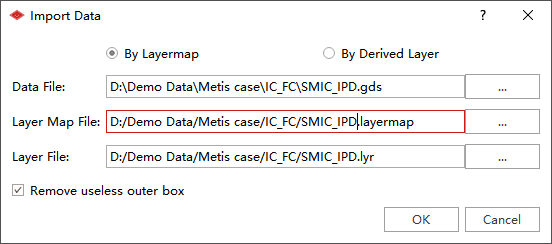

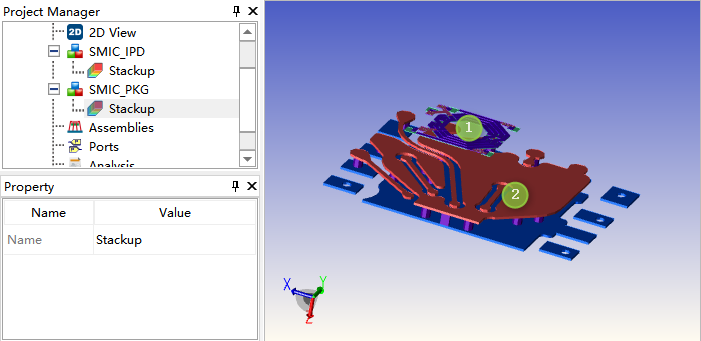

在Metis工具中,可直接導入Cadence的設計文件(.mcm/.sip/.brd)、ODB++文件、以及DXF和GDS文件。本案例中芯片和封裝版圖均為GDS格式,同時還需要layermap文件和仿真工藝信息lyr文件。依次導入芯片和封裝版圖后,在Metis 3D視圖中自動生成了它們的三維結構(圖2),此時它們的相對位置是任意,需要通過Bump將它們連接在一起。

圖1 導入版圖界面

圖2導入芯片和封裝文件

2.模型堆疊

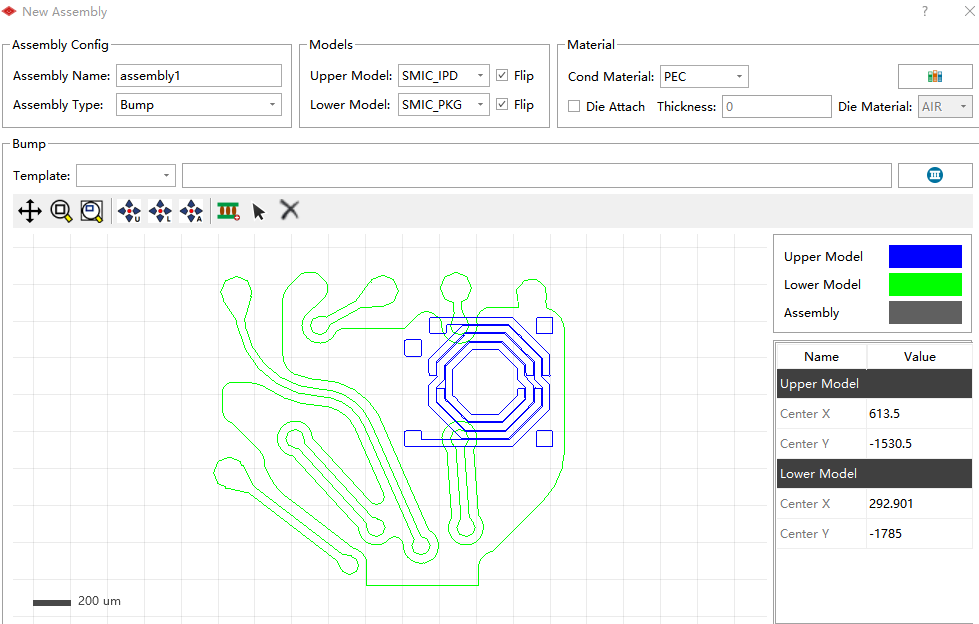

在左側的項目管理欄,選擇Assemblies,進入堆疊設置界面。在上側Model欄,我們將芯片設置為Upper Model,將封裝設置為Lower Model(圖3)。

圖3 切割后的模型 左:Serdes; 右:DDR

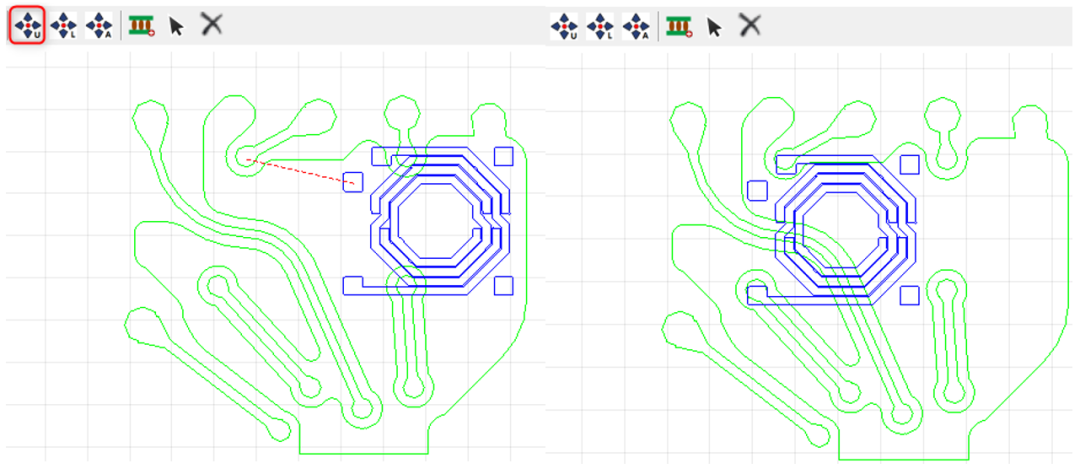

接著我們使用拖拽功能,將Upper Model拖拽至正確的封裝焊點位置(圖4)。

圖4 移動upper Model至正確位置(右圖)

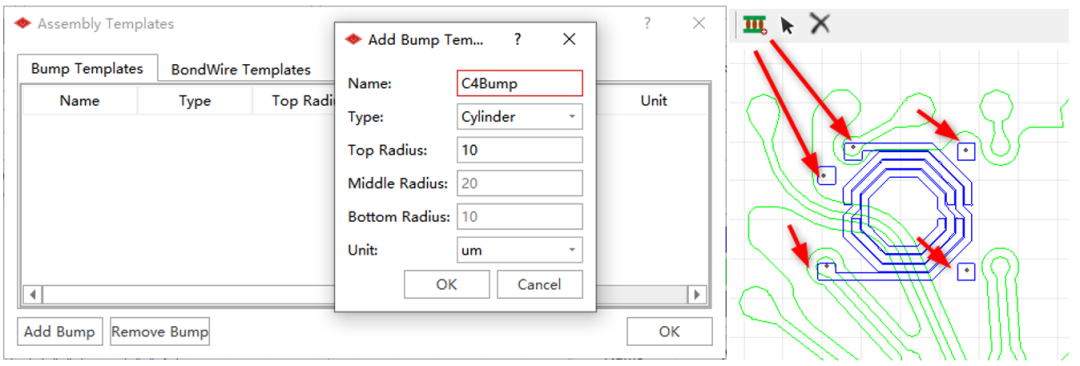

最后創建合適的Bump模型,通過在芯片pad上點擊增加Bump模型,將芯片和封裝結構連接在一起(圖5)。

圖5 Bump建模及添加

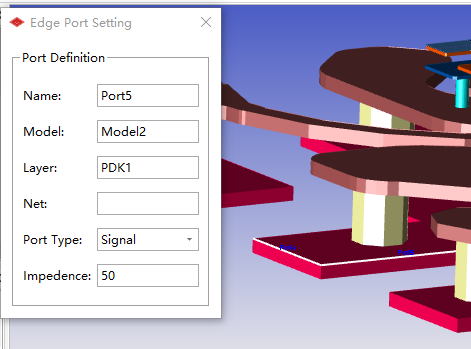

3.端口添加

模型堆疊完畢后,用戶可以直接在3D視圖中添加集總端口,其中信號類型,金屬層次,端口阻抗可任意配置。在本案例中,我們選擇封裝焊盤的一邊作為信號端口。

圖6 疊層及端口管理

圖7 生成的最終仿真模型

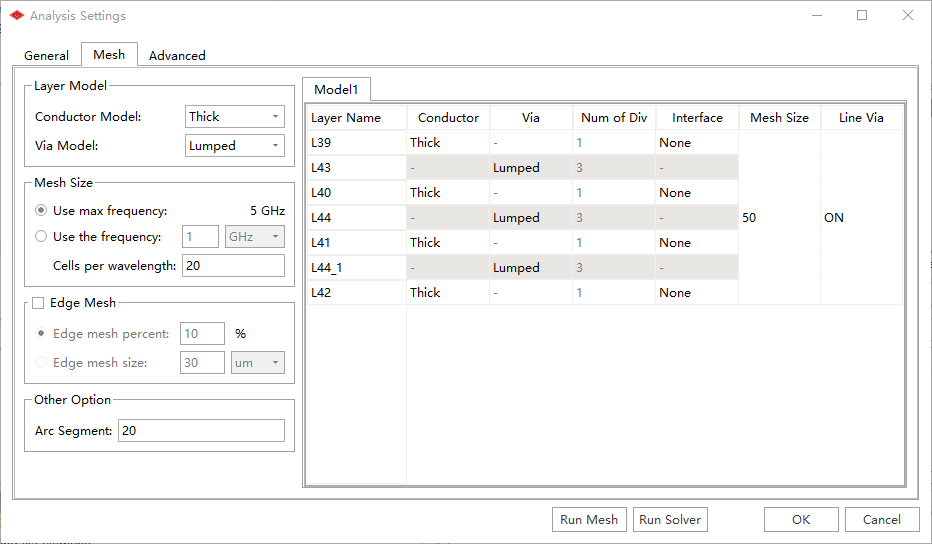

4.仿真環境設置

Metis的網格劃分、金屬和過孔模型可以根據不同的結構進行分開設置,從而達到仿真精度與效率的雙重提升。本案例中芯片的金屬設置為Thick,過孔為Lumped,網格大小為50um,而封裝的金屬設置為3D,過孔為3D,網格大小為200um。最后點擊Run Solver進行聯合仿真。

圖8 芯片的仿真設置

5.仿真結果比對

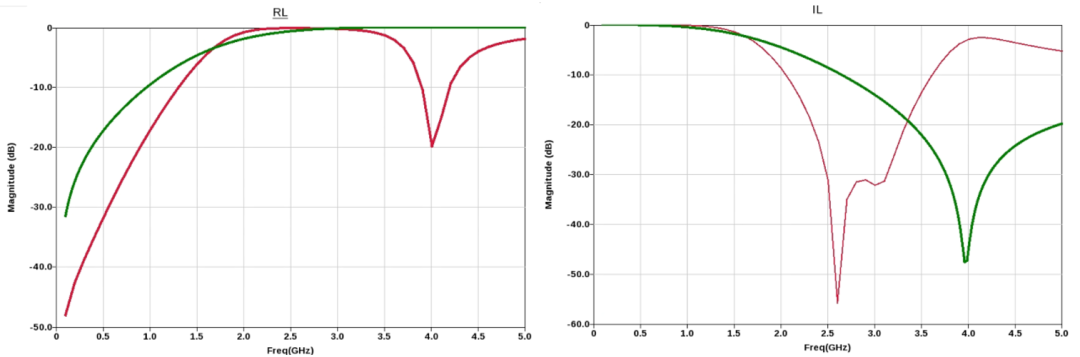

我們分別仿真了不帶封裝和帶封裝兩種應用場景,來分析封裝對芯片濾波特性的影響。綠色曲線是不帶封裝的芯片仿真數據,紅色曲線是帶封裝的芯片仿真數據。通過對比RL和IL兩個指標,我們發現在通帶內濾波器特性并沒有明顯惡化,但是由于封裝的容性寄生,導致帶外的抑制性能急劇下降。這將對射頻系統接收信號和本征信號帶來干擾,從而導致信號的阻塞。由此我們得出結論,封裝效應是芯片設計不得不考慮的重要因素,同時Metis能很好的解決聯合仿真建模困難,優化設計效率低的問題。

圖9 RL與IL比對結果

總結

本文介紹了一種采用芯和半導體的Metis工具實現芯片和封裝聯合仿真的方法。通過Metis分別導入芯片和封裝的版圖文件,將芯片倒裝焊在封裝基板上,建立三維堆疊模型。最后使用Metis進行快速的電磁仿真分析,我們考察了封裝對芯片性能指標的影響。此案例可以幫助設計人員進行芯片和封裝協同設計可大幅減少迭代次數,提高設計成功率,使能芯片工程師在設計流程中隨時評估封裝性能。

編輯:jq

-

芯片

+關注

關注

456文章

50936瀏覽量

424671 -

濾波器

+關注

關注

161文章

7843瀏覽量

178378 -

封裝

+關注

關注

127文章

7941瀏覽量

143093 -

RFFE

+關注

關注

0文章

8瀏覽量

5880

原文標題:怎樣實現 “高效的芯片與封裝的聯合仿真”?

文章出處:【微信號:Xpeedic,微信公眾號:Xpeedic】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

自動駕駛聯合仿真——功能模型接口FMI(終)

康謀分享 | 自動駕駛聯合仿真——功能模型接口FMI(四)

康謀分享 | 自動駕駛聯合仿真——功能模型接口FMI(三)

康謀分享 | 自動駕駛聯合仿真——功能模型接口FMI(二)

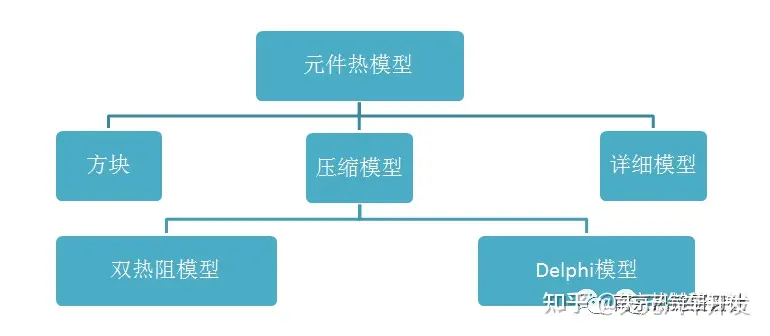

CAE熱仿真中的芯片物性等效建模方法分析

怎樣實現高效的芯片與封裝的聯合仿真?

怎樣實現高效的芯片與封裝的聯合仿真?

評論