這篇文章我們講一下Virtex7上DDR3的測試?yán)蹋琕ivado也提供了一個DDR的example,但卻是純Verilog代碼,比較復(fù)雜,這里我們把DDR3的MIG的IP Core掛在Microblaze下,用很簡單的程序就可以進(jìn)行DDR3的測試。

但這個工程只是一個簡單的測試用例,實際應(yīng)用中不會這么用的,因此傳輸效率太低。

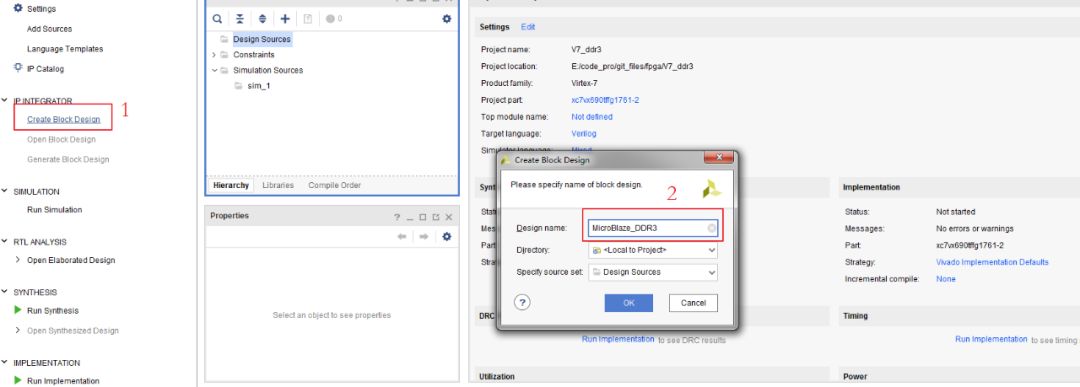

1. 創(chuàng)建Block Design,命名為Microblaze_DDR3。

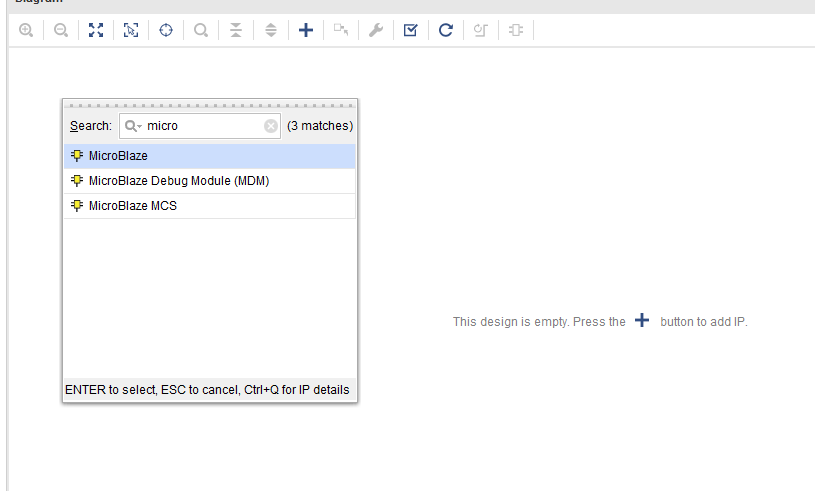

2. 在bd文件中加入Mircoblaze。

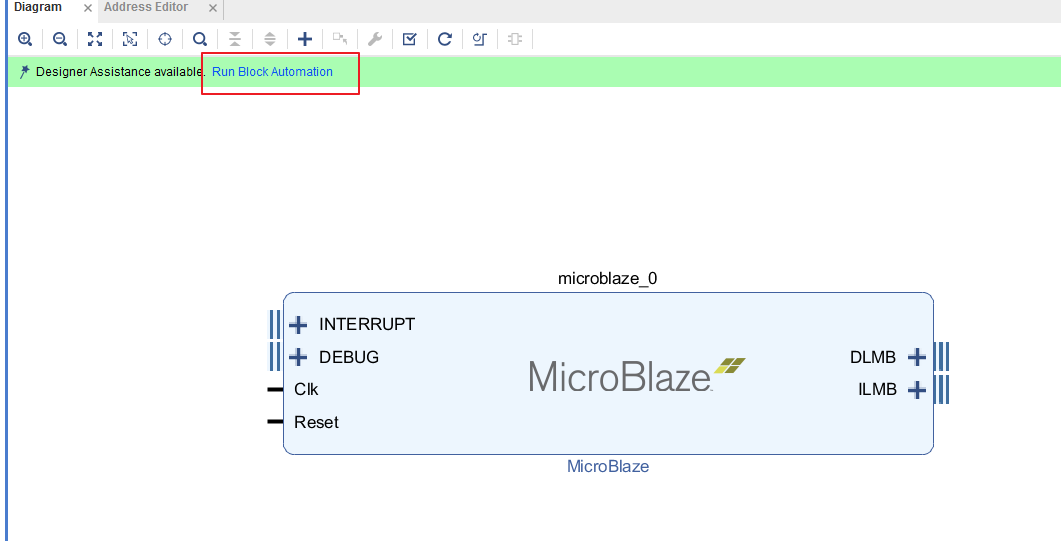

3. 點擊Run Block Automation。

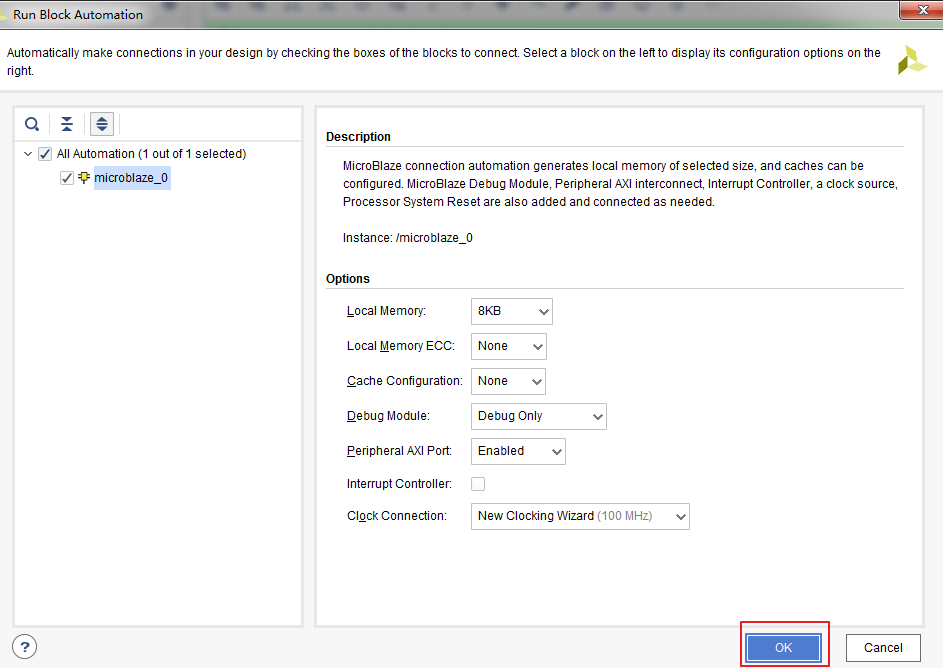

4. 按照默認(rèn)配置,確定即可。

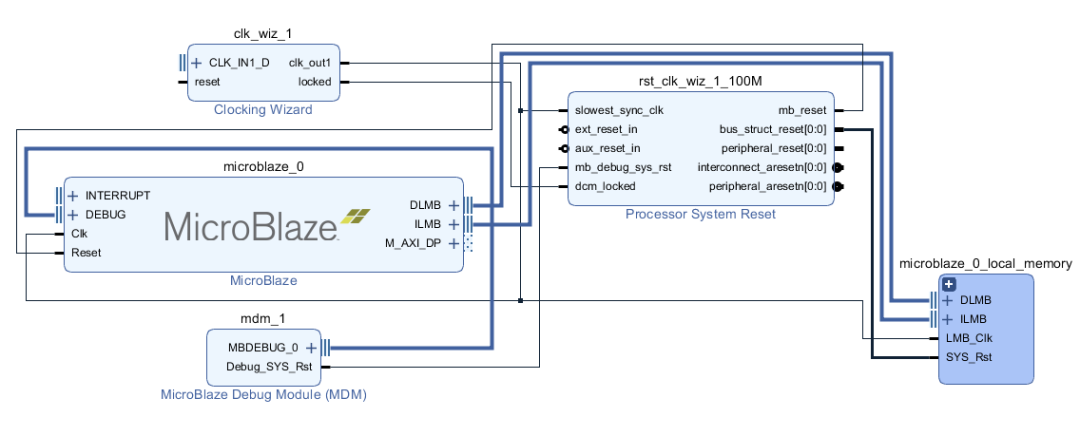

5. 出現(xiàn)下面的界面。

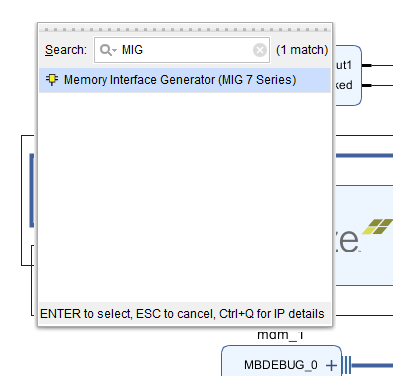

6. 添加MIG的IP Core。

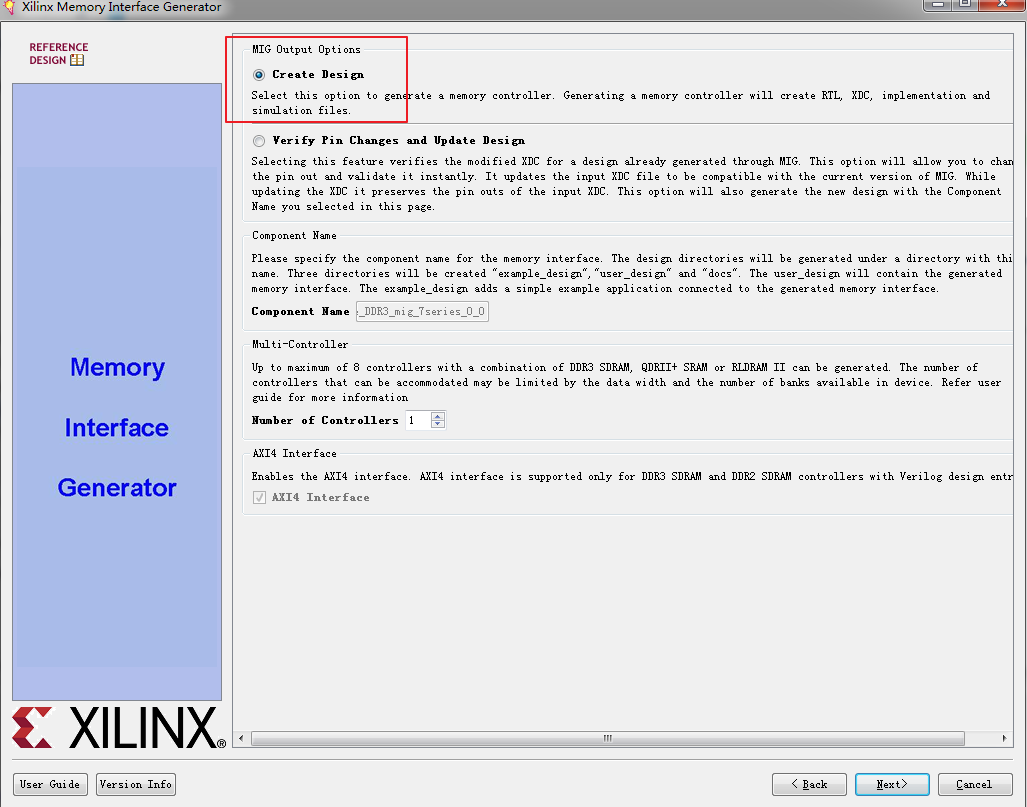

7. 開始配置DDR,選擇Create Design.

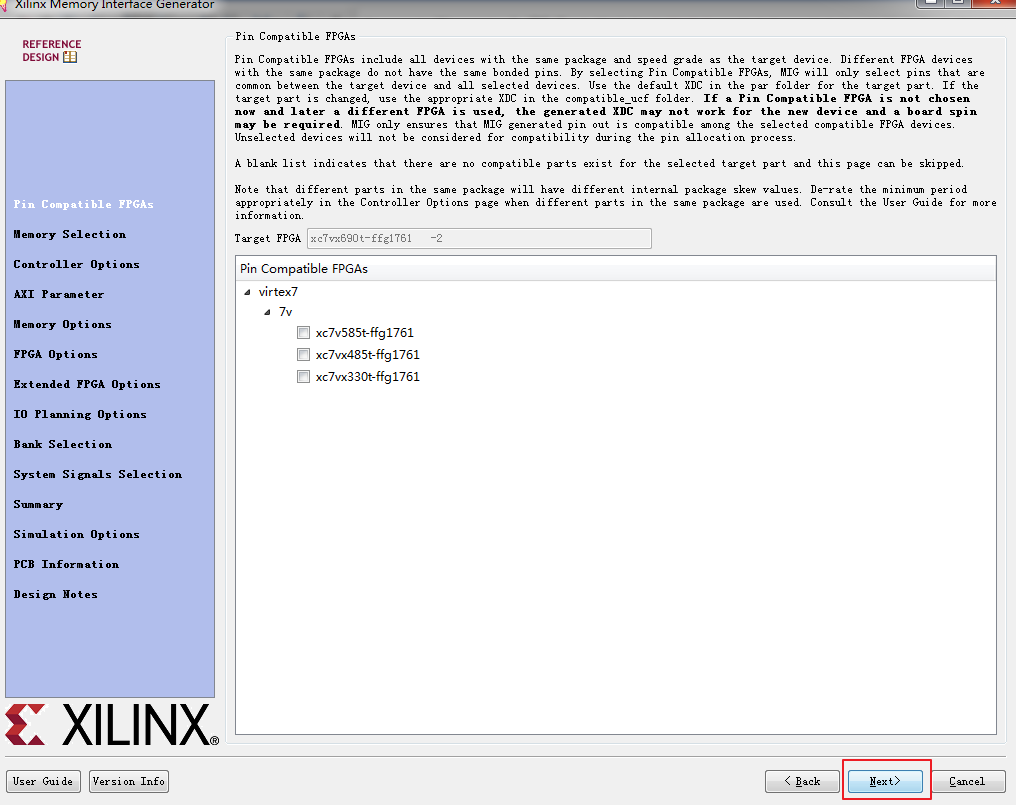

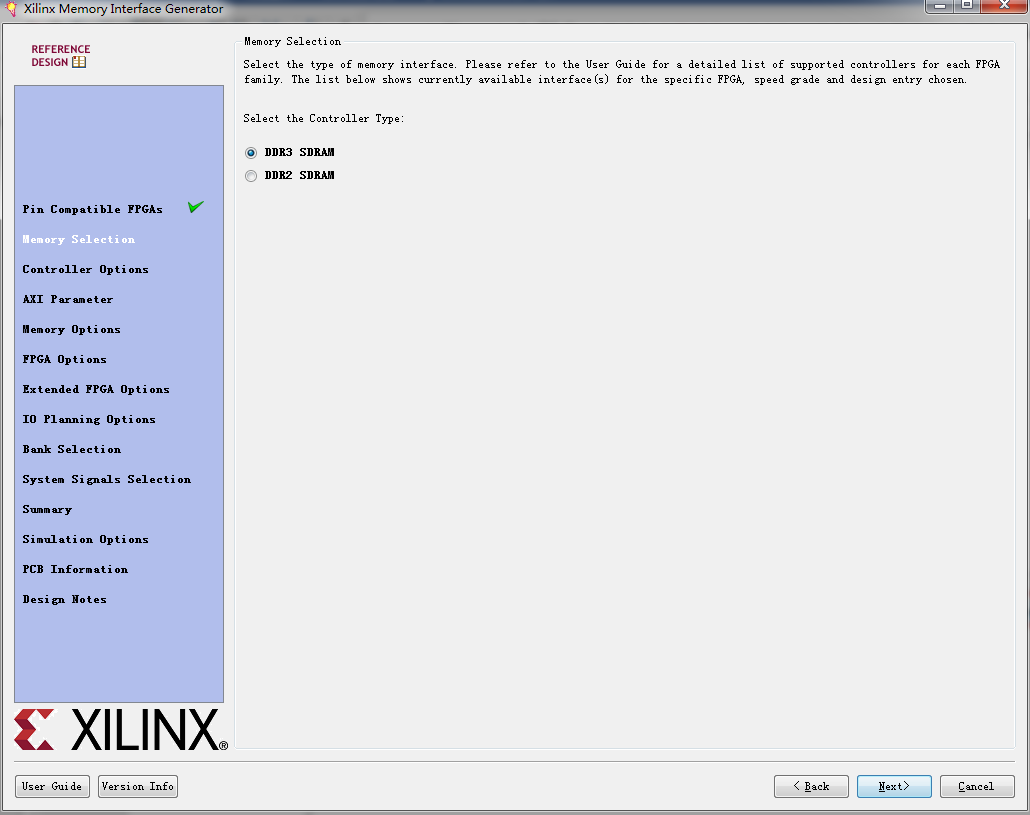

8. 這一步是選擇Pin腳兼容的FPGA,我們不做選擇,直接Next。

9. 選擇DDR3。

10.

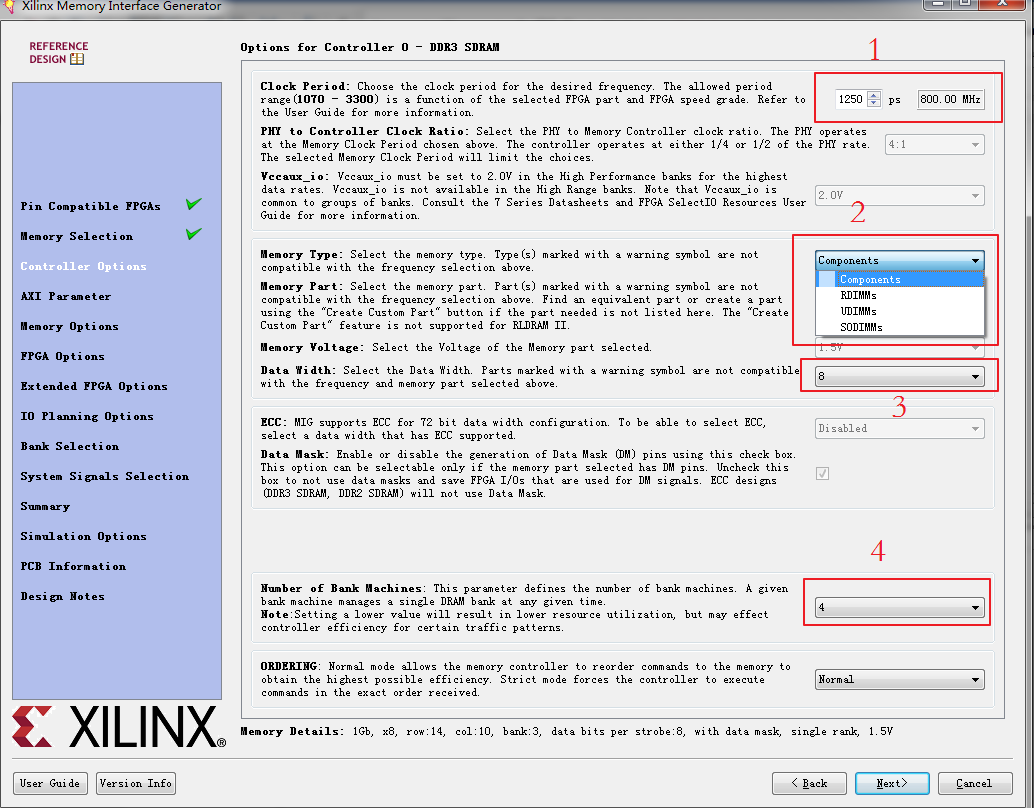

①選擇DDR的工作頻率,我們這里讓DDR3的頻率為1600MHz,所以時鐘頻率是800MHz;

②選擇器件,根據(jù)實際情況來選擇即可;

③數(shù)據(jù)位寬,也是根據(jù)板卡上的實際位寬進(jìn)行選擇;

④默認(rèn)即可。

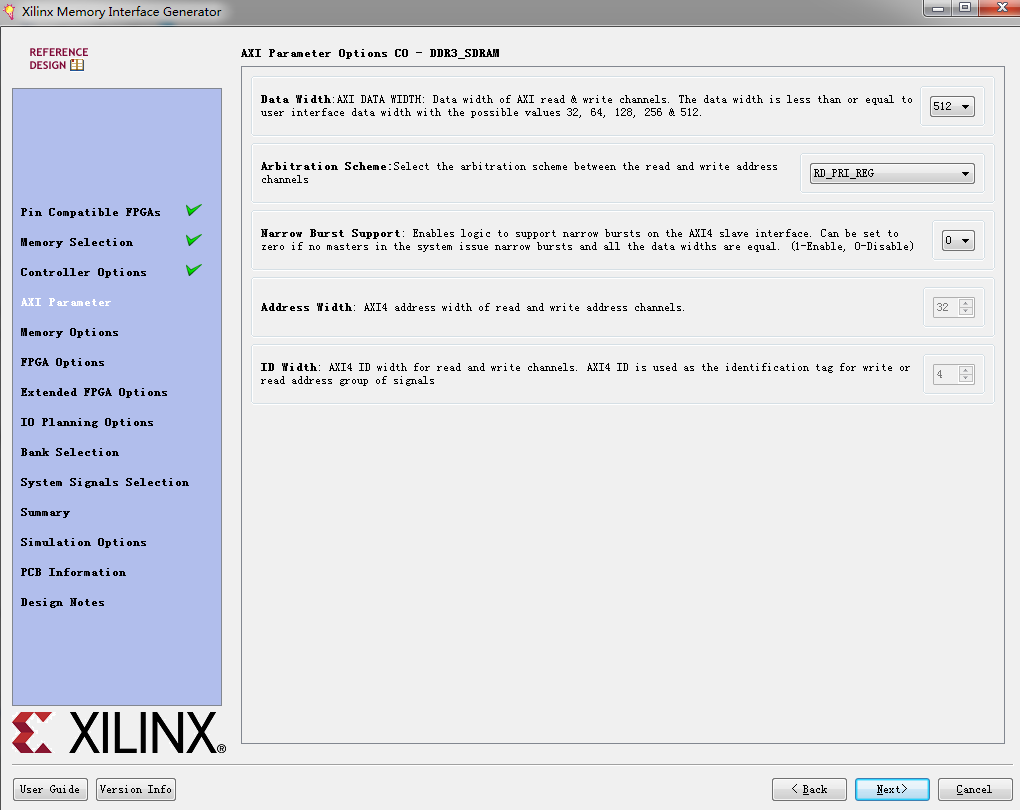

11. 選擇AXI總線的位寬,這里我們選擇512。

12.

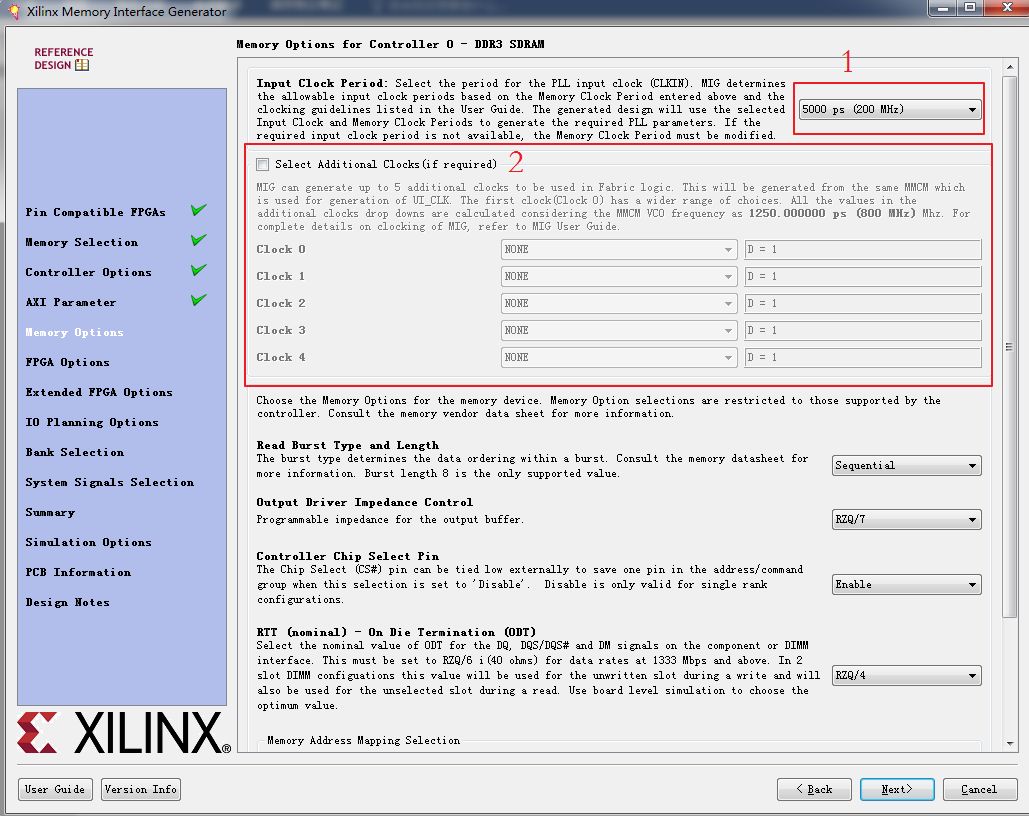

①選擇輸入時鐘頻率,雖然DDR的工作時鐘是800MHz(在第10步中選擇),但我們可以輸入一個低頻時鐘,然后MIG的IP Core中會倍頻到所需頻率。

②MIG的IP Core默認(rèn)會輸出一個200MHz的時鐘,如果還需要其他的時鐘輸出,可以在這里選擇。其他選擇默認(rèn)即可。

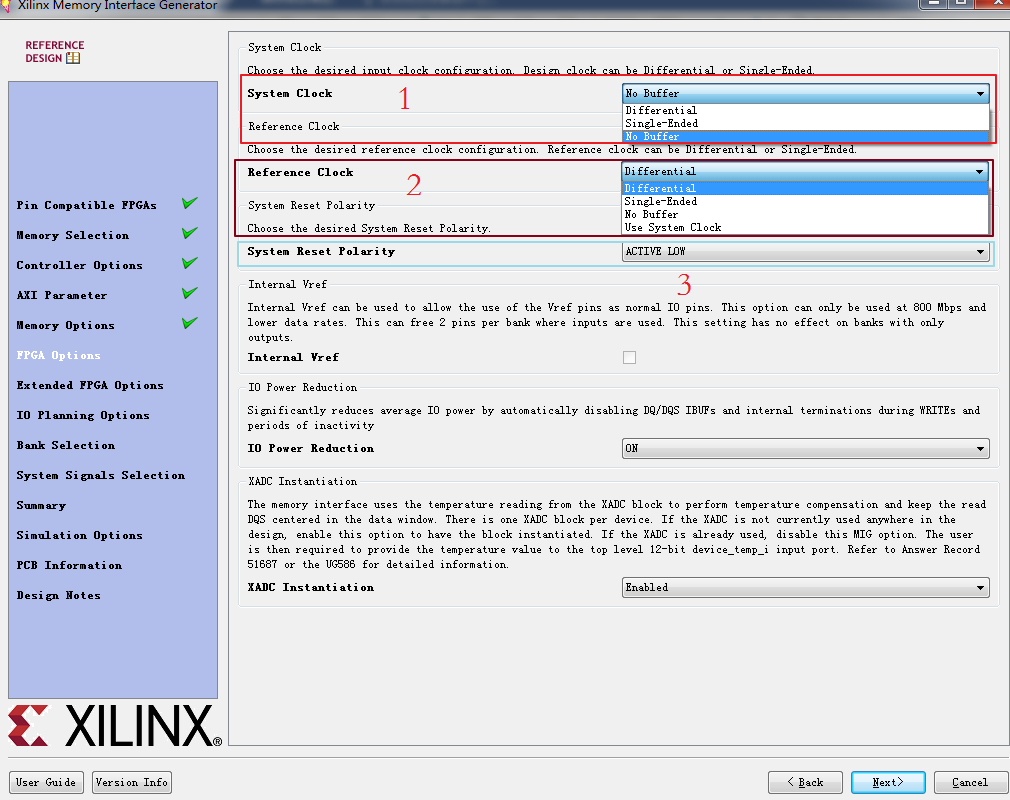

13.

①選擇輸入時鐘的方式,這里的輸入時鐘就是我們上一個頁面中的設(shè)置的200MHz的輸入時鐘,如果選擇差分或單端,則輸入通過FPGA的管腳輸入200MHz時鐘到MIG的IP Core;如果選擇No Buffer,則可以通過FPGA內(nèi)部的MMCM輸出一個200MHz時鐘到MIG;這里我選擇了No Buffer;

②選擇參考時鐘的方式,參考時鐘頻率固定是200MHz,如果選擇如果選擇差分或單端,則輸入通過FPGA的管腳輸入200MHz時鐘到MIG的IP Core;如果選擇No Buffer,則可以通過FPGA內(nèi)部的MMCM輸出一個200MHz時鐘到MIG;如果在前一個頁面中選擇了輸入時鐘頻率是200MHz,則這邊會出現(xiàn)一個Use System Clock的選項,因為此時兩個時鐘頻率是相同的嘛。這里我選擇了Use System Clock;

③設(shè)置輸入復(fù)位信號的極性,這個要特別注意,盡量選擇高有效,因為無論我們選擇高復(fù)位還是低復(fù)位,它的端口名都叫sys_rst,會讓人直觀就覺得是高復(fù)位。我第一次使用時,就沒注意到這個選項,默認(rèn)為低,但在MIG的端口上看到sys_rst這個名字我以為是高有效,結(jié)果DDR一直不通。

(備注:對于絕大多數(shù)的Xilinx的IP,如果是低有效的復(fù)位,端口名字中肯定是有N這個標(biāo)志的)

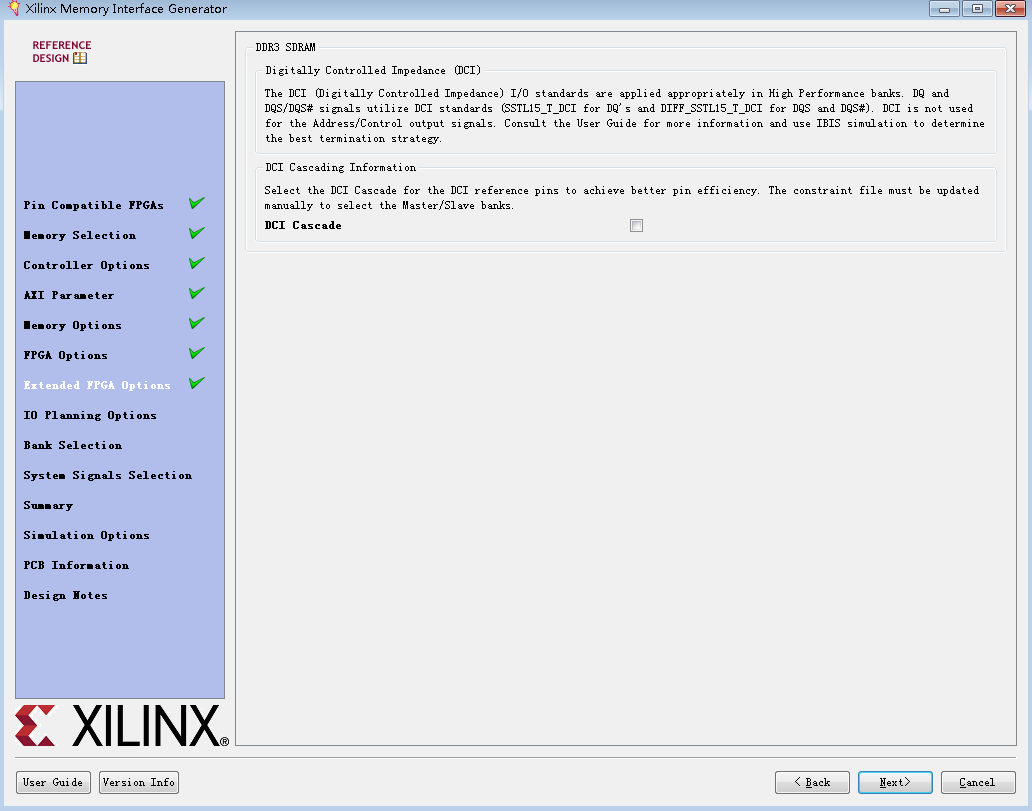

14. 這個頁面不需要操作。

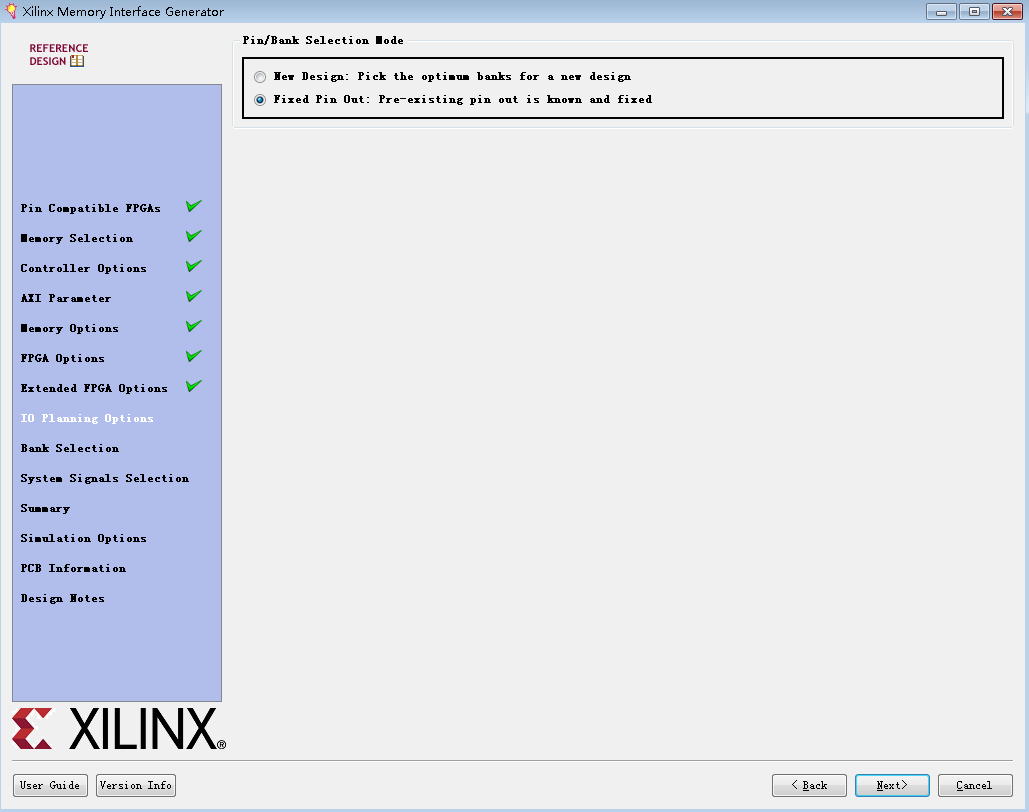

15. 下面開始分配管腳,我比較習(xí)慣于選第二個,無論是第一次分配還是后面再重新分配。

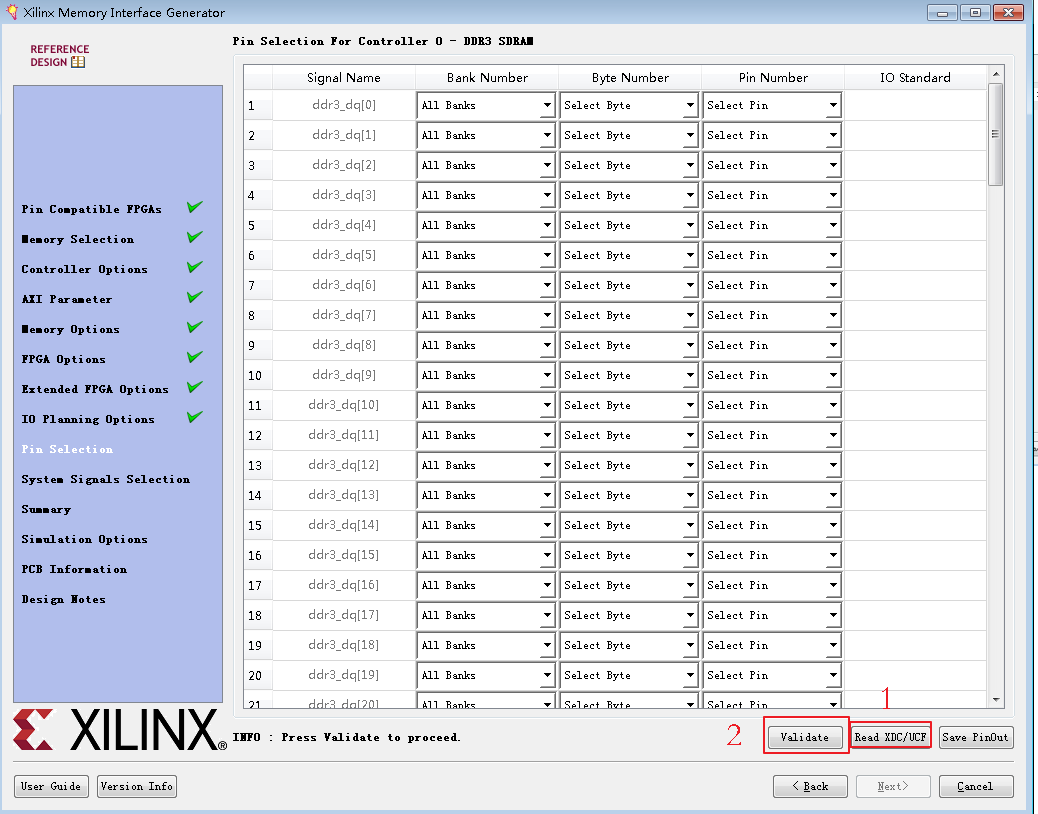

16. 在這一頁,可以根據(jù)原理圖一一分配管腳;如果有現(xiàn)成的xdc/ucf文件,可以直接通過Read XDC/UCF讀入,然后再選擇Validate驗證管腳分配是否正確。

如果Validate成功,則會提示下面的界面。

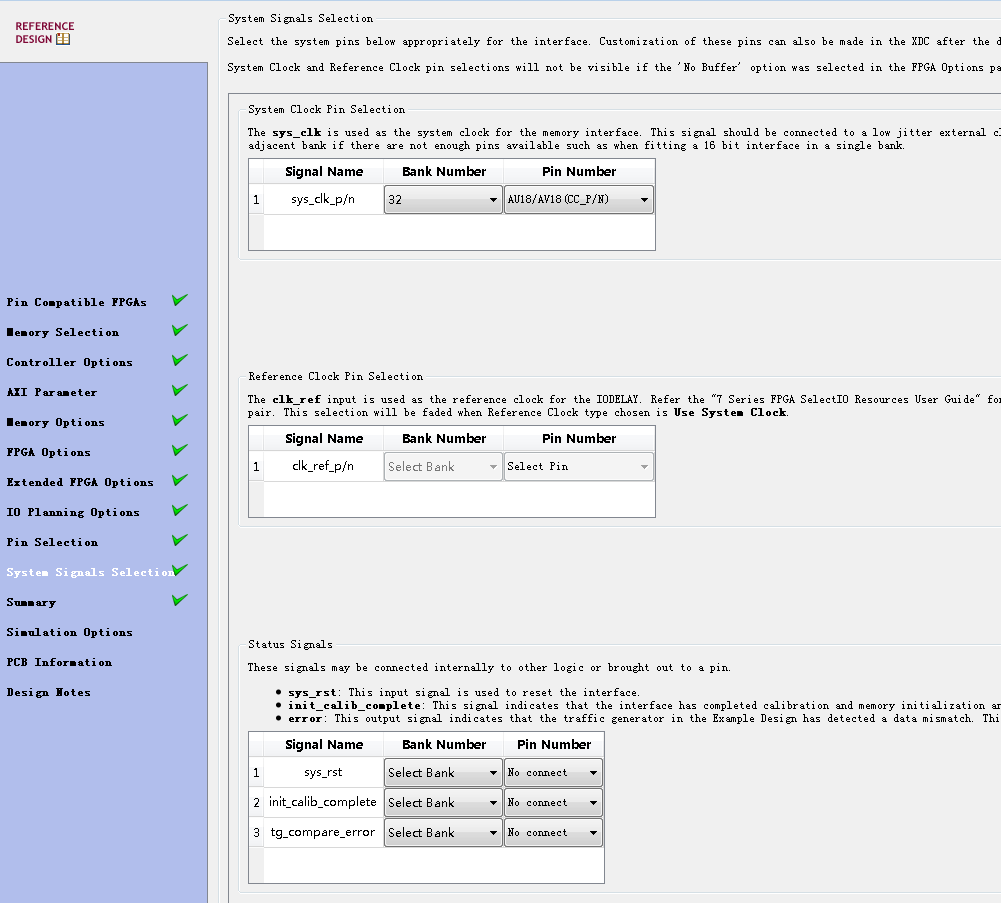

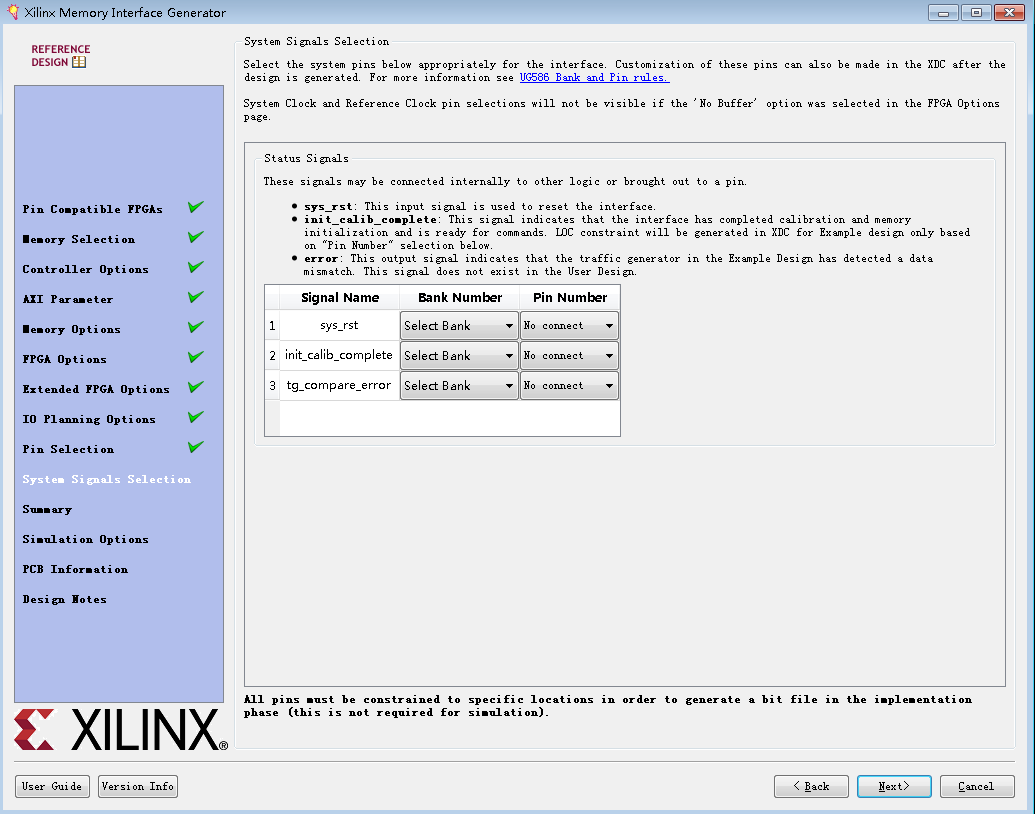

17. 如果在第13步中,選擇了差分或單端輸入,則這里會出現(xiàn)下面第一個圖;如果選擇了No buffer,則這里會出現(xiàn)第二個圖。很容易理解,如果選擇了通過外部管腳輸入時鐘,那這里就是讓選擇具體的管腳。并不是所有的MRCC或者SRCC管腳都可以選的,只能選擇跟DDR管腳同一片區(qū)域的(比如DDR放在了Bank31 32 33,那么這里的時鐘輸入管腳就不能選擇Bank15)。

如果不選擇復(fù)位信號管腳,就可以通過FPGA內(nèi)部邏輯來輸入復(fù)位。

后面一路Next就完成了MIG IP Core的配置了。

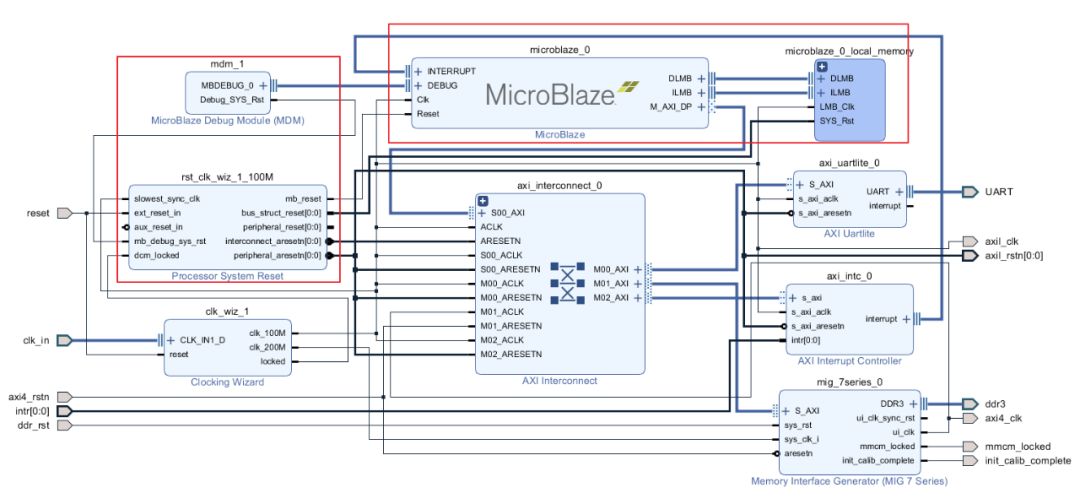

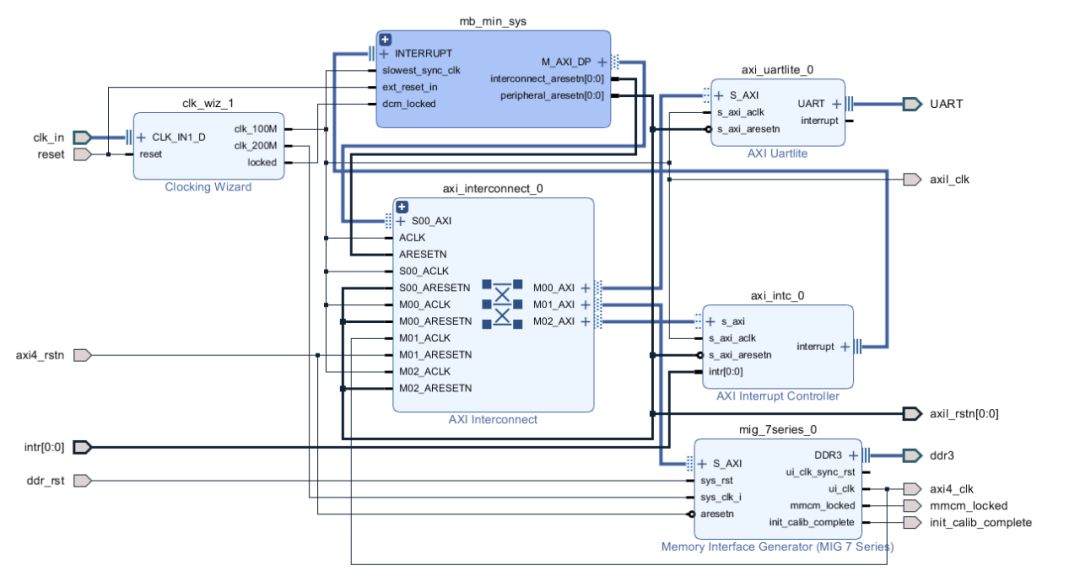

18. 在bd文件中,加入AXI Interconnect、UARTLite和Interrupt(如果不加中斷模塊,Microblaze的程序跑不起來),串口用來打印信息。然后再添加各輸入輸出端口,把內(nèi)部的線連接起來,如下圖所示。

但這個圖里的線太多,看著不直觀,我們把Microblaze模塊、mdm_1、rst_clk_wiz和local_memory模塊(上圖中紅框中的4個模塊)放到一個子模塊中,取名mb_min_sys,如下圖。

19. 創(chuàng)建頂層的top文件,并在top文件中例化bd文件。可以把init_calib_complete和mmcm_locked這兩個信號抓出來,在下載程序后,這兩個信號必須都是高,不然DDR就工作不正常,肯定是中間某個環(huán)節(jié)配置有問題。具體top.v文件內(nèi)容見附錄。

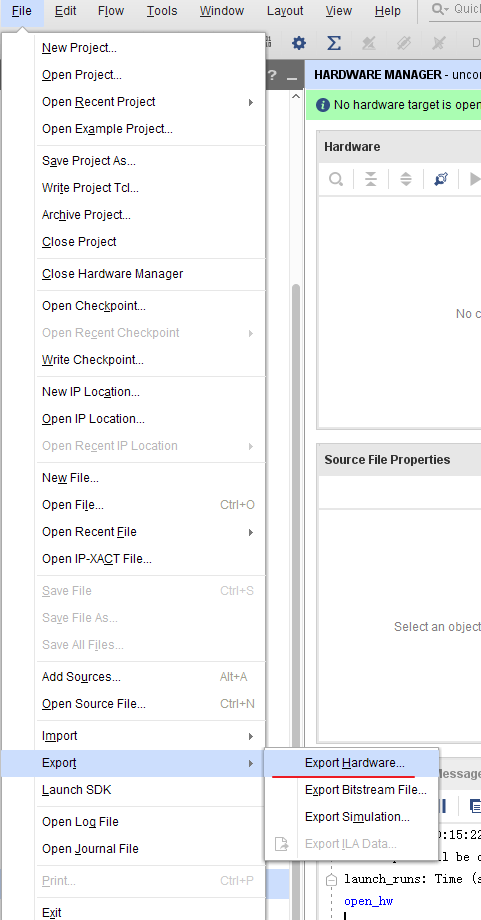

20. 將工程綜合、實現(xiàn)、生成bit文件,并導(dǎo)出Hardware。

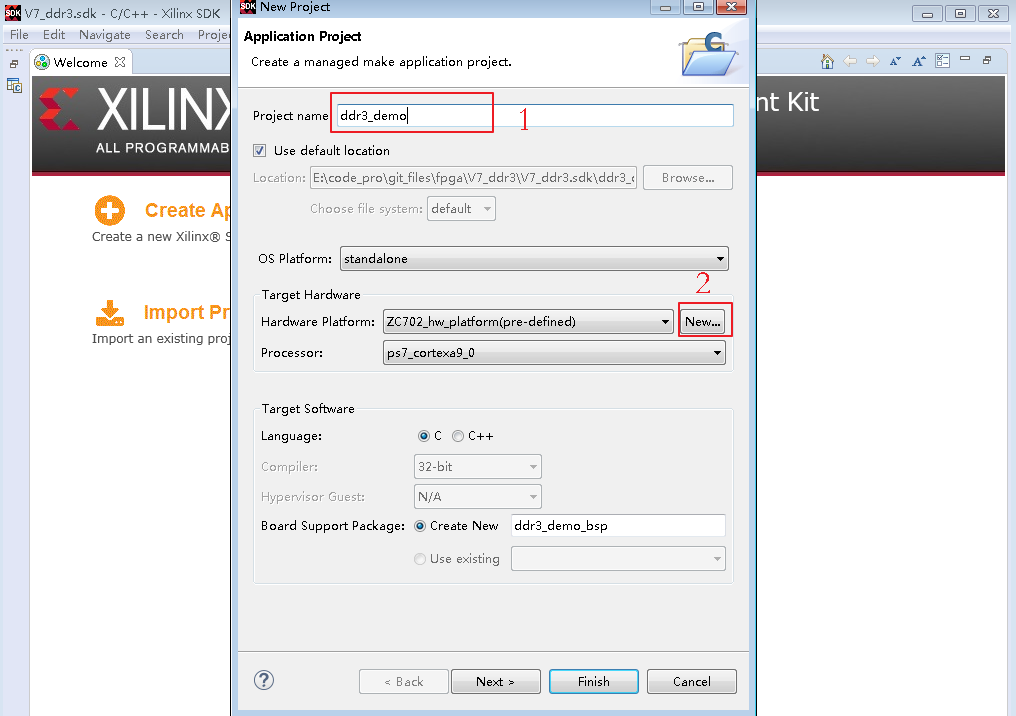

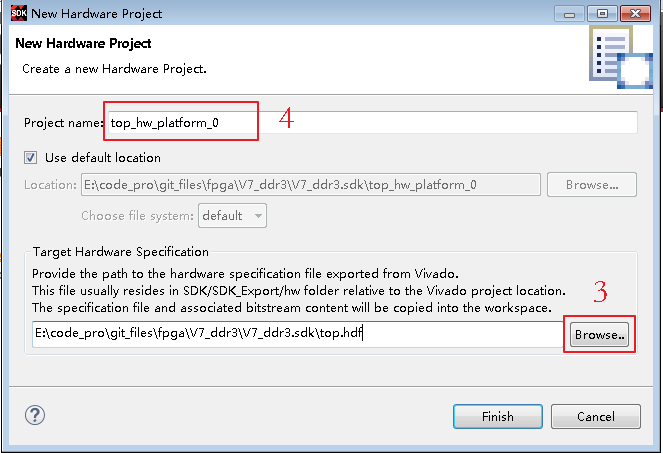

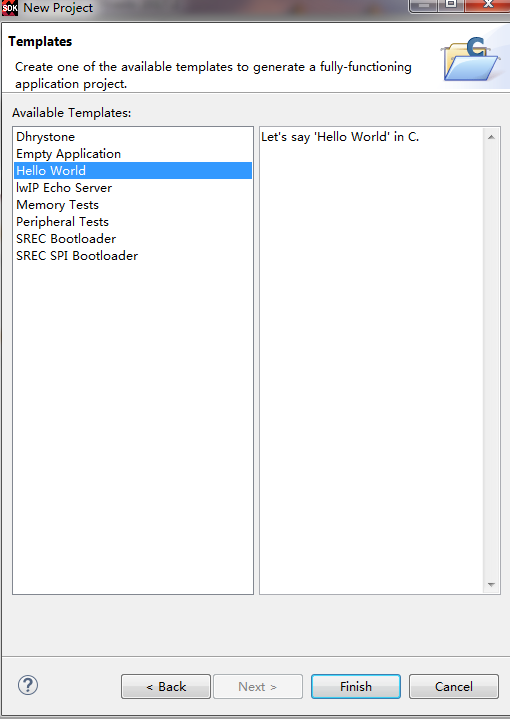

21. 打開sdk,新建Application Project,并按下面的步驟依次操作。

再選擇模板為HelloWorld,最后Finish。

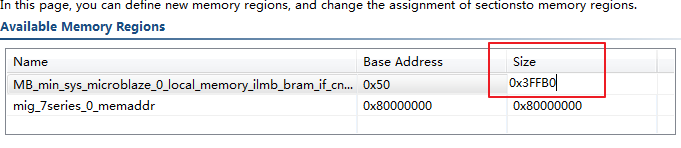

22. 修改helloworld.c,見附錄,重新編譯,如果提示overflowed則把lscript.ld文件中的size改大。

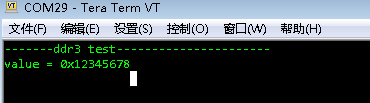

運行程序后,可以看到串口打印信息如下:

說明DDR3可以正常工作。

附錄

top.v

`timescale 1ns / 1ps

module top ( input clk_n, input clk_p, input UART_rxd, output UART_txd, output [15:0]ddr3_addr, output [2:0]ddr3_ba, output ddr3_cas_n, output [0:0]ddr3_ck_n, output [0:0]ddr3_ck_p, output [0:0]ddr3_cke, output [0:0]ddr3_cs_n, output [7:0]ddr3_dm, inout [63:0]ddr3_dq, inout [7:0]ddr3_dqs_n, inout [7:0]ddr3_dqs_p, output [0:0]ddr3_odt, output ddr3_ras_n, output ddr3_reset_n, output ddr3_we_n ); wire axi4_clk; wire axil_clk; reg axi4_rstn; wire axil_rstn; wire init_calib_complete; wire mmcm_locked;

wire ddr_rst;

always @ ( posedge axi4_clk ) begin axi4_rstn 《= axil_rstn; end

reg [8:0] cnt;

always @ ( posedge axil_clk ) begin if(~axil_rstn) cnt 《= ‘d0; else if(cnt==’d256) cnt 《= cnt ; else cnt 《= cnt + 1‘b1; end assign ddr_rst = (cnt==’d256)?1‘b0:1’b1; MicroBlaze_DDR3 MicroBlaze_DDR3_i

(.UART_rxd (UART_rxd ), .UART_txd (UART_txd ), .axil_clk (axil_clk ), .axi4_clk (axi4_clk ), .axi4_rstn (axi4_rstn ), .clk_in_clk_n (clk_n ), .clk_in_clk_p (clk_p ), .ddr3_addr (ddr3_addr ), .ddr3_ba (ddr3_ba ), .ddr3_cas_n (ddr3_cas_n ), .ddr3_ck_n (ddr3_ck_n ), .ddr3_ck_p (ddr3_ck_p ), .ddr3_cke (ddr3_cke ), .ddr3_cs_n (ddr3_cs_n ), .ddr3_dm (ddr3_dm ), .ddr3_dq (ddr3_dq ), .ddr3_dqs_n (ddr3_dqs_n ), .ddr3_dqs_p (ddr3_dqs_p ), .ddr3_odt (ddr3_odt ), .ddr3_ras_n (ddr3_ras_n ), .ddr3_reset_n (ddr3_reset_n ), .ddr3_we_n (ddr3_we_n ), .ddr_rst (ddr_rst ), .init_calib_complete (init_calib_complete ), .mmcm_locked (mmcm_locked ), .reset (1‘b0 ), .axil_rstn (axil_rstn ) );

endmodule

helloworld.c

#include《stdio.h》#include“platform.h”#include“xil_printf.h”

int main(){ init_platform(); print(“-------ddr3test----------------------

”); unsignedint*DDR_MEM = (unsignedint*)XPAR_MIG_7SERIES_0_BASEADDR; //write data to ddr3 *DDR_MEM =0x12345678; //read back unsignedint value =*(unsignedint *)XPAR_MIG_7SERIES_0_BASEADDR; xil_printf(“value= 0x%x

”, value);

cleanup_platform(); return 0;}

編輯:lyn

-

FPGA

+關(guān)注

關(guān)注

1645文章

22034瀏覽量

617815 -

DDR3

+關(guān)注

關(guān)注

2文章

284瀏覽量

43126 -

Virtex-7

+關(guān)注

關(guān)注

0文章

31瀏覽量

17369

原文標(biāo)題:Virtex7 Microblaze下DDR3測試

文章出處:【微信號:HXSLH1010101010,微信公眾號:FPGA技術(shù)江湖】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

【RK3568+PG2L50H開發(fā)板實驗例程】FPGA部分 | DDR3 讀寫實驗例程

在Vivado調(diào)用MIG產(chǎn)生DDR3的問題解析

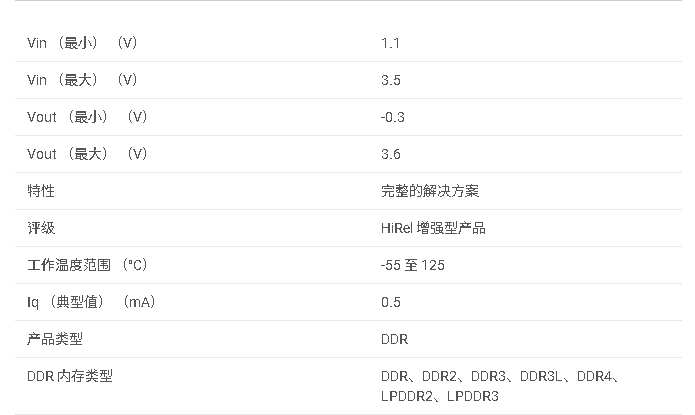

TPS51116 完整的DDR、DDR2、DDR3、DDR3L、LPDDR3 和 DDR4 電源解決方案同步降壓控制器數(shù)據(jù)手冊

DDR模塊的PCB設(shè)計要點

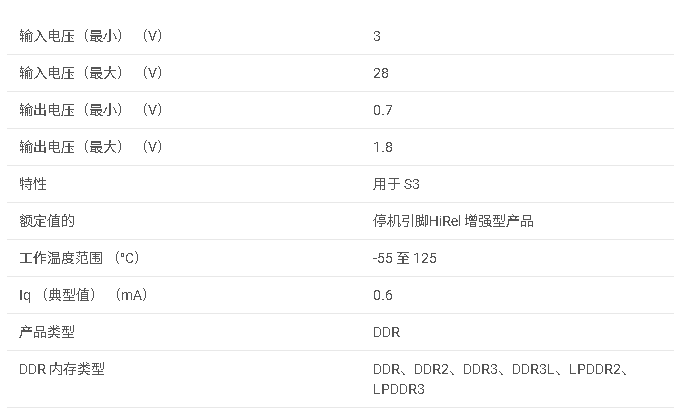

TPS51216-EP 增強型產(chǎn)品 完整的 DDR2、DDR3 和 DDR3L 內(nèi)存電源解決方案 同步降壓控制器數(shù)據(jù)手冊

TPS51200-EP 灌電流/拉電流 DDR 終端穩(wěn)壓器數(shù)據(jù)手冊

DDR3 SDRAM配置教程

燦芯半導(dǎo)體推出DDR3/4和LPDDR3/4 Combo IP

初次使用XC7A35T-FGG484做設(shè)計,用的是25MHZ有源晶振,有源晶振3.3V供電,DDR3的供電1.35V,現(xiàn)在接上晶振后,DDR3的供電變成1.8V

DDR內(nèi)存控制器的架構(gòu)解析

三大內(nèi)存原廠或?qū)⒂?025年停產(chǎn)DDR3/DDR4

DDR3、DDR4、DDR5的性能對比

如何選擇DDR內(nèi)存條 DDR3與DDR4內(nèi)存區(qū)別

DDR3寄存器和PLL數(shù)據(jù)表

圖形圖像硬件加速器卡設(shè)計原理圖:270-VC709E 基于FMC接口的Virtex7 XC7VX690T PCIeX8 接口卡

關(guān)于Virtex7上DDR3的測試?yán)淘斀?/h1>

關(guān)于Virtex7上DDR3的測試?yán)淘斀?/h1>

評論