無人機系統對于地面站發送的控制信號以及飛行器傳回的姿態數據有著極高的實時性、可靠性與穩定性要求,這對無人機通信系統設計提出了新的挑戰。對于采用ARM作為微處理器的無人機系統來說,系統往往需要協調基于ARM處理器的高速陀螺儀模塊與相對低速的外部無線數據傳輸模塊間的工作。在通信高穩定性與低誤碼率的要求下,處理器不得不花時間運行空操作來等待外部相對低速的傳輸模塊完成一幀數據的收/發。由于等待所浪費的處理器運算周期無形中降低了整個飛控系統的實時性,進而帶來許多潛在的不穩定因素。

本設計結合無人機系統發展需求,采用FPGA FIFO[1]作為高速數據緩沖,提出一種基于FPGA內建FIFO的無人機陀螺儀前級通信接口。通過高速異步FIFO緩沖,將無人機陀螺儀姿態數據經由FPGA準確無誤地發送給地面站,保證了傳輸質量,架起了高速芯片與低速設備之間溝通的橋梁。

1 FPGA內建FIFO的基本工作原理

FIFO即先進先出隊列,采用環形存儲電路結構,是一種傳統的按序執行方法。先進入的指令先完成并引退,隨后才執行第二條指令,是一種先進先出的數據緩存器。根據FIFO的讀寫時鐘頻率是否相同,可將FIFO分為同步FIFO與異步FIFO[2]。FIFO的應用可以很好地協調不同時鐘、不同數據寬度數據的通信,滿足高/低速時鐘頻率要求。與普通存儲器相比,FIFO沒有外部讀寫地址線,使用方便。

本文設計采用FPGA異步FIFO連接基于ARM處理器的高速無人機陀螺儀模塊與相對低速的無線數據傳輸外設。從硬件的觀點來看,FIFO實質上就是一塊數據內存。異步FIFO采用2個時鐘信號控制其讀寫操作,分別為寫時鐘(wrclk)和讀時鐘(rdclk)。一個用來寫數據,即將數據存入FIFO;另一個用來讀數據,即將數據從FIFO中取出。

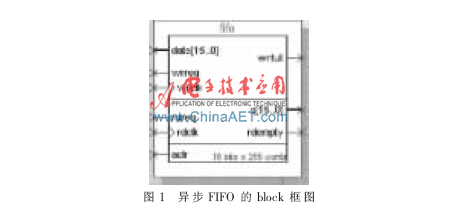

與FIFO操作相關的有兩個指針:寫指針指向要寫的內存部分;讀指針指向要讀的內存部分。FIFO控制器通過外部的讀寫信號控制這兩個指針移動,并由此產生FIFO空信號或滿信號。讀寫時鐘相互獨立設計,有效地保證了FIFO兩端數據的異步通信,其模塊框圖[3]如圖1所示。其中,異步FIFO模塊共有9個端口,分別為數據輸入(datda[15..0])、寫請求(wrreq)、寫時鐘(wrclk)、緩沖器滿信號(wrful)、讀請求(rdreq)、讀時鐘(rdclk)、數據讀出(q[15..0])、緩沖器空信號(rdempty)、緩沖器清空信號(aclr)。

2 基于ARM的無人機陀螺儀接口結構

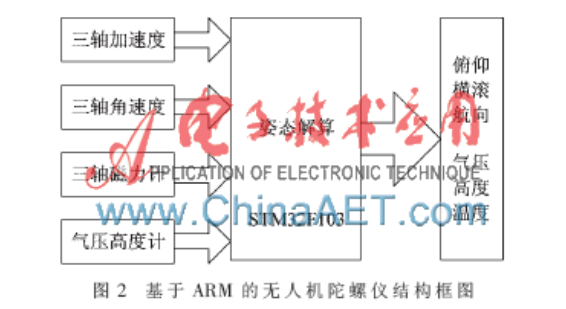

由于機載燃油和電能儲備的制約,無人機載設備要求小巧輕便,能效比高,因此對芯片的選型及電路結構提出了較高的要求。綜合穩定性、數據精度、工作溫度、封裝體積以及能耗等各方面因素,對無人機陀螺儀傳感器經行嚴格篩選,確定了如圖2所示的陀螺儀方案。

無人機陀螺儀的主控芯片選用ARM 32 bit CortexTM M3內核的STM32F103T8處理器。其內建64 KB的閃存存儲器和20 KB的運行內存,以及7通道的DMA、7個定時器、2個UART端口等。通過板載的8 MHz晶體和STM32內部的PLL,控制器可以運行在72 MHz的主頻上,為姿態解算[4]提供強大的硬件支持。

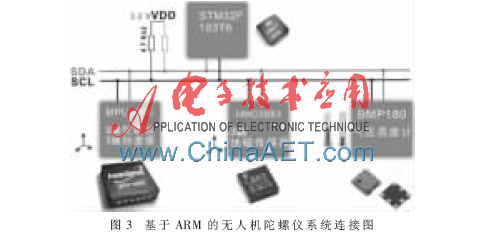

三軸加速度與三軸角速度傳感器采用Invensense公司的MPU-6050單芯片方案,此芯片為全球首例整合性6軸運動處理組件,相比其他多芯片實現方案,免除了整合陀螺儀與加速度器軸間差的問題,大大減少了封裝空間。

三軸磁力計采用Honeywell公司的HMC5883L芯片,此芯片內部采用先進的高分辨率HMC188X系列磁阻傳感器與行業領先的各向異性磁阻技術(AMR),具有軸向高靈敏度和線性高精度的特點,測量范圍從毫高斯到8高斯(gauss),穩定可靠。

氣壓傳感器采用博世公司的BMP180芯片,該芯片性能卓越,絕對精度可以達到0.03 hpa,并且功耗極低,只有3 ?滋A。傳感器采用強大的7 pin陶瓷無引線芯片承載(LCC)超薄封裝,安裝使用方便。各傳感器與ARM處理器采用I2C總線連接,示意圖如圖3所示。

3 FPGA FIFO與陀螺儀的連接

結合無人機ARM陀螺儀的特點,為了適應過程的復雜性,實現操作的簡便性,設計選用Altera公司的CycloneII系列芯片EP2C8Q208C8N,在QuartuesII平臺上進行Verilog代碼設計,使用Altera公司提供的FIFO IP核[5]。此方案穩定高效,易于開發。

3.1 陀螺儀與FIFO及FPGA的連接

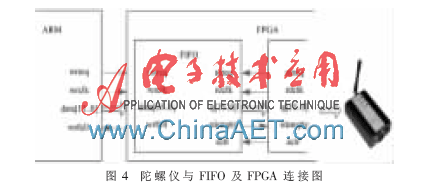

處理器采集各傳感器信號,在ARM內部進行姿態解算,進而得到俯仰角、橫滾角、航向角、氣壓、高度和溫度信息。為了及時將解算得到的數據發送回地面站,處理器控制寫請求信號wrreq和寫時鐘wrclk將這些數據高速寫入FIFO,然后回到飛行控制程序,進行下一周期的姿態解算。FIFO在數據寫滿后,寫滿標志位wrfull會置高電平,ARM處理器通過檢測寫滿標志位的狀態來判斷是否繼續寫入數據。

與此同時,在FPGA中通過檢測所讀取FIFO是否為空標志位rdempty來判斷是否繼續讀取數據。讀空標志位為低電平代表FIFO中有數據,可以讀取,則配合讀請求信號rdreq和讀時鐘rdclk及時讀取數據,直到將數據全部讀出,標志位變為高電平,此時FIFO中已經沒有數據。基于ARM的陀螺儀與FIFO及FPGA的連接如圖4所示。

3.2 FIFO的配置與讀寫操作

針對上述ARM陀螺儀接口特點,對FIFO進行配置如下。

FIFO Width : 16 bit

FIFO Depth : 2 048 words

Synchronize reading and writing clock : YES

Asynchronous clear : YES

設計采用位寬為16 bit、深度為2 048且帶有同步清零端[6]的異步FIFO結構,其寫時序與讀時序分別如圖5、圖6所示。

狀態機跳轉部分控制代碼如下:

always@(posedge SYSCLK or negedge RST )

begin

if(!RST)

state 《= idle;

else

case(state)

idle:

begin

data[15:0] 《= 16′d0;

wrreq 《= 1′b1;

rdreq 《= 1′b0;

aclr 《= 1′b0;

state 《= write;

end

read:

if(rdempty != 1′b1 && rdreq ==1′b1)

read_start 《= 1′b1;

else

begin

read_start 《= 1′b0;

wrreq 《= 1′b1;

state 《= idle;

end

write:

if(wrfull!= 1′b1 && wrreq == 1′b1)

write_start 《= 1′b1;

else

begin

write_start 《= 1′b0;

rdreq 《= 1′b1;

state 《= read;

end

default: state 《= idle;

endcase

end

4 系統仿真效果

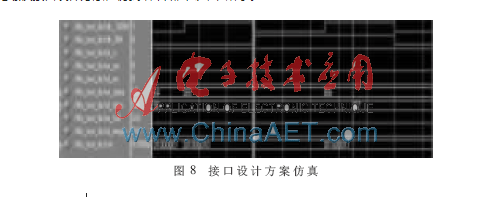

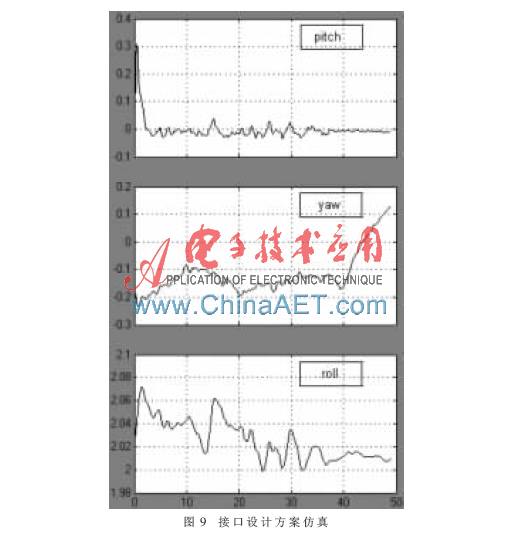

綜合運用QuartuesII[9]與ModelSim SE[10]先進仿真工具,結合FPGA內建FIFO與基于ARM的無人機陀螺儀接口設計方法,仿真結果如圖8、圖9所示。

從圖8中仿真結果得知,在寫入時鐘頻率為100 MHz、寫滿標志位為低電平時,待寫入數據data在每個寫入時鐘上升沿來臨后被準確寫入FIFO的存儲區;隨后在讀出時鐘頻率為5 MHz且讀空標志位為低電平的情況下,待讀出數據q在每個讀時鐘上升沿來臨后被正確讀出,系統讀寫數據穩定準確,符合設計需求。

圖9為通過此通信接口讀取得到的無人機飛行姿態數據,包括俯仰角、偏航角、滾轉角,以圖表形式予以顯示。數據精度與實驗結果理想,驗證了FPGA與ARM無人機陀螺儀數據接口設計方案穩定可靠。

本文提出了基于FPGA內建FIFO與ARM的無人機陀螺儀數據接口設計方法,解決了無人機ARM處理器與相對低速無線發送模塊直接數據傳輸時傳輸速度不匹配的難題,實現了ARM處理器將無人機姿態數據高速寫入FIFO后就可以立即返回、無需等待的功能,節約了處理器資源,使得無人機系統的可靠性與穩定性得到大幅提升。仿真驗證表明,讀寫數據準確無誤,顯著提高了數據傳輸速度與數據質量,證明了本方案的可行性與正確性。面對高速數據傳輸的需求,該系統還可廣泛應用于其他需要高無線數據傳輸的領域,有較高的理論意義和應用價值。

參考文獻

[1] 秦鴻剛,劉京科,吳迪。基于FPGA的雙口RAM實現及應用[J]。電子工程設計,2010,2(2):72-74.

[2] 夏宇聞.Verilog數字系統設計教程[M]。北京:北京航空航天大學出版社,2008.

[3] BAKER R J,LI H W,BOYEE D E.CMOS電路設計布局與仿真[M]。陳中建,譯。北京:機械工業出版社,2006.

[4] PAVLLOV A.CMOS SRAM circuit design and parame tric test in Nano-Scaled technologies[M].New York:Springer,2008.

[5] 單立超,謝雪松。基于FPGA的一種可變幀數字分接技術[J]。電子技術應用,2013,32(2):27-30.

[6] 何濤。基于軟硬件協同技術的FPGA測試平臺設計及測試實現[D]。成都:電子科技大學,2009.

[7] 徐國強,張萌。基于FPGA的高性能視頻信號采集系統設計與實現[J]。微型機與應用,2012,31(6):72-75.

[8] BRIAN D,ANDREW S,CHAN K.RAM with configurable depth and width[P].US:6578 104.1 8.22,June 2003.

編輯:jq

-

FPGA

+關注

關注

1629文章

21729瀏覽量

603049 -

ARM

+關注

關注

134文章

9088瀏覽量

367412 -

fifo

+關注

關注

3文章

387瀏覽量

43655

發布評論請先 登錄

相關推薦

陀螺儀x軸和y軸的應用

解析愛普生(EPSON)陀螺儀傳感器XV-3510CB

探究FPGA與ARM的無人機陀螺儀數據接口設計

探究FPGA與ARM的無人機陀螺儀數據接口設計

評論