據IPNest機構預測,2015~2024年全球接口類IP保持16%的平均年復增長率。未來幾年,在主流的五大類接口IP,包括USB、PCIe、DDR、D2D&Ethernet、MIPI的市場份額方面,DDR IP市場需求強勁,將持續保持前三的市場份額。

但是,目前在DDR IP的市場上國內IP企業占比很小,究其原因,主要是由于DDR PHY具有較高的技術門檻,要在這類PHY上實現突破并不容易。

首先與其說DDR PHY是一個芯片技術,不如說DDR PHY是一門系統工程。DDR的數據傳輸采用并行多位、單端突發的傳輸模式,對電源完整性PI(Power Integrity,電源完整性)和信號完整性SI (Signal Integrity,信號完整性)的要求很高。另一方面,DDR可以說是對訓練(Training)要求最多的接口。各種訓練是否獲得最佳的結果直接影響DDR工作的可靠性。

對于PHY開發人員來說,既要懂物理層的設計,也要懂訓練算法的設計,只有這樣才能開發出可靠的產品,然而這又無形中抬高了設計的門檻。最后,如何實現高速的單端信號傳輸,是DDR IO設計的一大考驗。

作為一家專注于半導體IP研發和服務的高科技公司,芯耀輝科技看準了企業的需求和市場機遇,通過可靠的SI和PI分析、優化的訓練算法設計、高性能的IO設計等一系列技術創新,成功突破了DDR PHY的技術瓶頸。

關鍵技術點一:可靠的SI和PI分析指導

DDR數據傳輸的特點是:多位并行傳輸,單端數據突發模式。目前SoC可以集成多達72位(DDR4帶ECC)的DDR接口,多位并行傳輸在封裝和PCB上的布線是非常復雜的,很多走線有一定等長要求,同時還要盡量減小線間串擾,所以合格的封裝和PCB設計是一大挑戰。另外突發模式的傳輸,SSO(Simultaneous Switching Output)噪聲也會嚴重影響DDR的性能。所以DDR穩定的工作需要可靠的SI和PI分析。

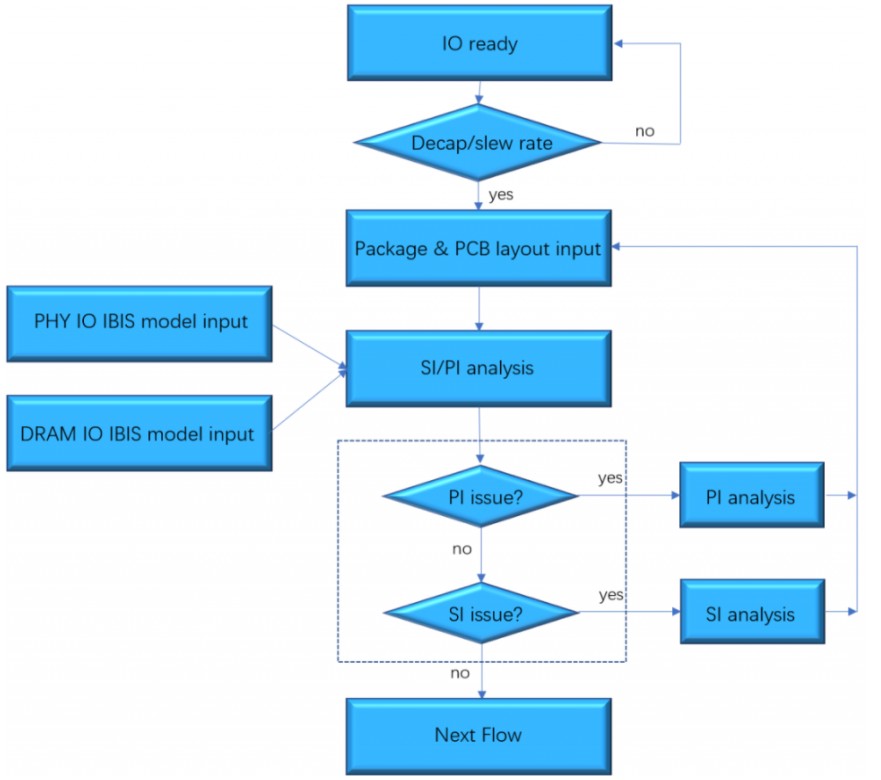

在芯片開發早期,確定好芯片的PAD規劃和封裝規劃,對于設計后期優化DDR的SI和PI性能至關重要。芯耀輝在系統級芯片設計早期、IO準備階段就開展SI和PI的分析,提前幫助客戶規劃,以確保集成的DDR PHY的量產性能。如下圖2所示為芯耀輝的SI和PI流程示意圖。

圖2 芯耀輝SI和PI流程示意圖

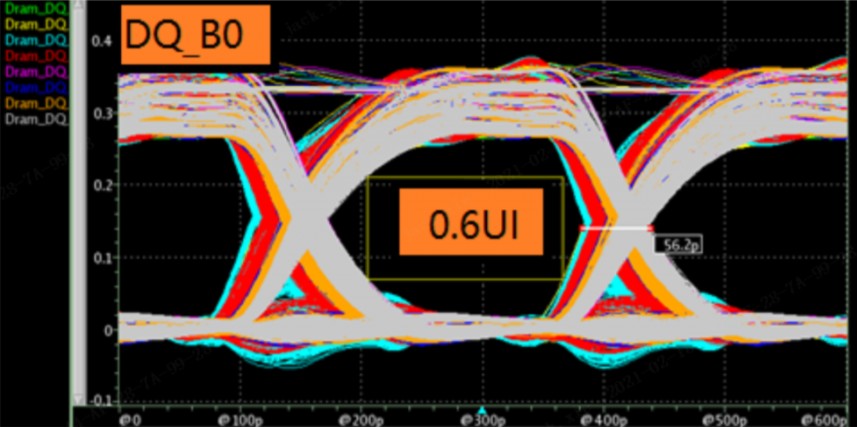

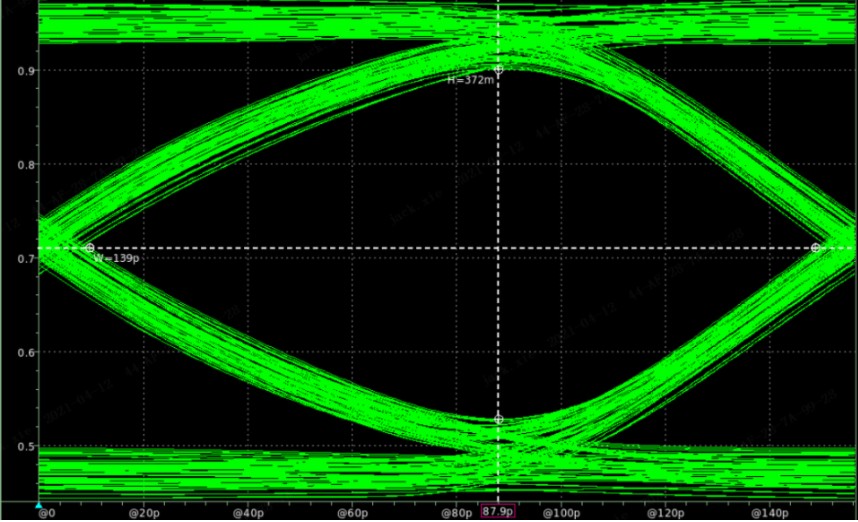

另外,芯耀輝團隊還開發出了一套特殊碼流分析技術。通過該技術,在設計階段可以高效地分析封裝和PCB設計是否滿足DDR眼圖的要求,可以快速定位缺陷,并指導客戶優化完善。圖3給出了一個實際合作案例,展示了系統設計最終完成后的眼圖質量。

圖3 芯耀輝LPDDR4X-3733仿真寫數據眼圖

關鍵技術點二:高可靠性訓練設計

DDR系統的穩定工作離不開各種訓練。在啟動的時候需要做初始化的CA Training,Write Leveling,Read Leveling和 Write Eye Training等一系列訓練,對于DDR4、LPDDR4及以上的更高協議,還需要VREF的二維訓練。基于純硬件的方式無法提供復雜的訓練范式。例如JEDEC的DDR4協議里面規定了DRAM只能提供簡單的01010101等范式, 這對于高速DDR的訓練是不足夠的,因為這些范式頻率單一,無法反映數據通道衰減帶來的碼間串擾(ISI)。另外,不同范式在終端的反射也會不一樣。所以如果采用JEDEC規定的簡單范式來訓練DDR,特別是在較高速率下,不能得到一個最優化的訓練結果。

芯耀輝的DDR PHY采用基于固件的訓練方法,可以設置不同的范式,如PRBS范式、特殊設計的掃頻范式等。顯然此類范式能更全面的反映數據通道特性,因為它包含了高頻、中頻、低頻信息,以及長0和長1帶來的碼間串擾等問題,可以保證獲得更優的訓練結果。

初始化的訓練完成之后,芯片內部溫度和電壓會隨著工作狀態和環境溫度的變化而變化,此溫度和電壓的變化會讓訓練的結果偏移理想值,使得DDR的讀寫裕量減小,嚴重的情況還會造成讀寫數據錯誤。芯耀輝開發了一種可以動態檢測芯片內部溫度和電壓變化的技術,通過實時補償各種訓練結果,保證數據的讀寫具有足夠的裕量,確保DDR工作的穩定性。

關鍵技術點三:高性能DDR IO設計

信號碼間串擾和走線的阻抗不匹配帶來的信號反射嚴重影響數據通信。為了保證DDR數據讀寫的可靠性,在DDR IO設計中,芯耀輝采用了FFE(前向反饋均衡)和DFE(判決反饋均衡)技術。

FFE 前端預均衡

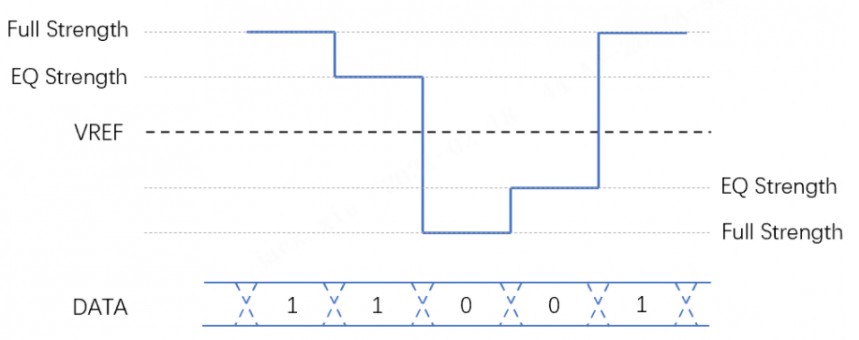

FFE前端預均衡是在DDR TX端采用的技術。因為數據通道有衰減,使得信號高頻部分被抑制較大,低頻部分被抑制較小,所以在RX端看到的眼圖眼高和眼寬均比較小。FFE的思想就是減小低頻分量的能量,使得信號的高頻低頻部分在信道之后達到均衡。圖4展示了FFE原理,如果信號有0-》1的或者1-》0的變化,則輸出滿強度(Full Strength)的信號,如果信號是連續的1或者0,則輸出均衡強度的信號(EQ Strength)。

圖4 FFE前端預均衡原理示意圖

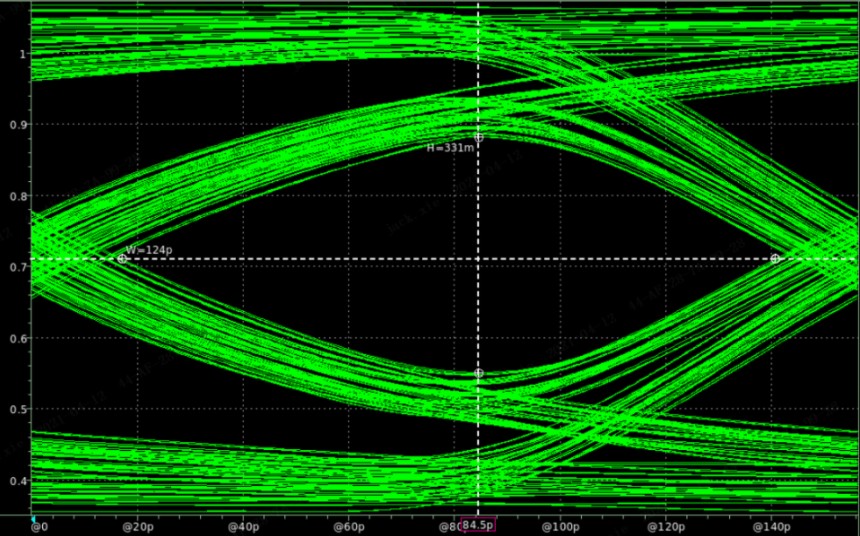

圖5 展示了在RX端,數據速率是6400Mbps時,關閉FFE和打開FFE的仿真示意圖。可以看到,打開FFE的眼圖質量明顯好于關閉FFE的眼圖質量。

圖5 芯耀輝仿真效果示意圖(6400Mbps),左圖沒有打開FFE,右圖打開FFE

芯耀輝采用可編程的前端預均衡方案,通過設置不同參數可以獲得不同的均衡效果,以適應各種應用場景的需要。

自適應算法支持的接收端DFE(判決反饋均衡)

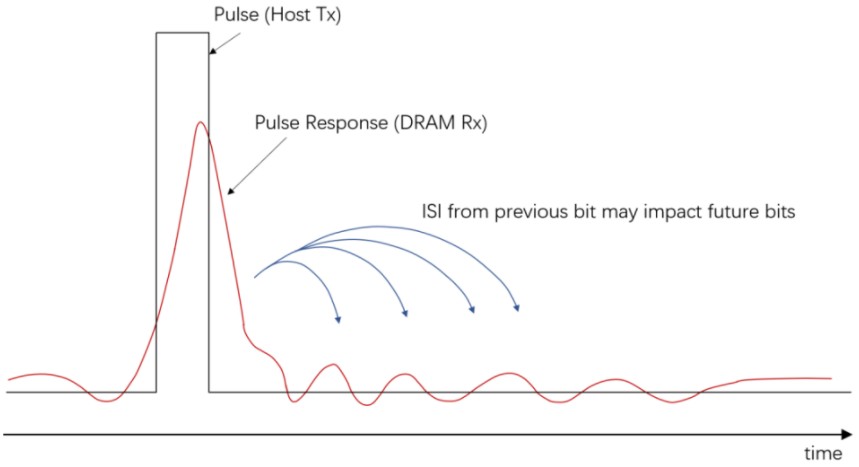

信號的碼間串擾可通過脈沖響應(pulse response)示意圖理解,如下圖67所示。

圖6 經過信道的脈沖響應

當脈沖信號經過信道時,因為高頻衰減和信道反射,會形成一個拖尾的波形,前一個bit的信號會影響將來bit的信號質量。DFE的原理是:判斷之前幾個bit的信號是1或者0,然后通過加權和反饋相加,減弱前bit信號的拖尾影響,以達到改善當前bit信號質量的目的。相比于CTLE等均衡技術,DFE不會放大噪聲信號,因此固態技術協會在JEDEC79-5 規范中正式引入了DFE技術,目的就是為了增強接收端的能力。

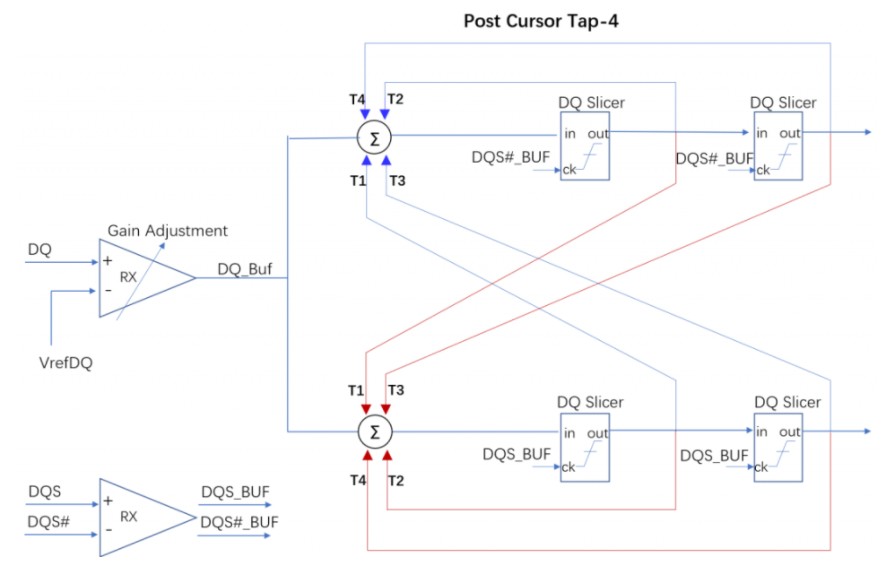

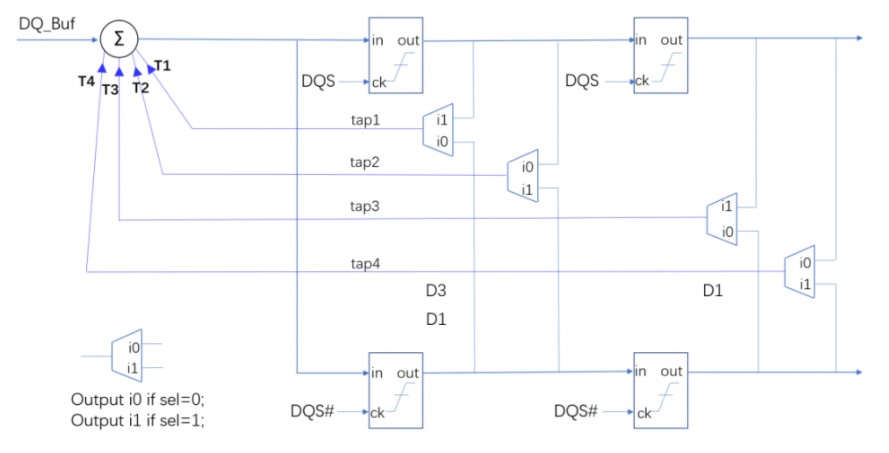

圖7是常見的4 tap DFE架構,也是JEDEC規范推薦的架構之一。因為DQS的上升沿和下降沿均會采樣DQ,所以采樣電路分為上下兩個數據通路。兩個數據通路的4個采樣值經過加權系數處理后會反饋到每一個數據通路對應的求和器(∑),從而減去這4個之前信號對當前信號的ISI影響。這種結構采用了兩個求和器,會加大DQ_Buf端的負載。另外4個采樣值均需要直接反饋到兩個求和器,會使得芯片內部連線比較復雜,影響高速性能。圖8是DFE的另一種架構,這種結構通過MUX選擇兩路數據通路的采樣值,并把選擇后的值送到求和器進行EQ處理。因為只用到了一個求和器,減小了芯片內部的連線復雜性,最重要的是減小了DQ_Buf端的負載,提升了高速性能。

圖7 常見的4-tap DFE架構

圖8 另一種常見的4-tap DFE架構

DFE各級tap的加權系數可以通過手動設置,前提條件是要得到信道的參數,這樣做不適合產品的大規模量產,因為對不同的產品來說,它的IO特性、信道參數是有隨機偏差的,同樣的一套設置不能保證每個產品都有最佳的DFE性能。通過自適應訓練得到DFE各級tap的系數是目前主流的方式。芯耀輝的DDR PHY提供了一套特殊的固件訓練機制,DFE的各級tap的反饋系數可以通過訓練快速得到,自適應程度高,可保證每一顆芯片都有更優的DFE性能,有效減小碼間串擾和反射造成的影響。

關鍵技術點四:支持多頻點的快速頻率切換技術實現低功耗設計

DDR是SoC系統中的功耗大戶,如何減小DDR的功耗一直是DDR技術革新的動力和方向之一。最直接的方法就是降低供電電壓,而這正是DRAM規范的演進之路。另一方面,從DDR4和LPDDR4開始,DRAM規范定義了POD IO 架構(針對DDR4和DDR5)、LVSTL IO架構(針對LPDDR4和LPDDR5)和數據總線倒置(DBI)技術,能有效地減小IO端的功耗。

以上降低功耗的方法是JEDEC規范限定的技術,芯耀輝還開發出一種動態頻率切換技術,能有效降低系統總功耗。該技術在DRAM初始化的時候可以訓練多達多個頻率點的配置,并保存相關訓練結果。當系統確定不需要DRAM工作在高頻率時,可以通知DDR控制器,然后DDR控制器會通知DFI,并讓DRAM進入自刷新狀態,之后頻率切換就會自動在DFI和DDR PHY內部進行,頻率切換完成之后DDR控制器則會讓DRAM退出自刷新,這樣DDR就可以切換到一個較低的工作頻率,從而降低功耗。相較于同類產品,該技術最大特點是整個過程無需固件接入,在新的頻率點無需重新做訓練,從而快速穩定地實現頻率切換。

總結

未來,市場對DDR PHY的需求持續增長,在先進制程上的需求更加突出。芯耀輝較早切入了基于FinFET工藝的IP開發,通過不斷的技術創新,成為目前少數能提供先進制程、優越性能,穩定可靠的DDR PHY的本土企業之一。

百尺竿頭,更進一步,芯耀輝人必將以提供高性能的接口類IP,高品質的設計服務為己任,奮發圖強,助力攜手合作廣大芯片設計公司及晶圓代工廠,推出更優秀的產品,助力提升中國芯片產業的發展。

本文綜合整理自芯耀輝科技 EDN電子技術設計 半導體行業觀察

責任編輯:pj

-

半導體

+關注

關注

334文章

27359瀏覽量

218593 -

數據傳輸

+關注

關注

9文章

1889瀏覽量

64587 -

DDR接口

+關注

關注

0文章

5瀏覽量

7534

發布評論請先 登錄

相關推薦

芯耀輝DDR PHY訓練技術簡介

芯耀輝推出可編程的前端預均衡方案

芯耀輝推出可編程的前端預均衡方案

評論