復用不僅是SOC設計思想的核心,也是解決SOC測試的基礎。本文在分析SOC的基本概念和特點的基礎上,從復用的角度對現有的SOC測試方案進行分析和綜述,并探討了亟待解決的問題。

1 引言

90年代國際上出現的SOC概念,以系統為中心、基于IP模塊多層次、高度復用的設計思想受到普遍重視和廣泛應用 [1,2]。SOC的高集成度和復雜度使得SOC測試面臨挑戰,傳統的基于整個電路的測試方法不再適用。對于IP模塊和SOC而言,在電路設計向可復用這一目標發展的同時,測試中的復用也變得愈加重要,成為解決SOC測試的關鍵 [3],也成為目前該領域研究的焦點。本文在分析SOC與SOB(system on board)本質區別的基礎上,闡明復用對于SOC測試的重要性,對現有主要幾類基于復用思想的SOC測試進行分析。

2 SOC的測試

SOC使集成電路設計者分為兩個部分:IP模塊的設計者和SOC集成者(IP模塊的使用者)[2,4,5] 。IP模塊是設計者提供的具有特定功能和相關參數描述的模塊;而SOC集成者利用它們和用戶自定義邏輯(UDL)集成在一起,實現既定的功能。從表面上看,這種設計類似于傳統的基于芯片的SOB 設計,但二者存在本質區別。

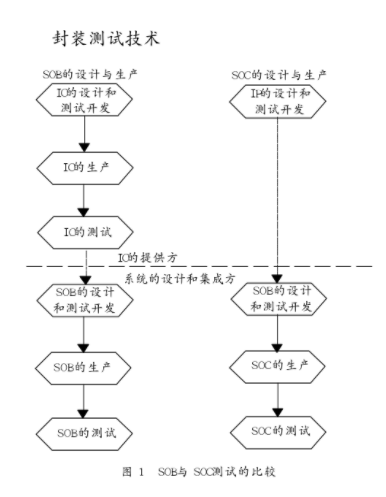

SOB中的IC是經制造生產和測試后的實體,因此對SOB集成者而言,測試是針對系統中IC之間連接的測試。在SOB的設計集成過程中,IC的制造商和系統的集成者有相對獨立的測試開發和實施階段,如圖1所示。從描述的層次而言,SOC中的IP模塊可以分為軟核、固核以及硬核。每一個核又可以是若干更小的模塊共同構成,但無論什么模塊,相對于SOB中的芯片而言是虛擬器件,在進行SOC集成設計時都未經物理實現。

IP模塊提供者對所設計的虛擬模塊進行測試開發,卻不能對IP模塊進行實際的物理測試。因此IP模塊設計者和SOC集成者的測試開發和實施將不再是彼此獨立和分割的兩個階段。SOC集成者要完成包括IP模塊在內的整個芯片的測試方案[2]。因此,SOC測試較傳統的SOB測試而言,更加復雜,也更具挑戰性。

3 復用技術與SOC測試

隨著技術的發展和市場的需要,IP模塊和SOC 的設計正逐漸以分布和并行的方式進行。來源于不同的各種IP模塊的多層次復用是SOC的基礎。IP 模塊是對功能和實現方式的描述,是未經物理實現的虛擬器件,不同類型的IP模塊有不同的模型和測試方法,IP模塊的提供者雖然無法對模塊進行物理測試,但必須向SOC集成者提供模塊的測試信息,其中包括模塊的測試方法、可測性結構、測試產生方法及測試集等 [2,4,6]。

如果不以這些模塊的測試信息為基礎,SOC集成者就無法對高達千萬門級的芯片進行測試,而復用則是SOC測試的關鍵。因此,國際上IEEE P1500工作組和VSIA(virtual socket in ter face alliance)聯盟正在制定相關的國際標準[6,7] ,研究焦點集中于規范IP模塊設計者和SOC集成者之間的軟硬件接口,如模塊測試語言(CTL,)和可擴展結構,以實現SOC測試中IP模塊測試信息的即插即用。

但標準并不進行復用方法和測試集成及優化的研究,有許多問題尚未解決。因此采用何種方式復用,如何解決復用中遇到的問題成為目前 SOC測試研究的焦點之一。從復用的角度,現有的SOC測試解決方案大致分為兩類:直接復用和間接復用。

3.1 直接復用

該方法的基本思路是自頂向下,直接在芯片級使用已有的模塊測試信息,通過實現對每個IP模塊的測試訪問從而解決整個芯片的測試[8]。核心是通過構建測試通路實現對各IP模塊的測試訪問,前提是各IP模塊都具有良好的可測性和完整的測試信息。這類方法的有效性關鍵在于兩個方面,即各模塊原有測試信息的質量和在SOC中各模塊測試訪問的實現。具體的方案如下。

① 測試總線。ARM公司發布的32位AMBA(advanced microcontroller bus architecture)總線結構,通過解決每個IP模塊的測試訪問問題來最終完成整個SOC的測試,但其兼容性、測試費用及測試時間上有其局限性 [9]。Duel Technologies公司也作了類似的工作,提出了“測試總線”,連接每個IP模塊,雖然優化了測試所占用的芯片面積,但無法同時將多個IP模塊連到總線上進行測試。

② 端口訪問。Intel公司提出將每個IP模塊的接口端通過多路選擇器接到芯片的引腳上直接進行訪問[10]。但當IP模塊增加時,對多路選擇器的控制就會過于復雜,且該方法對IP的端口數有明確的限制。

③ 模塊的透明模型。文獻[11]提出一種基于IP模塊透明模型的方法,它要求每個IP模塊都有一種工作模式——透明模式。當對SOC中某一個IP模塊進行測試時,其它模塊均處于透明模式,從而為該模塊提供測試訪問通路。這種方案較前兩種方案減少了硬件開銷,但對IP模塊的設計有特殊要求,且數據傳輸通道多位串行會導致測試時間過長。

④ 邊界掃描。Texas Instrument公司利用IEEE 1149.1標準中的邊界掃描測試(BST)技術,通過標準的掃描鏈串行訪問IP模塊,該方案是將用于解決SOB的測試技術移植到了SOC上。該方案的硬件開銷會隨著電路集成度提高而加大,測試時間也會隨著SOC規模的增加變得無法接受[12]。

3.2 間接復用

這類方法的基本思路是自底向上,利用每個模塊級的測試信息,通過綜合轉換形成該模塊在芯片級可以實施的測試信息,直至形成整個芯片的測試。核心是以系統為出發點,利用各IP模塊的測試信息,綜合SOC的結構或功能特點,形成SOC 對各IP模塊的測試數據和方案。具體的方案如下。

① 宏測試。從設計出發,在自IP模塊向系統集成的過程中不斷將模塊的測試信息進行擴展,直至芯片級。其中較為典型的是Philips公司將解決IC測試的Macro Test技術用于SOC測試[13]。其基本思路是將每個IP模塊的測試信息以測試協議描述,結合整個系統的設計,識別合適的訪問路徑擴展到芯片級,再通過芯片級的測試協議調度每個模塊的測試順序,最終通過單獨測試每個IP的方法來完成SOC測試。該方法對SOC中的IP模塊及其測試信息有嚴格的規定。

② 層次復用。文獻[13]提出了一種層次法,基本思路是針對系統進行分析,提取系統中與待測IP 模塊的約束關系,使模塊在約束下直接產生測試集,進而解決整個芯片系統的測試問題。該方法每次只考慮一個模塊,先對每個模塊產生功能約束,將約束和該模塊一起綜合,形成一個從芯片級可以訪問的對應電路,再用商業軟件對模塊內部的故障生成測試。但當該技術應用到集成度很高的SOC時,模塊本身測試的生成變得非常困難。如果SOC中的模塊是多層次復用的,需要進一步分解成子模塊,約束條件的提取變得十分繁復。為解決這個問題,文獻[14]提出一種新的層次地提取可重復使用的約束方法,并在提取約束時利用綜合工具剔除冗余的邏輯部分,提高了測試生成效率,使其更有效。 中聯網

③ 功能復用。SOC的功能日益強大,其中許多都含有內嵌處理器和存儲器。文獻[16],[17]提出,在SOC內部通過內嵌處理器模塊和存儲器模塊實現對其他IP模塊的測試。具體就是首先將各IP模塊的測試數據壓縮并存入存儲器模塊,再由內嵌處理器利用這些數據,對IP模塊進行測試并收集響應進行測試分析。這種方法充分利用了SOC內部資源和已有的各IP模塊測試信息,可以實現芯片內部的高速測試。但測試數據處理和測試控制的復雜度都會隨的SOC設計復雜度的加大而增加。

4 面臨的問題

SOC內部晶體管集成度的增長遠遠高于芯片引腳的增長,有限的管腳資源使得外部數據帶寬和內部數據帶寬之間的差異越來越大[1]。這種差異不僅降低了內部模塊的可測性,還加大了間接復用方案中測試生成的難度。同時,具有一定故障覆蓋率的測試數據會隨著電路集成度和規模的增加而增加,大量的測試數據會對直接復用方案中的測試訪問的頻率和帶寬提出要求。

SOC嵌入了類型豐富的IP模塊,一些公司已將模擬電路、數字電路、嵌入式DRAM等不同形式的模塊集成到芯片中。隨著技術的發展,將有更多的電路類型被集成到SOC中,如嵌入式的FPGA、Flash、射頻發生器等。混合信號測試在SOC測試中占有重要地位,現有的復用方案還未解決該問題。

前面分析的現有方案有的來自于專業廠商,有的是利用自己的技術傳統,對原IC、SOB測試技術的改進,著眼于解決各自產品的測試問題,因此研究的出發點有局限性,各方案的適用范圍有限。

5 結論

迄今為止,還沒有一個貫穿IP模塊和SOC設計始終的完整的SOC測試解決方案,因為這不僅需要盡快訂立相關的國際標準,還需要進行一些關于復用方法上的研究,例如,如何在進行IP模塊的測試開發中引入可復用的因素,使得模塊級的測試信息對被集成環境具有更好的適應性,能被更高層電路模塊的測試開發高效率地復用;研究基于復用的測試集成和優化技術,利用已有模塊測試信息,集成出更高層模塊的測試并保證其可復用性等。

編輯:jq

-

芯片

+關注

關注

455文章

50714瀏覽量

423159 -

soc

+關注

關注

38文章

4162瀏覽量

218167 -

IP

+關注

關注

5文章

1702瀏覽量

149508 -

晶體管

+關注

關注

77文章

9682瀏覽量

138084

發布評論請先 登錄

相關推薦

Advantest推出適用于V93000 EXA規模測試平臺的先進功率多路復用器

soc技術在智能設備中的應用

最新SOC芯片技術發展

soc芯片測試有哪些參數和模塊

波分復用技術是如何工作的

密集波分復用和稀疏波分復用的區別

光纖是波分復用還是頻分復用?波分復用和頻分復用有什么不同?

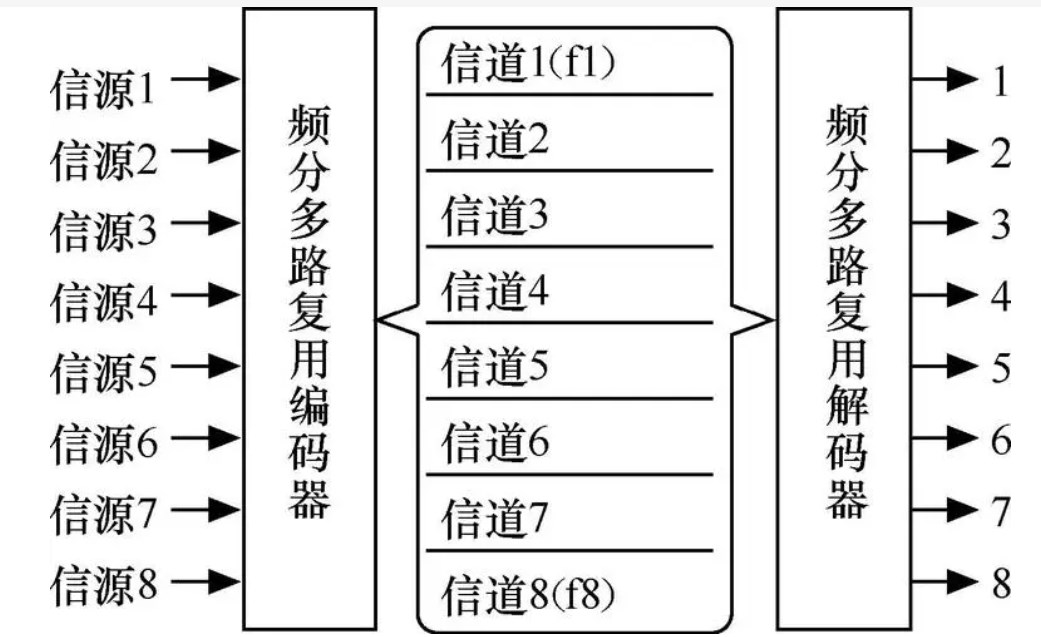

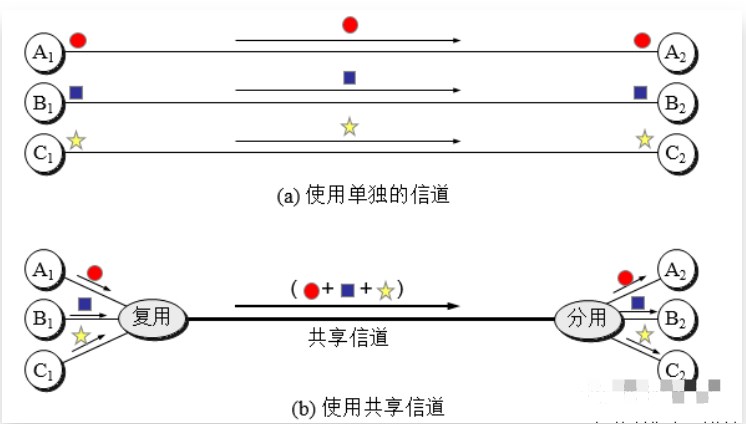

簡述多路復用技術的工作原理 多路復用技術有哪些

頻分多路復用和時分多路復用的區別有哪些

波分復用的特點 波分復用(WDM)和頻分復用(FDM)的區別

多路復用技術主要有幾種類型?它們各有什么特點?

頻分多路復用的原理 頻分多路復用方式的分類

淺談復用的SOC測試技術

淺談復用的SOC測試技術

評論