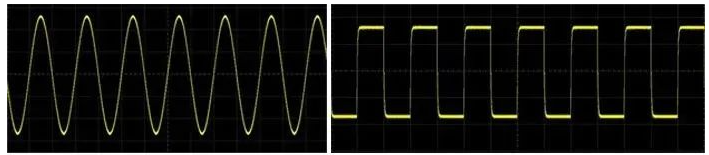

石英晶體振蕩器常用的輸出模式主要包括:TTL、CMOS、ECL、PECL、LVDS、Sine Wave。其中TTL、CMOS、ECL、PECL、LVDS均屬于方波,Sine Wave屬于正弦波。今天給大家講解到的是晶體振蕩器中的三態輸出技術。

大多數數字系統使用由兩個狀態級別0和1表示的二進制數系統。在一些特殊應用中,需要第三狀態(Hi阻抗輸出)。TTL,HCMOS或HCMOS石英晶體振蕩器提供三態輸出或三態啟用/禁用功能。其常見應用包括自動測試,總線數據傳輸。

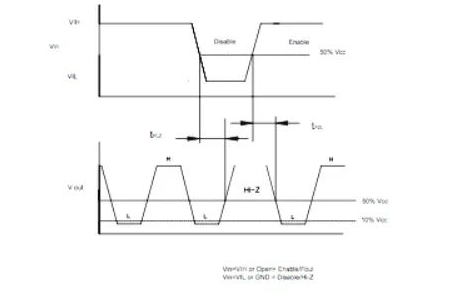

這三種狀態是低,高和高阻抗(HiZ或浮動)。高阻抗狀態的輸岀表現得好像它與電路斷開,除了可能有小的漏電流。三態器件具有使能/禁止輸入,通常在幾乎任何封裝的引腳1上。當使能為高電平或懸空時,器件振蕩(輸出高電平和低電平),當引腳1接地(邏輯“0”)時,器件進入高阻態。

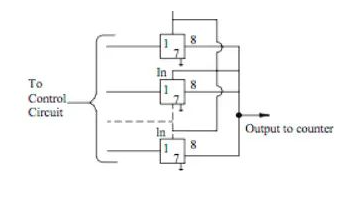

總線是一組通用的電線,通常用于數據傳輸。三態總線有幾個三態輸出連接在一起。通過控制電路,除了一個總線上的所有設備都具有高阻抗狀態的輸出。其余器件使能,驅動高低輸出總線。

三態功能的其他應用是用于自動測試設備(ATE)。幾個有源晶振晶體振蕩器的輸出連接在一起。對于控制電路,除了振蕩器外,所有振蕩器都具有高阻抗狀態的輸出。選擇的振蕩器將從計數器讀出其頻率。

在三態函數生效之前總會有一些延遲。此轉換發生在兩個轉換(禁用和啟用時)。從低電平開始的三態輸出禁止時間是tPLZ,三態到低電平的輸出使能時間是tPZL。

CMOS

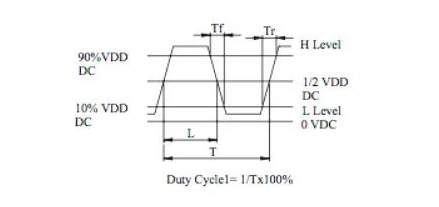

上升和下降時間CMOS技術的上升和下降時間取決于其速度(CMOS、HCMOS、ACMOS、 BICMOS),石英晶體振蕩的電源電壓,負載電容和負載配置。CMOS 40000列的典型上升和下降時間為30ns, HCMOS為6ns,而ACMOS( HCMOS/TTL兼容)的最大上升和下降時間為3ns。典型的上升和下降時間在其波形水平的10%至90%之間測量。

ACMOS輸出終止技術

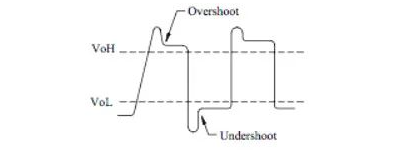

由于ACMOS( HCMOS/TL兼容)器件的快速轉換時間,在測試或測量石英晶體振蕩器電氣性能特性時必須使用正確的端接技術。端接通常用于解決電壓反射問題,這實質上導致時鐘波形中的步驟以及過沖和下沖。這可能導致數據的錯誤時鐘,以及更高的EM和系統噪聲。

由于PCB板上的線長度及其負載配置,還需要端接。有三種終止時鐘軌跡的通用方法,即將器件的輸出阻抗與線路阻抗相匹配的過程:

方法1:串聯終端在串聯終端中,阻尼電阻靠近時鐘信號源放置。Rs的值必須滿足以下要求:Rs≥ZT-Ro

方法2:上拉/下拉電阻在上拉/下拉終端中,組合的戴維寧等效于跡線的特征阻抗。這可能是最干凈的,并且不會產生任何反射,也會降低EMI。

編輯:jq

-

CMOS

+關注

關注

58文章

5710瀏覽量

235407 -

TTL

+關注

關注

7文章

503瀏覽量

70231 -

ECL

+關注

關注

0文章

38瀏覽量

13423 -

高阻抗

+關注

關注

0文章

19瀏覽量

10267

發布評論請先 登錄

相關推薦

石英晶體振蕩器的頻率范圍

壓控晶體振蕩器和石英晶體振蕩器的區別

壓控晶體振蕩器的構成和工作原理

晶體振蕩器怎么判斷好壞

晶體振蕩器的工作模式和作用

延長晶體振蕩器使用壽命的預防措施

一文詳解晶體振蕩器

一文讓你明白晶體振蕩器三態輸出技術到底是什么

一文讓你明白晶體振蕩器三態輸出技術到底是什么

評論