SOC 驗證有什么用?

這篇文章的標題聽起來像是上世紀90年代電視劇里的玩笑,但它實際上是一個嚴肅的問題。很多人不明白,是什么讓一個系統級芯片(SoC)與其他半導體器件不同。許多公司,尤其是在電子設計自動化(EDA)行業中,圍繞術語“SOC”進行了眾多討論,但卻沒有定義它,或者解釋它為什么是這樣一個重要的概念。

Soc驗證的含義

從“SoC”的定義開始討論,應該是最合適的地方。正如其名稱所暗示的那樣,“系統級芯片”,是存在于單個封裝的完整系統,通常都處于單個die,盡管3-D集成電路建立在多個die上的情況也正變得越來越普遍。

本質上,SoC就是將分布在多個芯片甚至是離散設備上的功能集成到一個芯片中。現在已經很難找到不含某種處理器的系統了,所以在實際的定義中,在SoC必須包括至少一個處理器。

最常見的SoC架構包括一個或多個嵌入式處理器,部分片上存儲器,附加的功能單元,標準總線接口以及可能的片外存儲器。某種類型的片上總線,總線結構,或網絡芯片將所有的單元連接在一起。

與其他芯片驗證不同的原因是什么?

由于需要在嵌入式處理器上運行的軟件,完整的SoC實際是芯片加上在這些在處理器上運行的代碼。有些系統級芯片具有在多個不同的處理器,CPU,DSP,圖像處理器等,——所有的運行代碼都是針對單獨功能定制的。

處理器的存在是使得SoC驗證與其他芯片驗證不同的關鍵。更小,沒那么復雜的芯片,以及許多在SoC內部的模塊,可以使用仿真測試平臺有效的進行驗證。提供數據到芯片的輸入,檢查芯片上的輸出數據。

傳統測試平臺可簡化為一個框架,允許用戶提供一系列的二進制輸入,并使用波形查看器查看輸出結果。當然,如此的手動設置僅僅能夠驗證復雜設計很少的預期功能。

現代的基于測試平臺的驗證環境會為芯片輸入自動生成隨機的stimulus,這種隨機同時處于用戶指定的約束條件(規則)下,并會自動檢查每個測試的結果。這比基于傳統測試平臺手工編寫單獨的測試更有效率。

有約束的隨機測試平臺

一些驗證方法已經建立,流行的標準是有約束的隨機測試平臺,并允許有限復用測試平臺的組件。這些驗證方法中,最有名的是標準組織Accellera定義的通用驗證方法學(UVM)。

帶約束的隨機測試平臺在一定程度上工作正常,但不能就此擴展到full-SoC驗證上。僅僅從芯片的輸入來驗證其所有功能,是一件太過困難的工程。

此外,雖然在SoC的嵌入式處理器通常有能力在仿真中運行代碼,但對所有協調處理器與測試平臺的活動,UVM都不提供任何指導。事實上,在SoC級運行的任何UVM-based仿真,通常用總線功能模型(BFMS)去替代嵌入式處理器。

以上的這些限制導致許多SoC團隊在full-chip級僅僅做最少的驗證。他們僅僅驗證模塊是否已正確連接,并可能運行一些簡單的測試來驗證各主要模塊運行正常。

對SoC運行中,模塊串接的真實情形,他們卻很少運行測試。這種“stitch and ship”方法帶來高風險,因為它從從未測試模塊間復雜相互作用的情況,而其恰恰極可能暴露設計bug或證實性能的缺陷。

模塊級驗證

在模塊級驗證中,很難發現諸如存儲器沖突,總線飽和,等在SoC多模塊共享資源時才發生的問題。

考慮到SoC功能在很大程度上取決于其嵌入式處理器,意料之中,一個純粹的測試平臺是不足夠的。有些驗證團隊認識到這一點,他們用人工設計測試在嵌入式處理器上運行。這些測試通常不連接到測試平臺也未很好集成到整個驗證工作中。

此外,要人工設計對SoC并行功能多任務(multi-threaded)測試簡直比登天還難。當然,我們所需要的就是考慮這些corner-case bugs和性能問題。

充分有效的SoC驗證

SoC驗證要充分有效,就必須包括在嵌入式處理器上運行自動化測試。軟件可以在仿真中生成在多處理器多線程情況下的測試case。

為了對SoC有足夠的壓力測試,測試case需要刺激和協調處理器和測試平臺內的并發活動。測試case必須能夠對隨機生成的輸入數據進行自動驗證,計算輸入的預期結果,并檢查芯片的輸出符合預期的結果。

通常來說,我們需要提供SoC的功能信息給測試case生成器,這些case才能恰當的驗證其功能性并檢驗結果。描述SoC設計功能的最好方法就是一系列可視方案模型。

圖像能夠捕獲芯片的數據流路徑并記錄如何配置模塊來運行所有SoC設計功能。圖像引導的生成器約束保證其不會對非預期行為生成test case。

來自Breker驗證系統中的TrekSoC產品

這個軟件工具能自動生成在SoC的嵌入式處理器上運行并能夠自驗證的C語言test case,而且該軟件不需要操作系統或者其他產品軟件的支持。

這些test case都是多線程的,因此能并行檢驗SoC的多個部位,在tapeout之前進行足夠的壓力測試。生成器中成熟的scheduler能夠跟蹤多個并行運行的現實情況,并從線程中移動它們以盡可能多的對SoC進行測試。

因為一些C-based測試會從芯片輸入讀取數據,或者發送數據到芯片輸出,“TrekBox”組件連接現有的總線功能模型(BFMS)在測試平臺中,并協調處理器和測試平臺間的活動。

當每個C-based測試準備接收或生成數據時,會通知TrekBox處理實際的數據傳輸。源數據也可以被加載到存儲器,并且存儲器檢查可以在不干擾的SoC的情況下進行。

這個基于圖形的場景模型描述了能夠在SoC中產生無限數量的多線程測試case的所有信息。

總結

總之,SoCs使得半導體產業能繼續實現其,更好,體積更小,更快芯片的目標。它們與其它類型的芯片不同,所以SoC的驗證也必然是不同的。

開發團隊必須認識到,在SoC時代,存在嚴重bugs風險或者毫無競爭力的去生產芯片的情況,使得他們的世界已經不同。

自動生成多線程,自我驗證C測試case是一個相當新,但是很好的驗證方法。“SoC驗證”團隊采取這種方式會有著更快產生更好的,更小的芯片的優勢。

編輯:lyn

-

芯片

+關注

關注

455文章

50732瀏覽量

423260 -

soc

+關注

關注

38文章

4163瀏覽量

218173

原文標題:?SOC 驗證有什么用?

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

SOC芯片在物聯網中的作用

SoC的數字簽名加解密過程

放大電路輸出電阻的含義和作用

解鎖SoC “調試”挑戰,開啟高效原型驗證之路

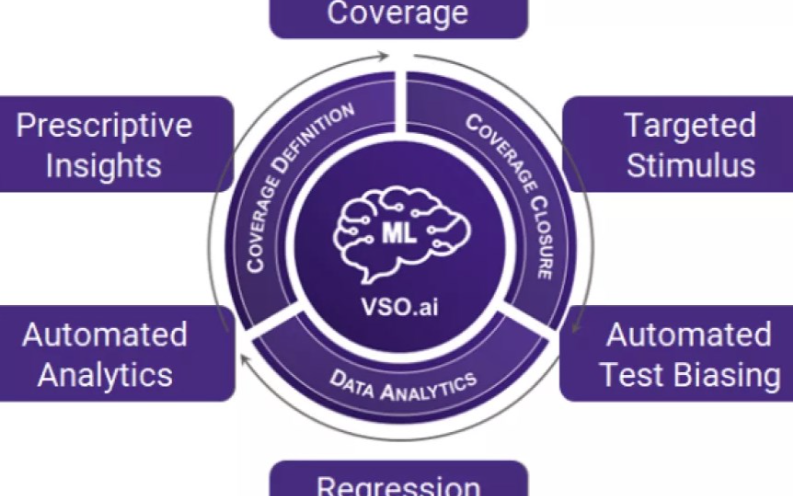

瑞薩如何利用Synopsys VSO.ai將SoC驗證生產率提高30%

pcb助焊層的作用及含義是什么

繼電器的作用和原理 繼電器的型號和含義

編碼器5條線的含義及作用

?SOC驗證的作用與含義及原因

?SOC驗證的作用與含義及原因

評論