作者:詹必勝;吳斌方;楊光友 來源:電子產品世界

隨著集成電路技術的發展,FPGA和DSP以及ARM以其體積小、速度快、功耗低、設計靈活、利于系統集成、擴展升級等優點,被廣泛地應用于高速數字信號傳輸及數據處理,以DSP+FPGA+ARM的架構組成滿足實時性要求的高速數字處理系統已成為一種趨勢,本文主要研究FPGA在高速多路數據傳輸中的應用。

系統結構

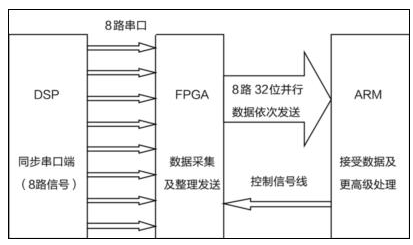

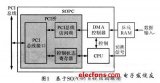

在DSP多路串行數據同時向ARM發送的系統中,因為數據通道有并行要求,應用FPGA硬件并行的特點,由FPGA并行接收多路數據,經過緩沖后再發送至ARM進行數據的高級處理的方案,系統結構圖如圖1所示。

圖1 系統結構圖

FPGA處理模塊實現

DSP的串口傳輸方式為同步串口,每組DSP串口有4個端口,分別為:clk , frame. , data_a,data_b[3]。數據端口有兩個,本例中只使能data_a,以下統一稱為data。

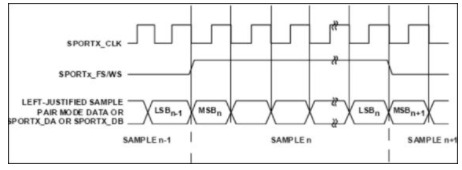

DSP同步串口傳輸時序如圖2所示,當frame為1時,串行數據有效,當frame為0時,一幀數據傳輸結束。本例中DSP傳輸的一幀數據為32bit。

圖2 DSP同步串口傳輸時序圖

FPGA內部采用異步FIFO解決DSP時鐘頻率和FPGA時鐘頻率不匹配的問題,寫時鐘由DSP輸出的同步時鐘信號提供,時鐘頻率為60MHz;讀時鐘由FPGA的鎖相環PLL時鐘提供,PLL輸出時鐘頻率為100MHz。

接收模塊

由于DSP的8個同步串口同時寫入,FPGA數據接收模塊一共有8個,每個模塊接收到的數據都存放在一個特定的FIFO中,將其稱之為R_FIFO。

DSP輸出信號為frame,clk, data,FPGA以DSP同步串口的輸出時鐘clk作為采集數據的時鐘。系統上電結束后,FPGA等待ARM發送接收允許指令,接收允許后,FPGA就可以開始接收數據。

當frame信號為高,FPGA即開始接收從DSP發送的串行數據,在每個dsp_clk的上升沿讀取一個bit的數據,之后將數據轉入移位寄存器中。FPGA引入一個模塊,時刻監測frame的下降沿,當frame下降時,即表示一個字的數據發送完畢,移位寄存器的數據放入R_FIFO的數據輸入口,將R_FIFO的寫使能置高,向R_FIFO發出寫入請求,寫入此時的數據至R_FIFO中,依次循環。當R_FIFO中的數據個數不為0時,即向FPGA的發送模塊發送請求。

發送模塊

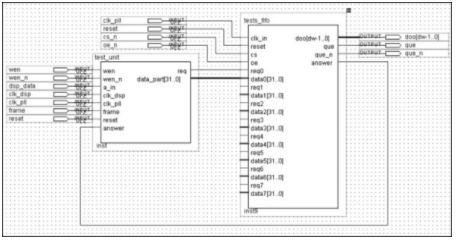

接收模塊接收到DSP同步串口數據后,即通過reg與answer信號與FPGA數據發送模塊之間進行數據傳輸,如圖3所示。

圖3 FPGA接收及發送模塊

當接收模塊有請求時,發送模塊即將接收模塊采集到的數據寫入發送模塊的緩存FIFO中,將其稱之為S_FIFO。每輪從R_FIFO中傳輸的8個數據均依次存入S_FIFO中。

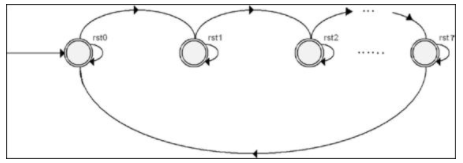

因為DSP的8個同步串口均同時工作,可以認為當有一個輸入模塊的數據接收完畢時,8個端口的數據均應該接收完畢,保險起見,可以延時若干時鐘周期后開始接收數據。從端口0至端口7為一輪,若此時有端口沒有數據,即可認為此端口暫無數據輸出,用數據0替代,發送模塊繼續接收下一個端口的數據。用狀態機來實現此功能,如圖4所示。

圖4 S_FIFO寫操作的狀態機圖

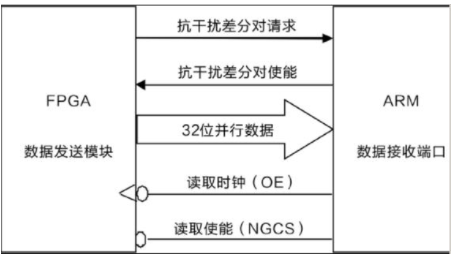

發送模塊完成FPGA向ARM的數據傳輸,當FPGA發送模塊S_FIFO中的數據達到一定數量時,FPGA即向ARM發出發送數據請求,ARM即開始對FPGA進行數據的讀取。

FPGA中的S_FIFO同樣也是異步FIFO。寫時鐘由鎖相環提供100MHz;讀時鐘由ARM的讀取使能信號OE取反得到,讀使能由ARM的片選信號NGCS取反得到。ARM讀取數據會產生NGCS與OE低電平信號,無操作時置高。每次讀取數據時NGCS與OE先后置低,取反接至S_FIFO讀端口分別為NGCS_N與OE_N。對S_FIFO讀取時,每當讀時鐘OE_N為上升沿,讀使能NGCS_N必為1,完成一次讀取操作。

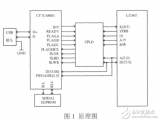

這樣實現了ARM與FPGA之間的跨時鐘域數據傳輸。FPGA發送數據采取乒乓操作, ARM可以源源不斷的將S_FIFO中的數據讀取出來。FPGA和ARM的數據傳輸原理圖如圖5所示。

圖5 FPGA和ARM的數據傳輸

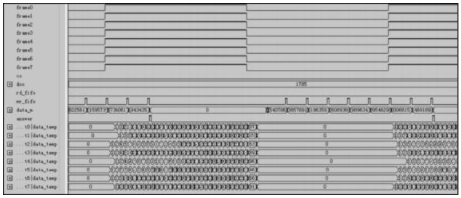

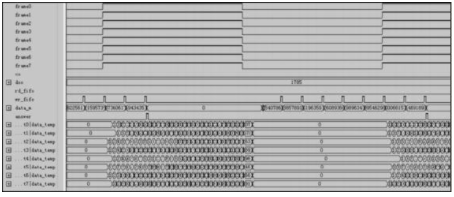

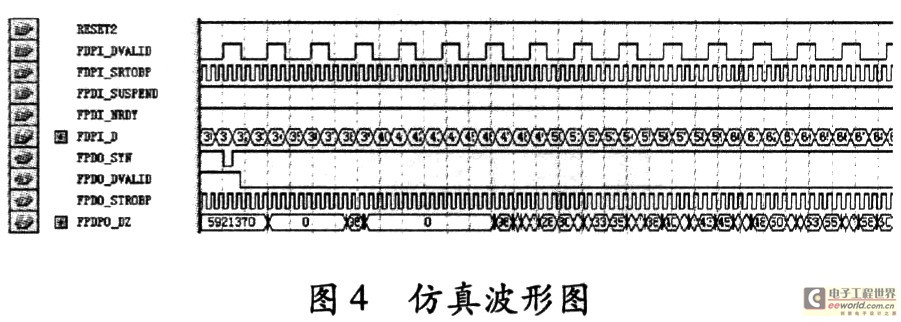

為驗證各控制信號的時序邏輯,做如下仿真:FPGA接收及緩存數據。仿真的時序如圖6所示。data_temp0~data_temp7為接收模塊的移位寄存器,在frame的下降沿時將數據寫入各自的R_FIFO中;R_FIFO中的數據依次通過寄存器data_m寫入S_FIFO中。8次寫入后,一輪緩存即結束,等待下次請求。

圖6 FPGA接收及緩存數據時序仿真圖

信號抗干擾處理

在FPGA和ARM之間的通訊中利用差分信號傳輸用于消除信號的干擾。差分對是指兩條線路總是傳送相反的邏輯電平,差分對信號對外界干擾源產生的噪聲不敏感,例如電路板的干擾噪聲等。

如圖7所示[5],IN引腳連接一個信號源,可以看到,對a噪聲毛刺不敏感,但是對于b噪聲毛刺,卻有可能使其誤認為一個脈沖,而這個可能引起FPGA內部的一些不期望的行為,如讀出一個錯誤的值。

圖7 差分降噪處理原理

差分對中的兩個信號總是傳送互補的邏輯值,所以當上圖中的IN_P為邏輯1時,IN_N則為邏輯0,反之亦然。并且布線時,差分對的兩條線路布線得非常的近,因此噪聲對他們的影響都是相同的。接收端只對兩個信號的差異感興趣,若兩個信號相同,則對此不敏感。

結語

利用DSP的實時數據處理能力與FPGA優越的硬線邏輯設計相結合,保證了多通道數據采集系統的實時性和精度要求,實現高速數據傳輸,同時簡化系統硬件設計,縮小系統體積,具有極高的性價比。系統的數字部分硬件采用Verilog硬件描述語言實現,便于修改和升級,可根據實際測試應用需求作靈活的改進。本數據采集傳輸模塊已成功實現,并取得了良好的應用效果。

責任編輯:gt

-

dsp

+關注

關注

553文章

7987瀏覽量

348743 -

FPGA

+關注

關注

1629文章

21729瀏覽量

602986 -

ARM

+關注

關注

134文章

9084瀏覽量

367381

發布評論請先 登錄

相關推薦

基于FPGA和USB的高速數據傳輸、記錄及顯示系統

USB2.0+FPGA實現多路數據傳輸系統

基于Zynq-7000的SRIO高速數據傳輸設計與實現

基于DSP+FPGA+ARM的架構實現高速多路數據傳輸系統的設計

基于DSP+FPGA+ARM的架構實現高速多路數據傳輸系統的設計

評論