航天技術的發展,對遙測系統的性能要求越來越高。飛行器復雜程度的加大、測量參數種類的增多、數據量的增大、測量實時性的增強使傳統有限傳輸信道容量的遙測系統面臨巨大挑戰。為此,可以通過采用數據壓縮技術,有效地提高信道利用率,減少遙測數據的傳輸時間和存儲空間,增強遙測數據的實時性和吞吐率。

設計的數據壓縮器以FPGA為控制單元,用DSP實現數據壓縮,可將6路模擬信號采集并壓縮,再經長線發送至數據接收器。實現硬件模塊化、功能軟件化設計,依靠FPGA的并行執行特性,結合高速DSP通信,可靠地完成被測信號的采集、壓縮功能。在保證系統可靠性的同時節省系統的開發成本,提高了系統的可重構性[1-2]。

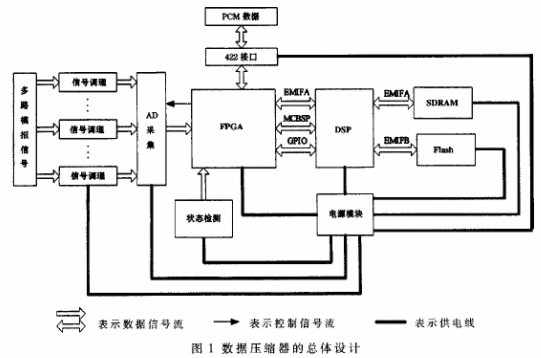

1 數據壓縮器的總體設計

數據壓縮器基于FPGA和DSP的硬件平臺,將待壓縮的6路模擬信號經過調理后輸入給A/D轉換器進行量化,FPGA將量化結果寫入其內部FIFO(First In First Out)緩存中。DSP通過判斷FIFO的半滿信號讀取數據,并根據通道號把數據流分配到6個分組緩存區,當其中任一分組緩存區滿2 KB時,就進行一次壓縮,壓縮后的數據被存入緩存器中。

當緩存器半滿時,DSP將壓縮后的數據串行發送至FPGA,FPGA根據接口的通信協議再把壓縮數據發送給數據接收器,以保證壓縮數據傳輸的實時性。壓縮器的總體設計方案如圖1所示[3-5]。

2 硬件及實現原理

2.1 控制單元的選型

FPGA采用XILINX公司的低成本產品XC3S200AN。其包含豐富的Block RAM資源,可利用IP核建立內部FIFO,以便于數據緩存。XC3S200AN內部含有4 MB大小的Flash,可以存儲FPGA程序。DSP是執行數據壓縮的核心單元器件,選型時在考慮處理速度的同時,還要兼顧其與其他設備的接口匹配能力。選用TI公司的TMS320C6416高性能DSP,其CPU工作主頻達到600 MHz,內含容量為1 MB的RAM內存,同時可通過外部存儲器接口(EMIF)、多通道緩存串口(MCBSP)等外設接口與FPGA及存儲器連接。

2.2 信號采集電路設計

設計要實現對6個通道的信號進行每通道30 kHz、8位分辨率的采樣,相當于總采樣率180 kHz。選用TI公司的16位、250 kS/s、6通道同步采樣模數轉換器ADS8365,能夠滿足要求[2]。為了保證模擬信號能被正確量化,先采用運算放大器OPA4340對信號進行電壓跟隨,再由FPGA控制ADS8365進行采樣。

通過在FPGA內部建立FIR濾波器IP核對采集到的數據進行數字濾波,隨后將其低13位并置3位通道編號發送給DSP。DSP工作頻率通常能達到幾百兆赫茲,但FPGA的工作頻率僅為幾十兆赫茲,所以FPGA要將數據先緩存在其內部FIFO,便于DSP讀取[6-8]。信號調理電路如圖2所示。

2.3 DSP的通信接口設計

DSP從FPGA中讀取采樣數據進行壓縮,再將壓縮后數據發回FPGA,由FPGA進行編碼后發送到數據接收器。由于數據壓縮需要較大的處理空間,而DSP內部存儲空間有限,為防止在數據壓縮期間內采樣數據和壓縮結果因不能及時傳送而丟失,故在數據輸入、輸出接口之間設計了緩存單元。采樣數據輸入緩存可用FPGA內部FIFO承擔,考慮到FPGA內部RAM資源有限,僅能搭建容量較小的FIFO,而需要的是大容量數據輸出緩存單元。

因此,設計中DSP的外部存儲采用64 MB容量,能夠緩存1 MB壓縮數據,64位數據寬度的同步動態隨機存儲器(SDRAM)MT48LC2M32B2TG芯片。DSP在采集數據時的數據通信操作較復雜,如果按照外設的器件手冊編程實現對其控制效率太低,而用DSP的外部存儲器接口EMIFA可極大地簡化操作過程,將采集數據FIFO映射到EMIFA的CE2空間;

將SDRAM映射到CE0空間,只需設置DSP的EMIFA相關寄存器參數即可實現數據通信。同樣可通過設置DSP的MCBSP相關寄存器參數來完成壓縮后數據的發送[9-11]。連接如圖3所示。

3 邏輯控制

3.1 FPGA邏輯設計

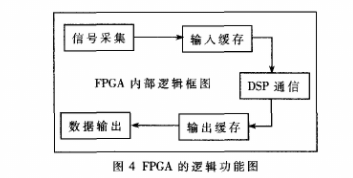

壓縮器中,FPGA作為控制單元,完成6路模擬信號采集的邏輯控制、數據傳輸控制以及與DSP的數據傳輸。如圖4所示,FPGA邏輯功能可劃分為4個模塊,分別為信號采集模塊、數據輸入緩存模塊、DSP通信模塊和數據輸出模塊。其中數據輸入、輸出緩存模塊的實現,可通過調用FPGA的IP核設置參數生成相應容量的FIFO來完成。

3.2 DSP程序設計

DSP程序模塊主要完成模擬信號的壓縮處理。DSP的程序包括模擬數據的預處理、模擬數據的壓縮以及與外部存儲器的通信等。DSP程序流程圖如圖5所示[12-14]。

TMS320C6416在上電啟動或者復位后,DSP程序從Flash中加載并啟動,完成系統的初始化以及各個參數的設置,然后進入主函數、初始化CSL函數庫、MCBSP、可編程輸入輸出接口(GPIO)等相關中斷寄存器和內部FIFO。當TMS320C6416檢測到輸入FIFO半滿信號,DSP從輸入FIFO中讀取模擬信號的量化值,當SBUF中有待處理標志時,

DSP啟動ARC編碼開始數據壓縮,ARC編碼將返回壓縮后的數據長度,如果壓縮后的數據長度比壓縮前的小,DSP將壓縮后數據寫入內部數據發送緩存器,反之則將壓縮前的數據直接寫入。同時DSP不斷監測內部緩存的狀態與外部輸出FIFO中數據狀態,當內部FIFO數據量大于512 B,同時外部FIFO不半滿,DSP從內部FIFO取出數據啟動MSBSP傳輸,將壓縮后的數據發送到FPGA。

3.3 無損壓縮算法及實現

通過試驗,比較ARC、WINZIP、WINRAR、字典編碼等常用的數據無損壓縮算法的壓縮結果。在壓縮去除率、壓縮速度以及穩定性等各方面綜合分析后,最終采用ARC編碼。ARC編碼采用依次遞推方式,對全序列連續編碼。ARC算法不是依據每個信源符號單獨映射后編碼,而是將整個信號符號序列全部映射到實數軸上(0,1)區間內的一個子區間內,子區間長度等于該序列的概率。

當整個序列映射完畢,就可以用一個概率值表示,可以在子區間內選擇一個有代表性的介于0和1之間的二進制小數作為實際的ARC編碼輸出,從而實現高效編碼。例如,算術編碼對某條輸入信號序列的輸出為1011001111,它表示小數0.101100111,即十進制數0.72。在VC中編譯調試后,再將算法移植到DSP開發平臺CCS3.3上繼續編譯直到通過[15-16]。

4 測試結果

數據壓縮器地面測試臺是專門用來對數據壓縮器進行單元測試的,它可以完全地模擬數據壓縮器在實際環境下的電氣工作環境。地面測試臺通過電纜傳輸到壓縮器信號輸入接口,壓縮器采集處理完畢,把數據通過422接口回傳到地面測試臺,測試臺將接收到的數據通過USB接口存儲到計算機以便事后分析處理。測試系統結構圖如圖6所示。

對采集到的6組遙測信號利用ARC算法進行32 min無損壓縮,測試得到162.8 MB的數據。可得壓縮去除率為:

1-162.8 MB/(6×30 kHz×8 bit×32×60 s)=52.9%

壓縮過程中SDRAM的最大占用比例為55%。通過MATLAB工具,對一路壓縮前的原始數據和解壓還原后數據進行頻域分析,圖7和圖8分別為兩者的幅頻特性圖,橫軸為頻率值,縱軸為幅值。實測噪聲的主要頻率分布在1~2 kHz的范圍內,解壓后,由于前端濾波器的作用,頻率大于10 kHz的部分基本被濾掉,但數據主要成分基本保持下來,能比較真實地反映數據的實際分布情況。

通過對比,可以看出原始數據與解壓后數據具有一致性,壓縮器的壓縮性能良好,可以較好地完成數據壓縮任務,而且在設計指標上考慮了一定冗余量,提高了壓縮裝置的可靠性,減輕遙測系統的傳輸帶寬壓力。

為有效降低遙測速變數據單信道容量,從而在有限的帶寬中增加更多的測試通道和測試參數,提高帶寬利用率,通過對壓縮機理的研究、壓縮算法的比較及相關硬件的設計,總體上實現了遙測噪聲數據的無損壓縮。通過單元測試,充分驗證了所設計的遙測噪聲數據無損壓縮裝置的正確性與可靠性。數據無損壓縮對當前許多應用領域都產生了深遠的影響,特別是在航天遙測領域,意義重大。

針對目前的研究情況,進一步需改進的問題包括:(1)數據采集部分可以在現有遙測噪聲數據采集的基礎上,結合FPGA的高性能和AD器件的更新,增加提高數據采集路數,提高采集速率和精度。(2)優化ARC編碼方式。可以結合其他的算法,實現算法自適應以增強數據處理適應能力,進一步提高壓縮器性能。(3)推廣技術的使用范圍,比如應用在數據采編、存儲等各個領域,以節省數據存儲容量開銷。

編輯:jq

-

USB接口

+關注

關注

9文章

702瀏覽量

55736 -

數據

+關注

關注

8文章

7114瀏覽量

89315 -

ARC

+關注

關注

0文章

42瀏覽量

16509 -

壓縮器

+關注

關注

0文章

26瀏覽量

7815

發布評論請先 登錄

相關推薦

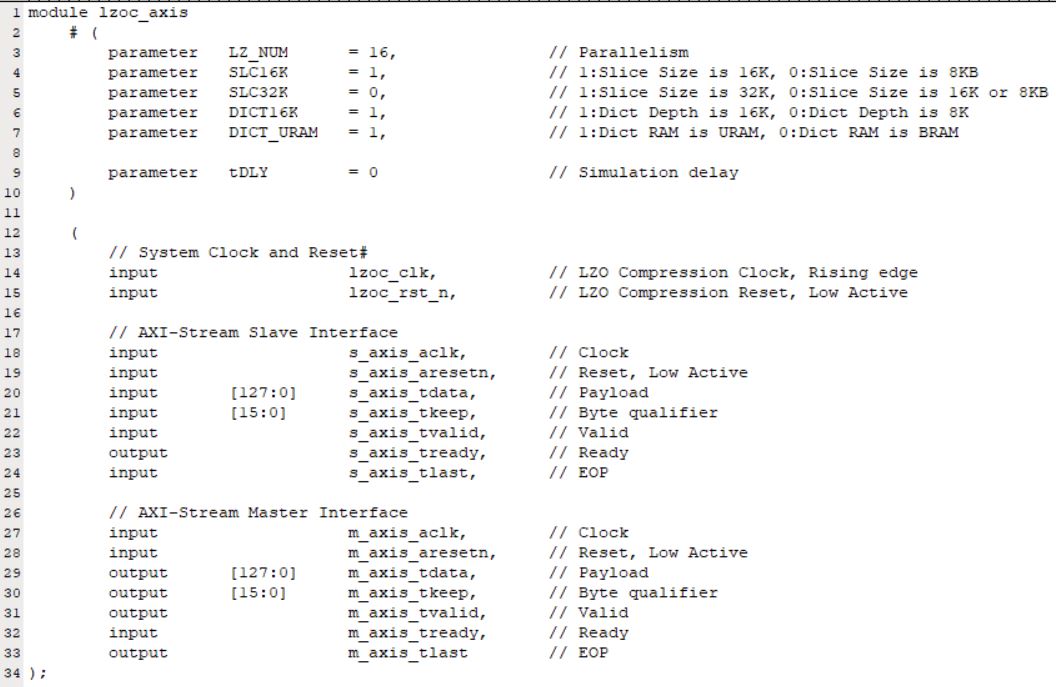

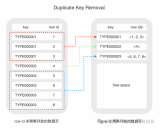

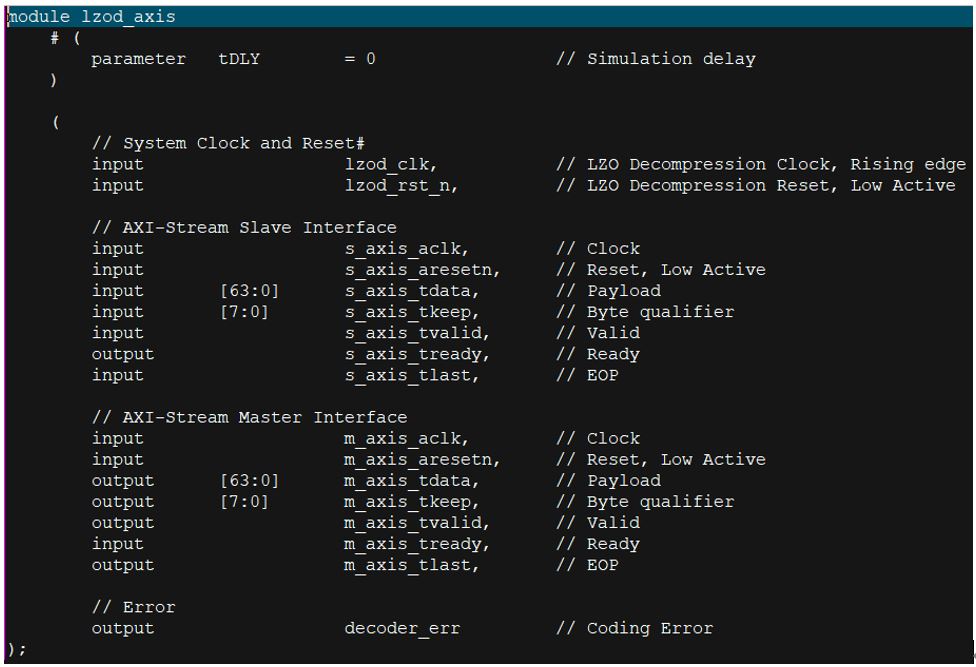

LZO Data Compression,高性能LZO無損數據壓縮加速器介紹,FPGA&ASIC

EE-257:面向Blackfin處理器的引導壓縮/解壓縮算法

【BearPi-Pico H3863星閃開發板體驗連載】LZO壓縮算法移植

PolarDB-MySQL引擎層的索引前綴壓縮能力的技術實現和效果

關于ARC算法的數據壓縮技術和實現

關于ARC算法的數據壓縮技術和實現

評論