如果你參加過IC校招面試,自然會被問到“setup/hold的概念,以及setup/hold違例怎么辦?”

這時候,你肯定會立馬在腦海中從打拍或者插buffer兩個答案中選一個。但是在實際項目中,往往沒有這么簡單。舉一個實際的場景:

AXI master和AXI slave這一簇信號出現(xiàn)setup時序違例怎么辦?

1、從AXI master 到AXI slave 出現(xiàn)setup違例;

2、從AXI slave 到AXI master出現(xiàn)setup違例;

3、兩者都出現(xiàn)setup時序違例。

所以AXI master和AXI slave之間的打拍會存在4中模式:

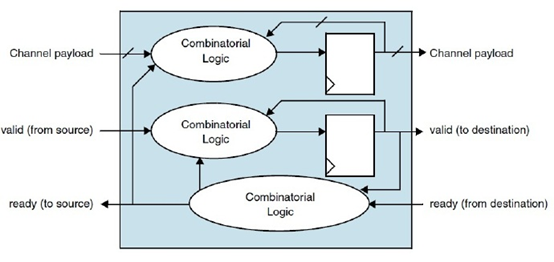

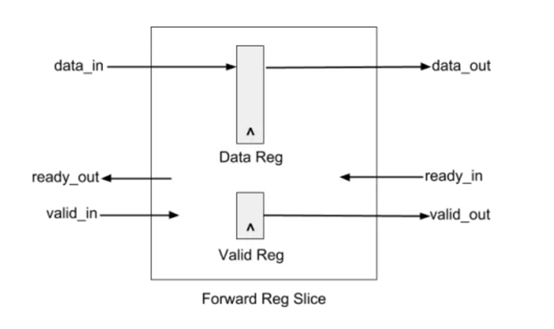

Forward Registered :對valid和payload路打拍

Backward Registered :對ready路打拍

Fully Registered :同時對valid/payload路和ready路打拍

Pass Through Mode:Bypass,均不打拍

這個問題沒那么容易或者說不能夠直接打拍,是因為這一簇信號遵循valid-ready協(xié)議,需要打拍的信號間存在時序的耦合。

所以問題就簡化成如何在遵循valid -ready協(xié)議的master和slave 之間完成“打拍”,或者說在打拍的同時處理valid-ready協(xié)議。

Forward Registered

always @(posedge clk or negedge rst_n)begin if (rst_n == 1‘d0) valid_dst 《= 1’d0; else if (valid_src == 1‘d1) valid_dst 《= #`DLY 1’d1; else if (ready_dst == 1‘d1) valid_dst 《= #`DLY 1’d0;end always @(posedge clk or negedge rst_n)begin if (rst_n == 1‘d0) payload_dst 《= ’d0; else if (valid_src == 1‘d1 && ready_src == 1’d1) payload_dst 《= #`DLY payload_src;end ready_src = (~valid_dst) | ready_dst

現(xiàn)在來分析下上述Forward Registered 打拍代碼的幾個輸出端口:

valid_dst:在master發(fā)請求(拉高valid_src)時拉高valid_dst,直到當(dāng)前master沒有valid請求并且slave可以接收請求(拉高ready_dst)時拉低valid_dst,表示一次傳輸完成。

payload_dst:在master發(fā)請求(拉高valid_src),并且前面沒有請求、請求已經(jīng)被接收或者正在被接收時將payload_src打拍賦給payload_dst。

其實master本身也會遵循valid-ready協(xié)議,payload_src和valid_src做同樣處理就行,即也可以在(valid_src == 1‘d1 && ready_src == 1’d0)時進(jìn)行賦值,因為此時payload_src輸入應(yīng)該約束保持原始數(shù)據(jù)。

ready_src:register slice或者slave可以接收數(shù)據(jù)時拉高ready_src.

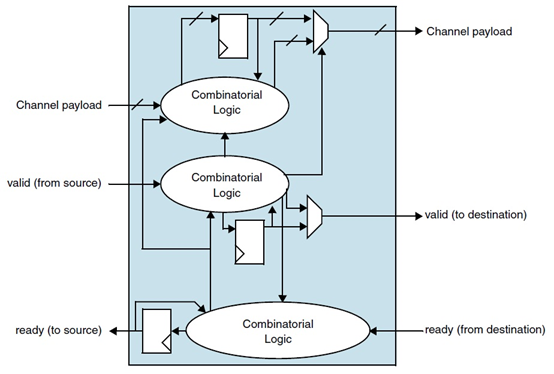

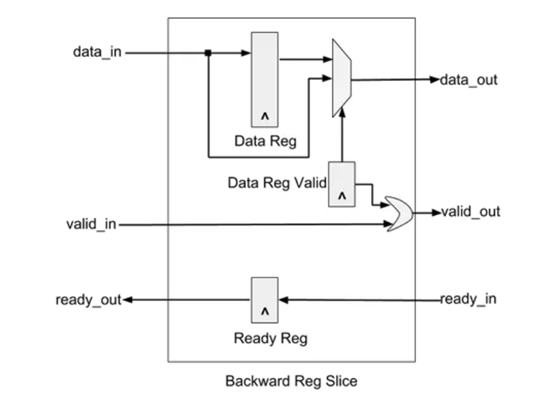

Backward Registered

always @(posedge clk or negedge rst_n)begin if (rst_n == 1‘d0) valid_tmp0 《= 1’d0; else if (valid_src == 1‘d1 && ready_dst == 1’d0 &&valid_tmp0 == 1‘d0) valid_tmp0 《= #`DLY 1’d1; else if (ready_dst == 1‘d1) valid_tmp0 《= #`DLY 1’d0;end always @(posedge clk or negedge rst_n)begin if (rst_n == 1‘d0) payload_tmp0 《= ’d0; else if (valid_src == 1‘d1 && ready_dst == 1’d0 &&valid_tmp0 == 1‘d0) payload_tmp0 《= #`DLY payload_src;end assign payload_dst = (valid_tmp0 == 1’d1) ?payload_tmp0 : payload_src; always @(posedge clk or negedge rst_n)begin if (rst_n == 1‘d0) ready_src 《= 1’d0; else ready_src 《= #`DLY ready_dst;end

Backward Registered 打拍相比較Forward Registered 會復(fù)雜點(diǎn),因為存在slave沒有ready時master發(fā)來請求,需要暫存payload的場景。

現(xiàn)在來分析下上述Backward Registered打拍代碼的幾個輸出端口:

ready_src:對ready通路直接進(jìn)行打拍。

valid_dst:當(dāng)slave沒有ready,master發(fā)來請求時拉高標(biāo)志位valid_tmp0,表示下一次slave準(zhǔn)備好之后應(yīng)該從register slice內(nèi)暫存的payload拿數(shù)據(jù)

payload_dst:當(dāng)slave沒有ready,master發(fā)來請求時暫存payload到payload_tmp。最終的payload_dst根據(jù)標(biāo)志位valid_tmp0從payload_tmp和payload_src之間選擇

Fully Registered

類似于,簡單理解就是個乒乓BUFFER,使用非空信號做valid_dst;payload的非滿信號做ready_src

Pass Through Mode

直接相連

通過上述分析,可以使用register slice mode參數(shù)化的庫,在后端要求AXI BUS打拍時直接調(diào)用,而無需重復(fù)造輪子。

編輯:lyn

-

IC

+關(guān)注

關(guān)注

36文章

5945瀏覽量

175506 -

時序

+關(guān)注

關(guān)注

5文章

387瀏覽量

37319 -

Setup

+關(guān)注

關(guān)注

0文章

30瀏覽量

11987 -

MASTER

+關(guān)注

關(guān)注

0文章

104瀏覽量

11283

原文標(biāo)題:打拍優(yōu)化時序不像聽起來那么簡單

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

關(guān)于磁通計你了解多少?

了解TI基于PCB布線規(guī)則的DDR時序規(guī)范

關(guān)于工廠人員定位,這幾點(diǎn)你了解嗎?

求助,關(guān)于STM32H7 FMC模式1的NADV時序問題求解

鎖存器的基本輸出時序

優(yōu)化 FPGA HLS 設(shè)計

OpenHarmony之開機(jī)優(yōu)化

你真的了解駐波比嗎?到底什么是電壓駐波比?

關(guān)于ECU 和 MCU ,你了解多少?

你真的了解110配線架嗎

fpga時序仿真和功能仿真的區(qū)別

快速全面了解大模型長文本能力

關(guān)于打拍優(yōu)化時序你真的全面了解嗎?

關(guān)于打拍優(yōu)化時序你真的全面了解嗎?

評論