學(xué)習(xí)內(nèi)容

學(xué)習(xí)關(guān)于AXI總線的信號接口的具體要求(包括不同通道之間的關(guān)系,握手機(jī)制說明等)和AXI4-Lite的相關(guān)信息,在文章后半部分對AXI讀寫時序進(jìn)行了簡要講解,主要針對ARM公司的IHI0022D進(jìn)行閱讀總結(jié)。

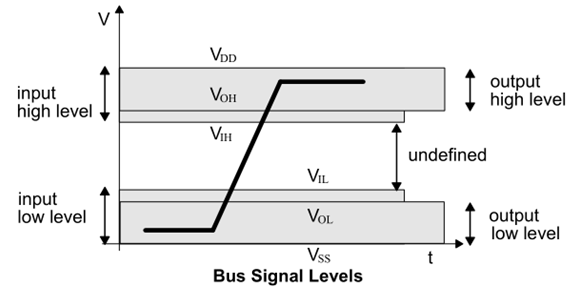

Clock and Reset

前面也提到了信號和復(fù)位的功能,這里對AXI全局時鐘(ACLK)和復(fù)位信號(ARESETn)做進(jìn)一步的解釋說明。Clock:每個AXI組件都要使用時鐘信號(ACLK)。

所有的輸入信號都在ACLK的上升沿上采樣。

所有輸出信號的變化必須發(fā)生在ACLK上升沿之后。

在主機(jī)接口和從機(jī)接口上,輸入和輸出信號之間不能有組合路徑。

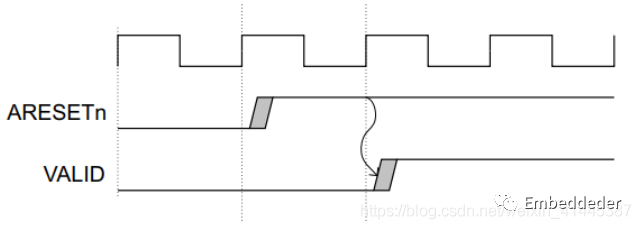

Reset:AXI使用一個單獨(dú)的低復(fù)位信號(ARESETn)。復(fù)位信號可以進(jìn)行異步復(fù)位,但是復(fù)位完必須與ACLK的上升沿同步。在復(fù)位過程中,要求:

主機(jī)接口必須驅(qū)動ARVALID、AWVALID、和WVALID為低電平。

從機(jī)接口必須驅(qū)動RVALID和BVALD 為低電平。

所有其他信號可以為任何值。

在完成復(fù)位后,允許master驅(qū)動ARVALID,、AWVALID、WVALID為高。但是上升沿信號是在ARESETn是拉高之后而且要在ACLK上升沿。如下圖:

Basic read and write transactions

在基本的讀寫傳輸中,要完成正常的傳輸功能要進(jìn)行握手并且遵守協(xié)議中對每個通道的信號的要求。

握手機(jī)制

所有五個通道都使用相同的VALID/READY握手處理來傳輸?shù)刂贰?shù)據(jù)和控制信息。這種雙向握手機(jī)制表示主機(jī)和從機(jī)都可以控制信息在主機(jī)和從機(jī)之間傳輸?shù)乃俾省?/p>

源端(master)生成VALID信號來指示地址、數(shù)據(jù)或控制信息何時傳輸可用。目的端(slave)生成READY信號來表示它可以接受該信息。傳輸只發(fā)生在VALID和READY信號都為高電平時。在主機(jī)接口和從機(jī)接口上,輸入和輸出信號之間不能有組合路徑。

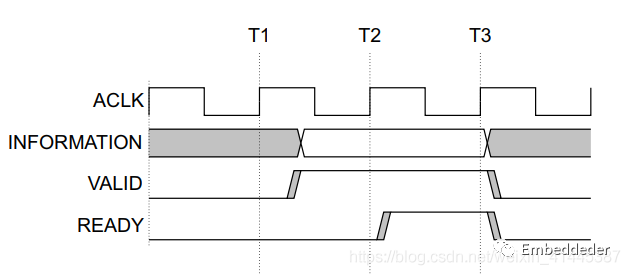

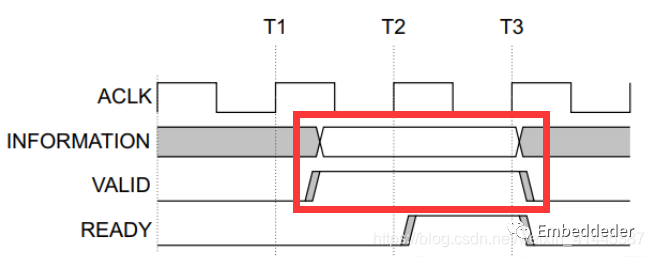

雙向握手協(xié)議表示主機(jī)和從機(jī)都可以控制信息在主機(jī)和從機(jī)之間傳輸?shù)乃俾省Q句話說也就是在傳輸中VALID和READY,都可以進(jìn)行等待對方從而完成數(shù)據(jù)傳輸。如下圖所示,下圖的VALID的上升沿在T1時刻之后完成拉高,在T2時刻VALID信號為高,而READY信號為低,所以要繼續(xù)等待READY信號拉高。在T2時刻的上升沿之后,READY拉高,在T3時刻上升沿時,READY和VALID信號都為高,所以數(shù)據(jù)傳輸發(fā)生。也就是下圖的數(shù)據(jù)傳輸發(fā)生在T3時刻。

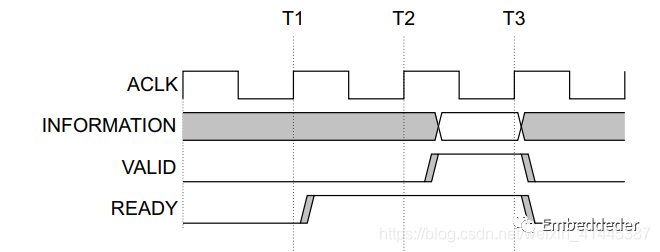

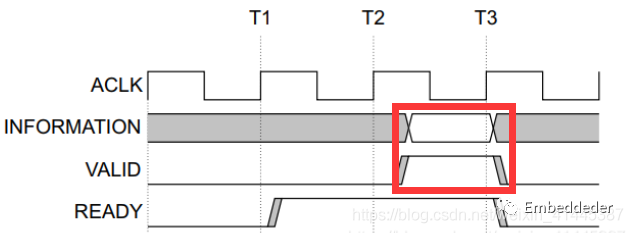

下圖的分析方法同上,在T1時刻READY和VALID信號都為低,不進(jìn)行數(shù)據(jù)傳輸;在T2時刻READY和VALID信號分別為高、低,不進(jìn)行數(shù)據(jù)傳輸;在T3時刻READY和VALID信號都為高,進(jìn)行數(shù)據(jù)傳輸。

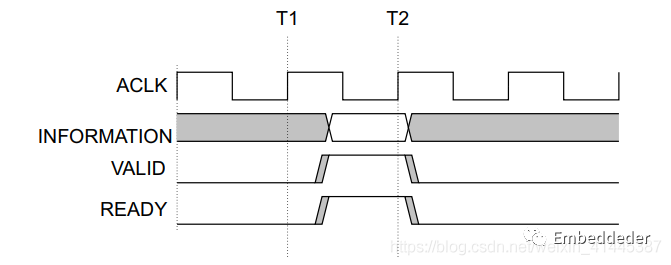

并且,READY和VALID可以同時設(shè)置為高進(jìn)行數(shù)據(jù)傳輸,如下圖,在T2時刻發(fā)生數(shù)據(jù)傳輸。

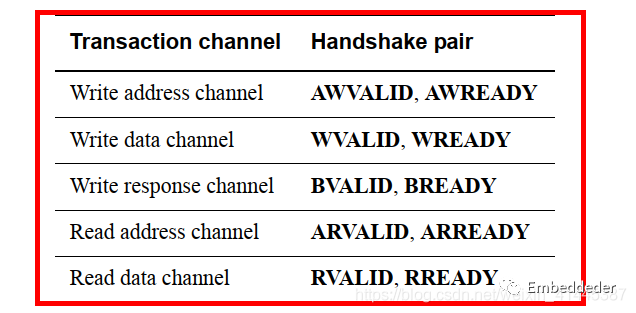

針對不同的信號通道,握手信號加上不同的前綴加以區(qū)分,如下表:

對于不同通道的握手信號,AXI協(xié)議有具體的建議要求:Write address channel主機(jī)可以在地址和控制信息都有效的時候拉高 AWVALID。當(dāng)AWVALID拉高后要保持不變,直到AWREADY也拉高并且時鐘產(chǎn)生上升沿之后。換句話說,在握手傳輸?shù)臅r,我們的數(shù)據(jù)信息和地址信息要保持不變,這樣才能確保傳輸?shù)臄?shù)據(jù)為有效可靠的。也就是AWVALID和信息數(shù)據(jù)是同步變化的。下面給出兩個示例:

AWREADY的默認(rèn)狀態(tài)可以是高或者低。AXI協(xié)議建議的默認(rèn)狀態(tài)為高。當(dāng)AWREADY為高時,從機(jī)能夠接受任何提供給它的有效地址。不建議默認(rèn)AWREADY狀態(tài)為低,因?yàn)樗鼜?qiáng)制進(jìn)行握手傳輸,至少需要兩個時鐘周期,一個周期拉高AWVALID,另一個周期拉高AWREADY。

Read address channel和上面的寫地址通道要求類似,主機(jī)可以在地址和控制信息都有效的時候拉高 AWVALID。當(dāng)AWVALID拉高后要保持不變,直到AWREADY也拉高并且時鐘產(chǎn)生上升沿之后。WREADY的默認(rèn)狀態(tài)可以是高或者低。AXI協(xié)議建議的默認(rèn)狀態(tài)為高。當(dāng)AWREADY為高時,從機(jī)能夠接受任何提供給它的有效地址。不建議默認(rèn)AWREADY狀態(tài)為低,因?yàn)樗鼜?qiáng)制進(jìn)行握手傳輸,至少需要兩個時鐘周期,一個周期拉高AWVALID,另一個周期拉高AWREADY。

Write response channel當(dāng)它驅(qū)動有效的寫響應(yīng)時,從機(jī)才能拉高BVALID信號。當(dāng)BVALID拉高后要保持不變,直到BREADY也拉高并且時鐘產(chǎn)生上升沿之后。BREADY的默認(rèn)狀態(tài)可以是高電平,但前提是在主機(jī)總是能夠在一個周期內(nèi)接受寫響應(yīng)的情況下。

Write data channel:在寫突發(fā)傳輸期間,當(dāng)主機(jī)驅(qū)動有效的寫數(shù)據(jù)時,才需要拉高WVALID信號。當(dāng)WVALID拉高后要保持不變,直到WREADY也拉高并且時鐘產(chǎn)生上升沿之后。WREADY的默認(rèn)狀態(tài)可以是高電平,但前提是從機(jī)總是能在一個周期內(nèi)接受寫數(shù)據(jù)。當(dāng)主機(jī)在突發(fā)傳輸中進(jìn)行最后一個數(shù)據(jù)傳輸時,必須拉高WLAST信號,用于指示傳輸結(jié)束。

Read data channel:當(dāng)它驅(qū)動有效的讀數(shù)據(jù)時,從機(jī)才能拉高RVALID信號。當(dāng)RVALID拉高后要保持不變,直到RREADY也拉高并且時鐘產(chǎn)生上升沿之后。即使從機(jī)只有一個讀數(shù)據(jù)信息,它也必須在響應(yīng)數(shù)據(jù)請求時拉高RVALID信號。主機(jī)接口使用RREADY信號來表示它接受數(shù)據(jù)狀態(tài)。RREADY的默認(rèn)狀態(tài)可以為高電位,但前提是無論何時啟動讀操作,主機(jī)都能立即接受讀數(shù)據(jù)。當(dāng)從機(jī)在突發(fā)傳輸中進(jìn)行最后一個數(shù)據(jù)傳輸時,必須拉高RLAST信號,用于指示傳輸結(jié)束。

通道之間的關(guān)系

AXI協(xié)議中需要保持以下關(guān)系:

在寫操作中,寫響應(yīng)必須始終跟隨它是其中一部分的最后一個寫傳輸。

讀取數(shù)據(jù)必須始終跟在與數(shù)據(jù)相關(guān)的地址后面。

通道握手必須符合在通道握手信號之間的依賴關(guān)系。

通道握手信號之間的依賴關(guān)系

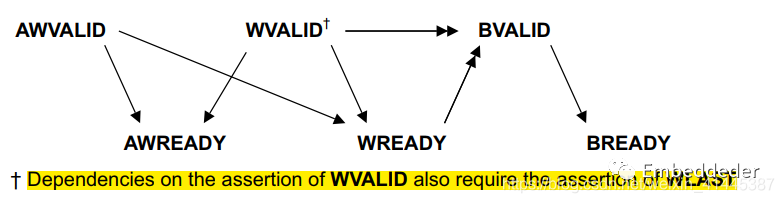

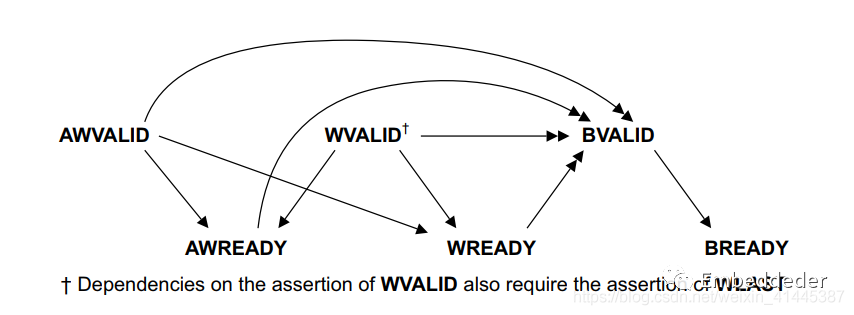

通道握手信號之間的依賴關(guān)系,,由下面的流程圖進(jìn)行描述,這里先進(jìn)行圖示說明:在依賴關(guān)系圖中,單箭頭指向可以在箭頭指向的信號之前或之后拉高信號;雙箭頭指向的信號必須在箭頭指向的信號斷言之后才能拉高。

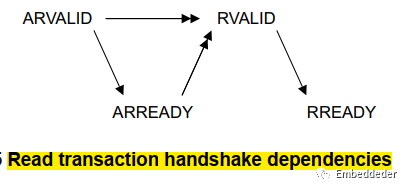

讀操作依賴關(guān)系

上圖顯示讀操作握手信號的依賴關(guān)系,在讀操作中:

從機(jī)必須等待ARVALID和ARREADY都拉高后,RVALID才能進(jìn)行拉高指示數(shù)據(jù)有效。

對于ARVALID和ARREADY的順序,可以任意設(shè)置先后順序,從機(jī)可以等待ARVALID拉高后,再拉高ARREADY,也可以相反,也可以同時拉高。

對于RVALID和RREADY不用關(guān)心順序,主機(jī)可以任意設(shè)置先后順序。可以先后,可以同時。

寫操作依賴關(guān)系

上圖顯示寫操作握手信號的依賴關(guān)系,在寫操作中:

主機(jī)在拉高AWREADY or WREADY不需要關(guān)心從機(jī)AWVALID or WVALID先后順序。

從機(jī)在BVALID拉高之前,WVALID和WREADY必須被拉高。

從機(jī)必須WLAST拉高之后,才能拉高BVALID,因?yàn)閷戫憫?yīng)(BRESP)在寫操作的最后一次數(shù)據(jù)傳輸之后,才發(fā)出信號。

從機(jī)不用關(guān)心BVALID和BREADY的先后順序。

寫響應(yīng)依賴關(guān)系

上圖顯示寫響應(yīng)握手信號的依賴關(guān)系,在寫響應(yīng)中:

單頭箭頭指向可以在箭頭指向的信號之前或之后拉高信號

從機(jī)須等待AWVALID、AWREADY、WVALID和WREADY都拉高之后,BVALID才能拉高使能。

從機(jī)必須WLAST拉高之后,才能拉高BVALID,因?yàn)閷戫憫?yīng)(BRESP)在寫操作的最后一次數(shù)據(jù)傳輸之后,才發(fā)出信號。

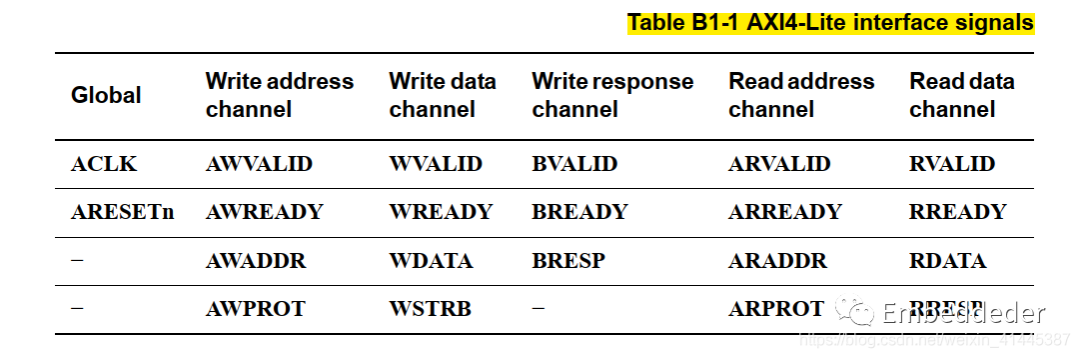

AXI4-Lite協(xié)議

AXI4-Lite和AXI4類似,當(dāng)不需要完整AXI4功能的時,進(jìn)行一些簡單的控制寄存器的讀寫。AXI4-Lite協(xié)議簡單描述如下:

AXI4-Lite協(xié)議的所有傳輸?shù)耐话l(fā)長度都是1(相當(dāng)于不支持突發(fā)傳輸)。

所有數(shù)據(jù)訪問都使用數(shù)據(jù)總線的全部位寬,支持32位或64位的數(shù)據(jù)總線寬度。

所有訪問都是不可修改的,不可緩沖的。

不支持獨(dú)占訪問。

接口定義

相比前面介紹的AXI4-Full,這里的信號端口就少了很多。但對于相同名字的接口信號含義是相同的,功能相同。

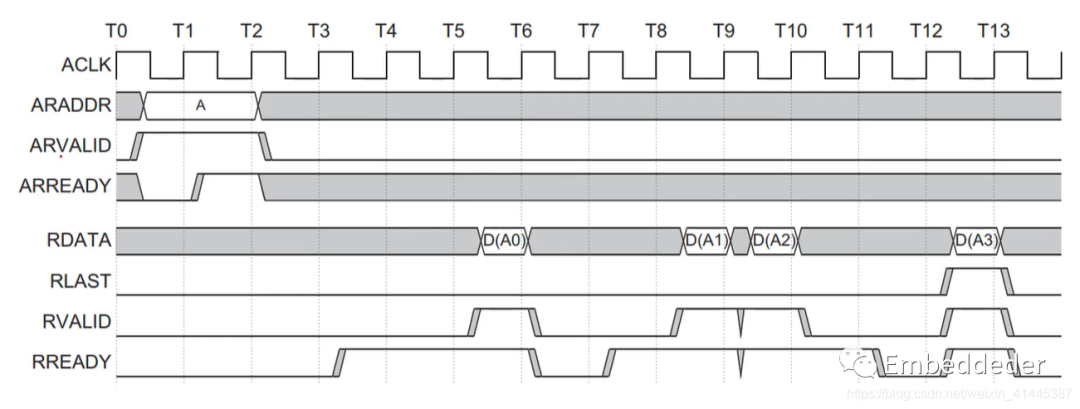

AXI總線協(xié)議時序

AXI突發(fā)讀

下圖所示,當(dāng)ARVALID信號和ARREADY信號都拉高時地址有效(地址信息和ARVALID是同步的),也就是在T2時刻讀取到所要讀取的地址,然后等待RVALID和RREADY都拉高,即可讀取到數(shù)據(jù),也就是在T5時刻內(nèi)讀取到第一個數(shù)據(jù)A0(數(shù)據(jù)和RVALID是同步的),依次讀取A1、A2、這里的時序圖定義A3為最后一次傳輸,所以RLAST也被拉高。

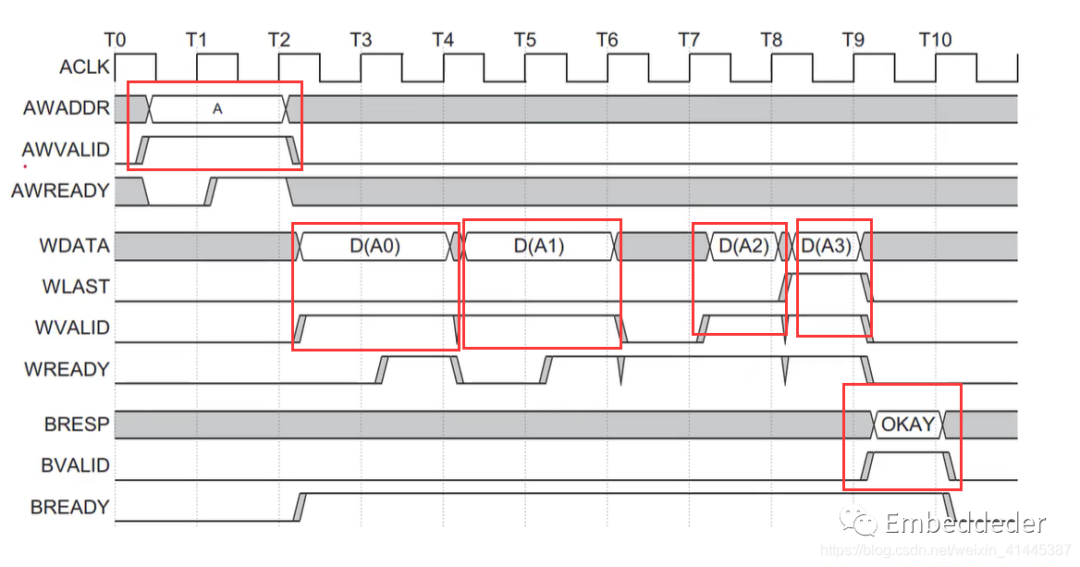

突發(fā)寫

下圖所示,當(dāng)AWVALID信號和AWREADY信號都拉高時地址有效(地址信息和AWVALID是同步的),也就是在T2時刻上升沿讀取到所要寫入的地址。然后主機(jī)發(fā)送寫入的數(shù)據(jù)(數(shù)據(jù)和WVALID信號是同步的),依次寫入A0、A1、A2、A3,當(dāng)寫入最后一個數(shù)據(jù)時,WLAST信號也要拉高,當(dāng)寫操作完成后,從機(jī)要發(fā)送一個響應(yīng)信號,這個信號也是在BVALID和BREADY為高時有效。

編輯:jq

-

數(shù)據(jù)

+關(guān)注

關(guān)注

8文章

7002瀏覽量

88943 -

主機(jī)

+關(guān)注

關(guān)注

0文章

993瀏覽量

35114 -

AXI總線

+關(guān)注

關(guān)注

0文章

66瀏覽量

14261

原文標(biāo)題:ZYNQ-AXI總線的信號接口要求以及時序關(guān)系

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

ADS8698有上電時序要求嗎?

AMBA AXI4接口協(xié)議概述

接口芯片的讀寫信號與系統(tǒng)的關(guān)系

瀚海微SD NAND之SD 協(xié)議(31)總線的信號和時序

Xilinx NVMe AXI4主機(jī)控制器,AXI4接口高性能版本介紹

FPGA 高級設(shè)計(jì):時序分析和收斂

有關(guān)PL端利用AXI總線控制PS端DDR進(jìn)行讀寫(從機(jī)wready信號一直不拉高)

SoC設(shè)計(jì)中總線協(xié)議AXI4與AXI3的主要區(qū)別詳解

FPGA通過AXI總線讀寫DDR3實(shí)現(xiàn)方式

PCIe-AXI-Cont用戶手冊

時序電路的分類 時序電路的基本單元電路有哪些

漫談AMBA總線-AXI4協(xié)議的基本介紹

CAN總線接口保護(hù)方案

淺述ZYNQ-AXI總線的信號接口要求以及時序關(guān)系

淺述ZYNQ-AXI總線的信號接口要求以及時序關(guān)系

評論