· 寄語 ·

小伙伴們,我們又見面了,上一期?「IC手記 ? 點沙成金的半導體行業」給大家介紹了芯片簡史和PA測試的內容,這一期,我們繼續為大家帶來數字芯片的重要分支:存儲器,以及DDR5技術及完整的測試方案。

存儲器簡史

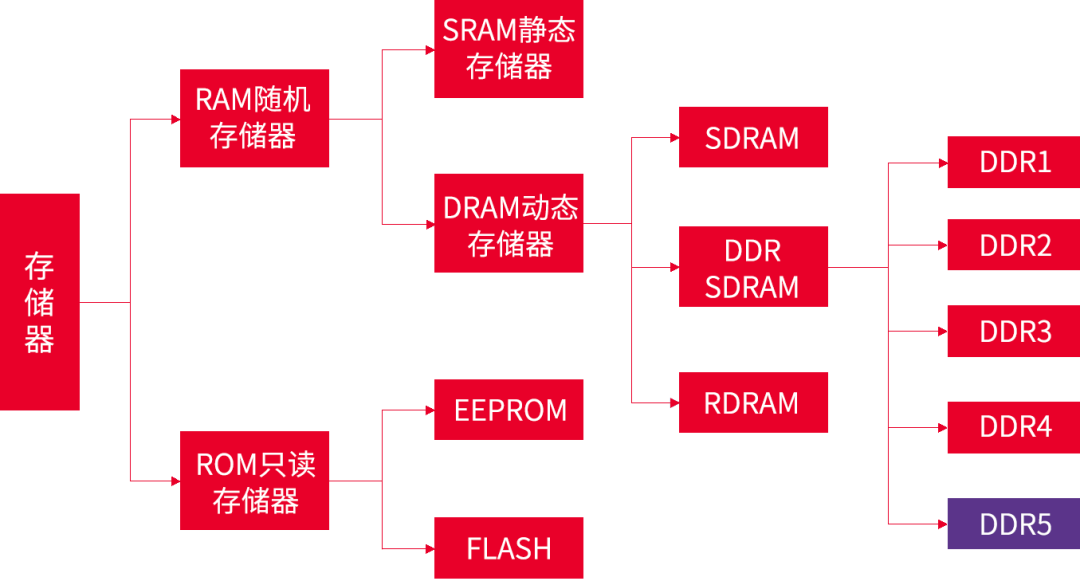

存儲芯片是數字芯片的重要組成部分,能夠存儲程序和各種數據,并能在計算機運行過程中高速、自動地完成程序或數據的存取,如下是存儲芯片的基本分類:

圖:存儲器基本分類

ROM:只讀存儲器

ROM所存數據,一般是裝入整機前事先寫好的,整機工作過程中只能讀出,ROM所存數據穩定,斷電后所存數據也不會改變。

RAM:隨機存取存儲器

RAM是與CPU直接交換數據的內部存儲器,它可以隨時讀寫,速度快,通常作為操作系統或其他正在運行中的程序的臨時數據存儲媒介,當電源關閉時RAM不能保留數據。

DDR SDRAM,也是我們今天的主角,在SDRAM的基礎上發展而來,這種改進型的DRAM和SDRAM是基本一樣的,不同之處在于它可以在一個時鐘讀寫兩次數據,這樣就使得數據傳輸速度加倍了,也是目前電腦中用得最多的內存,而且具有成本優勢。DDR已經發展至今已經進化到DDR5,與DDR4相比,DDR5 在強大的封裝中帶來了全新的架構,下面我們會著重介紹DDR5技術及測試方案。

DDR5簡介

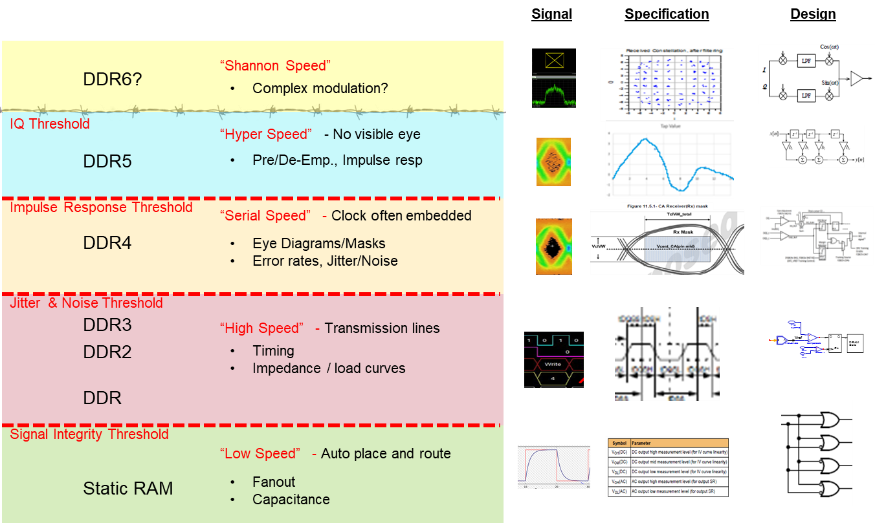

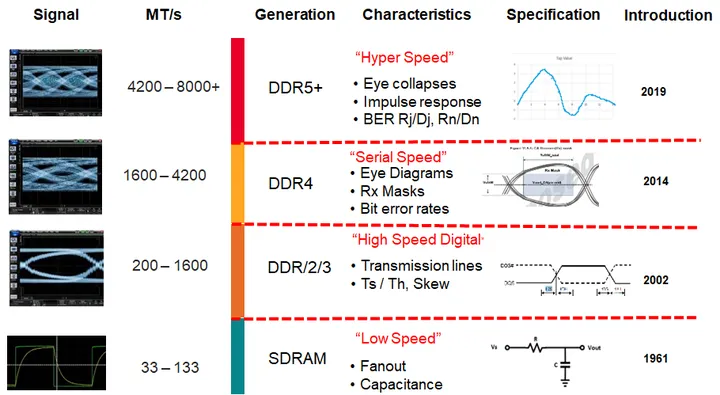

DDR總線經過演進,如今已經發展到DDR5,下圖是DDR總線的演進路線:

圖:DDR技術演進

無論是從移動計算、PC、服務器到圖形計算等領域,總線從早期的低速簡單時序特性,到DFE等技術在DDR5中被應用,內存總線在逐步引入SerDes技術,并逐漸逼近通道傳輸極限。隨著DDR5規范的正式發布,步入2021年,DDR5已開始被服務器CPU和存儲器廠商所采用,其具備更高的數據速率、更低的能耗和更高的密度。

DDR5具備如下幾個特點:

· 更高的數據速率 ·

DDR5最大數據速率為 6400MT/s(百萬次/秒),而 DDR4 為 3200MT/s,DDR5 的有效帶寬約為 DDR4 的 2 倍。

· 更低的能耗 ·

DDR5的工作電壓為1.1V,低于DDR4的1.2V,能降低單位頻寬的功耗達20%以上

· 更高的密度 ·

DDR5 將突發長度增加到 BL16,約為 DDR4 的兩倍,提高了命令/地址和數據總線效率。相同的讀取或寫入事務現在提供數據總線上兩倍的數據,同時限制同一存儲庫內輸入輸出/陣列計時約束的風險。

此外,DDR5 使存儲組數量翻倍,這是通過在任意給定時間打開更多頁面來提高整體系統效率的關鍵因素。所有這些因素都意味著更快、更高效的內存以滿足下一代計算的需求。

應對DDR5測試的挑戰

如前文所屬,DDR5具備諸多的優勢,也極大增加了測試的難度及復雜度。作為測試行業的領導者,是德科技一直以來積極推動JEDEC DDR5規范測試方案的開發,與行業內的頭部伙伴共同推動規范的演進和實施,從DDR總線仿真、測試夾具的定義和開發、Rx測試及Tx測試苛刻的抖動質量要求、再到協議測試方法的開發。是德科技也是唯一一家提供完整DDR5的Tx/Rx物理層到協議測試的方案提供商。

針對DDR生態鏈中的不同產品形態,是德科技都提供完整的解決方案,如下圖,包括發射端測試、接收端測試、協議測試等等,我們在下文會分別予以介紹。

1

DDR5發送端測試

隨著信號速率的提升,SerDes技術開始在DDR5中采用,如會采用DFE均衡器改善接收誤碼率,另外DDR總線在發展過程中引入訓練機制,不再是簡單的要求信號間的絕對建立保持時間,在DDR4的時代開始使用眼圖的概念,在DDR5時代,引入抖動成分概念,從成因上區分解Rj,Dj等,對芯片或系統設計提供更具體的依據;在抖動的參數分析上,也增加了一些新的抖動定義參數,并有嚴苛的測量指標。

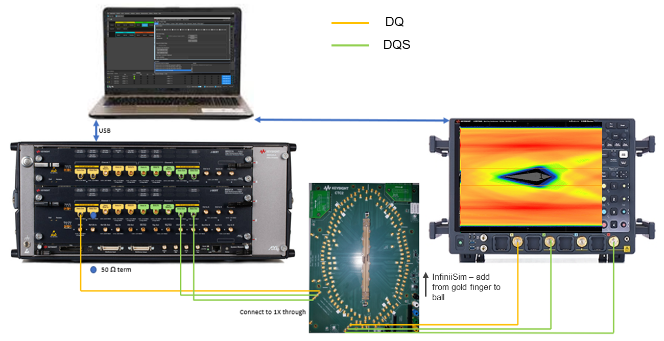

針對這些要求,是德科技提供了完整的解決方案。基于是德科技10bit ADC的UXR示波器,配合D9050DDRC軟件,及高阻RC探頭MX0023A,及Interposer,可以實現對DDR信號的精確表征。

2

DDR5 接收端測試

隨著DDR5信號目標速率持續提升,鏈路的ISI和串擾問題愈發明顯,在DDR芯片顆粒端信號可能已經閉合,為了保證誤碼率,在DDR5芯片中引入了VGA+DFE的結構,使得均衡后內部眼圖重新展開。所以傳統的只在DDR memory端測試眼圖的方法在DDR5時代并不是一個合理的方法,是德科技針對這種情況,推動了DDR5新的測試方法,即Rx測試。

下圖為基于UXR示波器及M8020A誤碼儀的接收端校準和測試組網:

是德科技和協會及相關公司共同定義了測試夾具,如CTC2測試基板夾具,Device芯片測試夾具卡。接收端測試包括如下測試內容:DQS Voltage Sensitivity,DQ Voltage Sensitivity,DQS Jitter Sensitivity,DQ Stressed Eye,CA Voltage Sensitivity,CA Stressed Eye,DQS2DQ,DFE Characterization等。

3

DDR5協議測試

JEDEC的規范中,定義了如下圖中的參數要求,是德科技的U4164A邏輯分析儀,可用于DDR5協議測試。B4661A軟件可以支持這些參數的實時和后分析功能,分析判斷測試結果是否符合規范的范圍要求,并且可以跟蹤測量結果,對于違規的測量參數可以跟蹤到波形界面,從而定位命令和操作的根源問題。

4

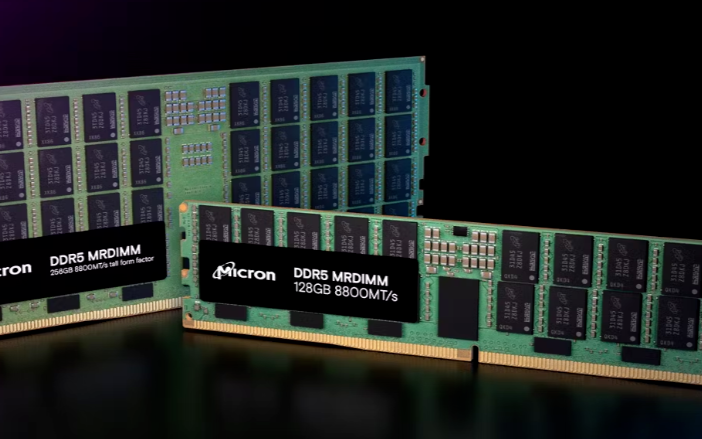

DDR5芯片顆粒及DIMM測試

針對DDR5,基于U4164A x 4及Futureplus公司FS2600 DDR5 RDIMM/LRDIMM Interposer夾具。另外,針對芯片顆粒的測試,Keysight也提供W5643A DRAM BGA Interposer。

5

DDR5測試總結

是德科技為DDR行業提供了最完整的解決方案。

原文標題:IC手記 ? 存儲器芯片及DDR5

文章出處:【微信公眾號:是德科技KEYSIGHT】歡迎添加關注!文章轉載請注明出處。

責任編輯:haq

-

芯片

+關注

關注

455文章

50714瀏覽量

423154 -

存儲器

+關注

關注

38文章

7484瀏覽量

163764 -

DDR

+關注

關注

11文章

712瀏覽量

65318

原文標題:IC手記 ? 存儲器芯片及DDR5

文章出處:【微信號:是德科技KEYSIGHT,微信公眾號:是德科技KEYSIGHT】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

DDR3、DDR4、DDR5的性能對比

DDR5內存的工作原理詳解 DDR5和DDR4的主要區別

星坤DDR5 SMT RDIMM金手指連接器:云端存儲與高性能計算的未來

DRAM大廠第三季DDR5價格大幅上調

Introspect DDR5/LPDDR5總線協議分析儀

DDR5 MRDIMM內存標準將發,存儲廠商方案先行

完整DDR,DDR2,DDR3 和LPDDR3 存儲器電源解決方案同步降壓控制器數據表

DDR5測試技術更新漫談

DDR5內存接口芯片組如何利用DDR5 for DIMM的優勢?

具有同步降壓控制器、2A LDO和緩沖基準的TPS51916完整DDR2、DDR3、DDR3L和DDR4存儲器電源解決方案數據表

TPS65295完整 DDR4 存儲器電源解決方案數據表

存儲器以及DDR5技術及完整的測試方案

存儲器以及DDR5技術及完整的測試方案

評論