5G時代下,各類消費電子產(chǎn)品趨向輕巧、多功能、低功耗發(fā)展,半導(dǎo)體封裝正向著高度集成的方向發(fā)展。

而為了在更小的封裝面積下容納更多的引腳數(shù),晶圓級封裝(WLP)也開始受到越來越多的關(guān)注。

一、什么是晶圓級封裝?

晶圓級封裝,即將晶圓作為加工對象,直接在整片晶圓上進行CSP封裝及測試,最后再切割成單個器件,同時具備更多的功能集成,尺寸也更小,可直接貼裝到基板或印刷電路板上。

1.傳統(tǒng)封裝

2.晶圓級封裝

這樣改變之后,芯片設(shè)計和封裝設(shè)計就能統(tǒng)一考慮,能夠簡化供應(yīng)鏈、縮短生產(chǎn)周期且降低成本。

目前所謂的晶圓級封裝一般分為Fan-in和Fan-out兩種,下面展開講講。

二、Fan-in封裝

Fan-in封裝即標準的WLP工藝,封裝后的尺寸與IC裸晶的原尺寸幾乎等同,直接貼裝到基板或印刷電路板上,大大降低加工成本、提升加工效率。

由于中間沒有載體,焊球直接植于硅基材上,其敏感度遠超BGA,有效增加了數(shù)據(jù)傳輸?shù)念l寬并減少了信號損耗,數(shù)據(jù)傳輸速度和穩(wěn)定性大幅提升;同時沒有塑封料或陶瓷包封,其散熱能力也更強。

Fan-in封裝已成為目前移動/消費應(yīng)用的主流封裝技術(shù),與基于基板的封裝相比,它提供了成本更低的解決方案。

三、Fan-out封裝

Fan-out封裝是基于晶圓重構(gòu)技術(shù),將測試合格的芯片重新埋置到晶圓上,然后按照與標準WLP 工藝類似的步驟進行封裝,得到的實際封裝面積要大于裸晶。

由于實際封裝面積要大于芯片面積,在面積擴展的同時也可以增加其它有源器件及無源元件,形成SiP。

Fan-out封裝可實現(xiàn)小芯片和異構(gòu)集成,預(yù)計將在未來幾年內(nèi)隨著5G、AI和自動駕駛的發(fā)展得到普及。

先進封裝技術(shù)已經(jīng)成為高性能芯片的必選項,在可預(yù)見的未來,晶圓級封裝對傳統(tǒng)封裝技術(shù)的替代將成為趨勢。

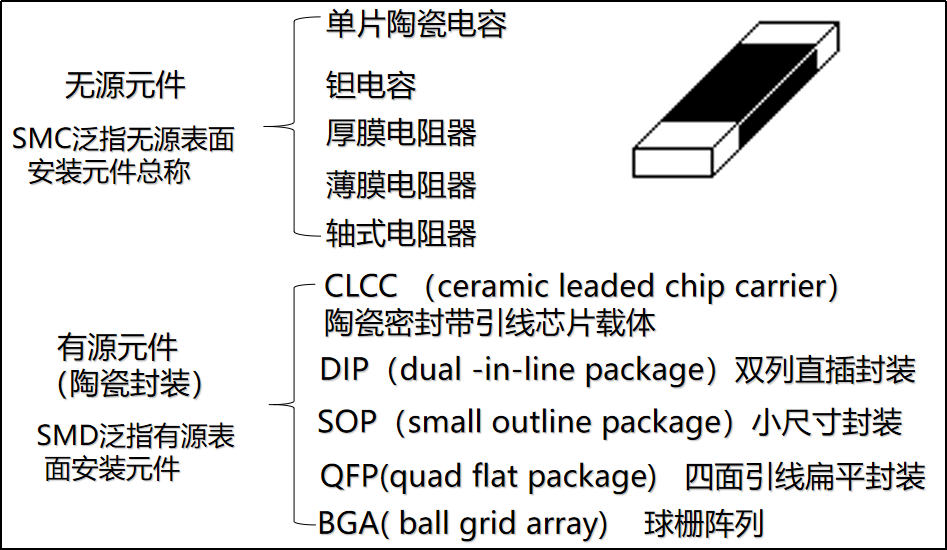

從上文我們可以看到,晶圓級封裝與傳統(tǒng)封裝最關(guān)鍵的區(qū)別就是——將封裝好的晶圓切割成片后,直接貼裝到基板或印刷電路板上,單個元件體積縮小了數(shù)倍。

不同封裝技術(shù)下單個元件的貼裝面積

不僅如此,晶圓級封裝的焊球直徑更小,焊球間距更小(范圍在0.3mm-0.5mm之間),所以在固晶時需要更精準的對位及取放壓力。

這意味著,采用更柔性、更好控制的高精度電機來進行操作,才更能匹配先進晶圓封裝的貼裝需求。

國奧直線旋轉(zhuǎn)電機助力提供更柔性固晶方案,雙向線性致動器和軟著陸能夠精準地控制力量,重復(fù)定位精度可達+/- 2μm,能更輕柔地觸碰晶片表面,進行準確的真空取放。

±0.01N的精準力控處于全球領(lǐng)先水平,協(xié)助提升生產(chǎn)設(shè)備的柔性化程度,提高生產(chǎn)效率和產(chǎn)品良率,共計申請相關(guān)核心專利知識產(chǎn)權(quán)和軟件著作權(quán)100余項。

國奧電機致力于為半導(dǎo)體封測、精密制造、智慧醫(yī)療、3C自動化等產(chǎn)業(yè)領(lǐng)域提供先進裝備及解決方案,歡迎預(yù)yue選型~

來源:國奧科技GOALTECH、半導(dǎo)體行業(yè)觀察

責(zé)任編輯:haq

-

晶圓

+關(guān)注

關(guān)注

52文章

4936瀏覽量

128114 -

封裝

+關(guān)注

關(guān)注

127文章

7948瀏覽量

143114 -

電機

+關(guān)注

關(guān)注

142文章

9044瀏覽量

145801

發(fā)布評論請先 登錄

相關(guān)推薦

SMT表面貼裝技術(shù)的優(yōu)勢

常見的PCB元件封裝類型

貼片電感有哪些封裝類型

速程精密高速貼裝頭引領(lǐng)智能制造新速度

SMT貼裝元件指南丨不同類型表面安裝器件大全

探索高精密板SMT貼裝:小元件,大乾坤

貼片電阻和表面貼裝電阻有什么不同?

元件貼裝推拉力測試,提升PCBA行業(yè)之生產(chǎn)品質(zhì)

Vishay推出采用超小型MiniLED封裝的新型藍色和純綠色表面貼裝LED

不同封裝技術(shù)下單個元件的貼裝面積

不同封裝技術(shù)下單個元件的貼裝面積

評論