IBM最近宣布,位于紐約Albany的IBM Research實驗室采用納米片(nanosheet)技術研制出2nm芯片,據稱在150mm2的平面上(約指甲蓋大小)嵌入了 500 億個晶體管,平均每平方毫米3.3 億個。而臺積電和三星的7納米芯片容納的晶體管數量大約在每平方毫米9,000萬個;三星的5LPE為1.3億個;臺積電的5納米芯片則是1.7億個。

IBM 2nm芯片的性能/功耗提升靠什么技術?

據IBM Research負責人Darío Gil稱,采用2納米工藝制造的處理器相比現在許多筆記本電腦及手機使用的主流7納米處理器速度提升45%,能效提高75%。也就是說,其2納米架構可以在與現有7納米相同的性能下,僅耗用25%的電力。以最新的智能手機為例,可能四天才需要充一次電。而在筆記本電腦、自動駕駛等對能耗不敏感的使用場景下,則能帶來更高的算力。

這種2nm芯片還可用于數據中心、太空探索、人工智能、5G、6G 乃至于量子計算。但要真正投片量產還要等待幾年時間,估計至少要到2024年。大約4年前,IBM宣布與合作伙伴格芯和三星共同開發出采用納米片晶體管結構的5納米芯片。

據稱在指甲蓋大小的面積上集成了30億個晶體管,而其前一代7納米測試芯片(于2015年發布)的容量為20億個晶體管。然而,今年下半年才能看到IBM的7納米芯片投入商用。

雖然IBM不再自己生產芯片(將其晶圓廠賣給了格芯),但位于紐約Albany的IBM Research實驗室仍繼續研發最前沿的半導體制造技術,7nm、5nm和2nm芯片都是業界率先研制成功的,而且都是采用這種業界通常稱為柵極全環繞型(GAA,Gate-All-Around)的納米片(nanosheet)技術。

從Planar到FinFET,再到GAA

可以容納數十億個晶體管的先進微處理器無疑是世界上最復雜的系統之一,但其本質上卻是一個非常簡單的單元:晶體管。無論晶體管數量多大,它們幾乎都是相同的,功能上就是一個簡單的開關。因此,提高性能并增加這些晶體管的密度是使微處理器及其驅動的計算機高效工作的最直接方法。這就是多年來摩爾定律正常運作的前提,但現在幾乎要走到盡頭了。

開發更小且更好的晶體管在技術上越來越困難,而且制造成本越來越高。目前,全世界只有英特爾、三星和臺積電(TSMC)三家公司能夠生產7nm及以下工藝的芯片。雖然臺積電和三星仍在不斷往5nm、3nm甚至2nm工藝進軍。

但它們已經不是傳統意義上晶體管線寬的準確物理概念了,只是廠商在最先進工藝競賽中使用的營銷代號而已。盡管如此,它們仍然可以反映出集成電路中晶體管的結構特征和小型化程度。

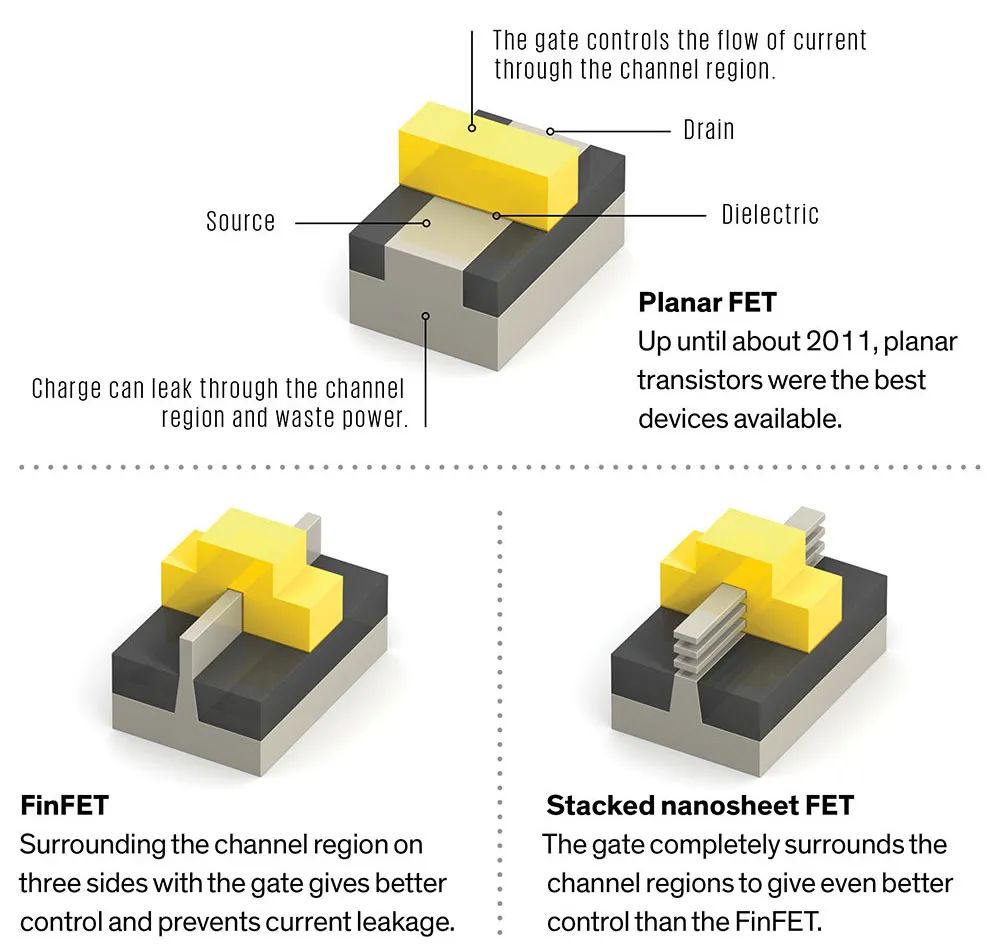

自1959年問世以來,金屬氧化物半導體場效應晶體管(MOSFET)一直采用相同的基本結構:柵極疊層、溝道區、源極和漏極。而且MOSFET的源極和漏極基本放置于硅平面上,柵極疊層位于溝道區的正上方,這就是沿用多年的平面型FET(Planar FET)。然而,這種結構的一個缺點是電荷有可能通過溝道區域泄漏,導致晶體管永遠不會完全截止,從而浪費功率并產生熱量。

為了阻止不必要的電荷流,必須將溝道區域做得更薄,以限制電荷流動的路徑,而且柵極需要在更多側面包圍溝道。為解決這一問題,加州大學伯克利分校的胡正明教授于2000年提出了鰭式場效晶體管(FinFET)方案。

在這種設計中,溝道區域在其側面向上傾斜,從而在源極和漏極之間形成一個細長的硅鰭,為電流提供了更寬的路徑。然后將柵極和電介質覆蓋在鰭片的三個側面,將硅鰭包圍起來。2011年,英特爾開始利用FinFET結構生產22納米的芯片。這一創新的晶體管結構把摩爾定律的有效期延長了數十年,如今22納米以下的工藝都是采用FinFET結構。

從Planar FET到FinFET再到疊層納米片FET的演進(來源:IEEE SPECTRUM)

FinFET無疑取得了巨大的成功,自2011年以來它一直是摩爾定律最后階段中先進數字邏輯芯片的主動力。英特爾、三星和臺積電等公司都在繼續使用FinFET研發7nm和5nm的芯片。但是,到了3nm節點,FinFET有點力不從心了。

FinFET雖然解決了平面型FET的電荷泄漏問題,但它也引入了新的設計限制。要知道,為達到最佳效果,我們必須在晶體管的速度、功耗、制造復雜性和成本之間做出取舍。這種折衷與溝道寬度(Weff )有很大關系,更大的寬度意味著可以驅動更多的電流并更快地開關晶體管。但這需要更復雜、成本更高的制造工藝。

對于平面型FET結構,可以簡單地通過調整溝道的幾何形狀來實現折衷。但是FinFET的鰭片卻沒有這樣的靈活性,因為連接晶體管以形成電路的金屬互連位于晶體管自身上方的層中。因此,在不干擾互連層的前提下,晶體管鰭片的高度(相當于平面型FET的寬度)實際上不能有很大的變化。如今,芯片設計人員通過設計具有多個鰭的晶體管來解決這個問題。

FinFET的另一個缺點是,其柵極僅在三個側面圍繞矩形硅鰭,而底側仍與硅主體相連。當晶體管關閉時,仍有一些泄漏電流流過。業界研究人員認為,要獲得對溝道區域的完全控制,柵極需要將其四面完全包圍。

從1990年開始,研究人員就著手將此想法付諸實際,并研制出首個完全圍繞溝道區域的柵極硅器件。從那以后,更多的研究人員投入研發所謂的柵極全環繞型(GAA)器件。到2003年,一直尋求最小化電流泄漏的研究人員將溝道區域變成了一條狹窄的納米線(nanowire),該納米線連接源極和漏極,其四周都被柵極包圍了。

那么,是否可以基于全包圍的納米線設計新的晶體管呢?這時溝道寬度又成了攔路虎。雖然較細的導線幾乎完全阻止了電子的逃逸,在晶體管處于關閉狀態時確實達到了真正的關閉。但是,當晶體管導通時,它也阻礙了電子的流動,從而限制了電流并減慢了開關速度。

如果將納米線彼此堆疊起來,就可以獲得更大的Weff,從而獲得更多電流。2004年三星研發出了這種配置的結構,稱為多橋溝道FET。但是它有一些局限性,例如FinFET的鰭堆疊不能太高,否則會干擾互連層。另外,每增加一條納米線就會增加晶體管的電容,從而減慢晶體管的開關速度。最后,由于制造非常窄的納米線特別復雜,其邊緣常常變得非常粗糙,這種表面粗糙度又會阻礙電荷載流子的速度。

2006年,法國CEA-Leti的研發人員想出了一個更好的主意。他們沒有使用一堆納米線來橋接源極和漏極,而是采用了一堆硅薄片。這個想法是在較小的晶體管中增加溝道的寬度,同時保持對泄漏電流的嚴格控制,從而提供性能更好的低功耗器件。IBM Research在此基礎上更進一步,證明由堆疊納米片(stacked nanosheets)構成的晶體管在同樣的面積上可以提供比FinFET更寬的Weff。

此外,納米片的設計又提供了一個額外的好處:它恢復了從Planar FET向FinFET過渡時喪失的靈活性。既可以讓納米片變寬以增加電流,也可以使其變窄以限制功耗。IBM Research將它們堆疊成三層,大小從8-50 nm不等,并于2017年宣布開發出基于這種納米片結構的5nm芯片。

GAA能否取代FinFET的主導地位?

在這種新型晶體管結構的開發過程中,有各種各樣的名稱出現,比如柵極全環繞型(GAA)、多橋溝道、納米束,以及半導體學術研究界通常叫的“納米片”。叫什么名字不重要,重要的是這種設計不僅僅是邏輯芯片的下一個晶體管結構,它可能是摩爾定律終結前的最后一個。

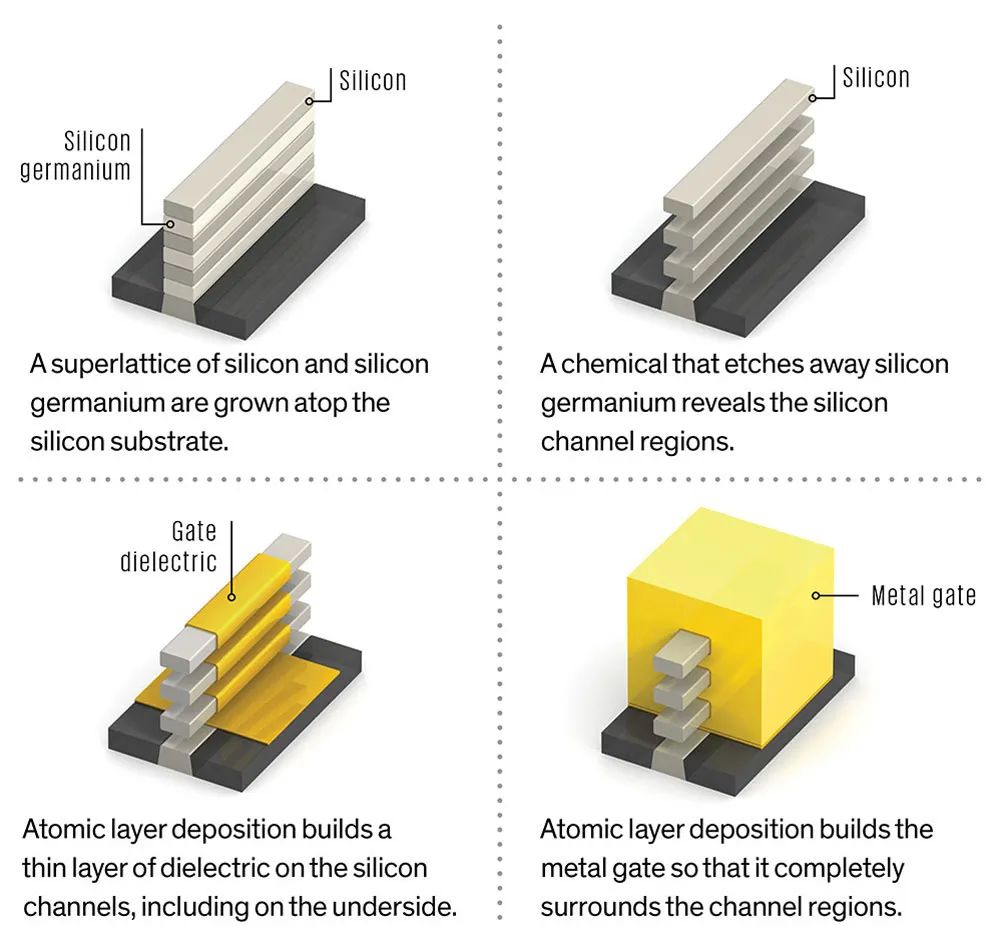

那么,如何制造納米片呢?制造納米片需要補償層、選擇性化學蝕刻劑,以及先進的原子精確沉積技術。

納米片設計結構插圖:Emily Cooper

基于納米片結構的晶體管又如何構建呢?考慮到大多數半導體制造工藝從硅的頂部垂直向下切割或從裸露的表面垂直向上填充,這似乎是一項艱巨的任務。納米片需要去除其他材料層之間的材料,并用金屬和電介質填充間隙。

其中的關鍵是構建所謂的超晶格--一種由兩種材料組成的周期性分層晶體。它可以是硅和硅鍺,研究人員已經制作出了19層的超晶格,但是所涉及的機械應力以及電容讓我們認識到不應該使用這么多的層。在生長了適當數量的層之后,我們使用一種選擇性腐蝕硅鍺但對硅無作用的化學物質,僅留下硅納米片作為源極和漏極之間的懸浮橋。

構建好硅納米片的溝道區域后,就需要填充間隙,首先用電介質,然后用金屬環繞溝道,以形成柵極疊層。這兩個步驟都是通過稱為“原子層沉積”的工藝完成的,這種工藝僅在十年前才引入半導體制造領域。

納米片設計的驚人之處是,它可能延續摩爾定律的有效壽命,甚至超過溝道中硅的使用時間,但是首先要解決散熱問題。每代工藝節點的晶體管密度仍在不斷增加,但芯片可以合理散熱的功率密度近十年來一直保持在每平方厘米100瓦左右。

芯片制造商已竭盡全力避免超過這一上線。為了降低熱量,時鐘速率不得超過4 GHz,于是處理器廠商轉向多核設計,期望幾個較慢的處理器內核可以完成與單個快速處理器內核相同的工作,同時產生的熱量更少。然而,如果想再次提高時鐘速度,我們就需要比硅本身的能效更高的晶體管。

一種潛在的解決方案是將新材料引入溝道區域,例如鍺或由元素周期表的第III列和第V列的元素組成的半導體,例如砷化鎵。電子在其中一些半導體中的移動速度可以快10倍以上,從而使得由這些材料制成的晶體管的開關速度更快。更重要的是,由于電子運動更快,器件可以在較低的電壓下工作,從而提高了能效,并減少了熱量的產生。

受早期關于納米線晶體管和超晶格結構研究的啟發,普渡大學的Peide Ye教授使用砷化銦鎵(III-V半導體)研制出一種三納米片器件,其結果好于預期。這種納米片晶體管對于每微米的溝道寬度允許9,000微安的電流。這是當今最好的平面型InGaAs MOSFET的三倍左右。如果制造工藝得到進一步改善,這種器件的性能仍然可以提高。通過堆疊更多的納米片,我們有可能將性能提高10倍以上。因此,這一設計思路對未來的高速和節能型集成電路的發展有著重要的指導意義。

當然,InGaAs并不是未來納米片晶體管的唯一選擇。研究人員還在探索其他具有高遷移率載流子的半導體,包括鍺、砷化銦和銻化鎵。例如,新加坡國立大學的研究人員最近使用由砷化銦制成的N型晶體管和由銻化鎵制成的P型晶體管的組合,構建了完整的CMOS IC。然而,一種可能更簡單的解決方案是使用摻雜的鍺,因為電子和正電荷載流子(空穴)通過鍺的速度都非常快。

總而言之,無論采用什么化合物材料,堆疊納米片似乎是構造未來晶體管的最佳方法。芯片制造商已經對該技術有足夠的信心,相信在不久的將來會將其納入設計規劃路線圖。隨著高遷移率半導體材料的集成,納米片晶體管將滲透到我們的未來生活,這是任何人現在就可以預見到的。

GAA之爭已經開始

TSMC計劃在2022年第三季度為蘋果公司提供基于3nm FinFET的芯片,而三星計劃在2022年第四季度開始量產其第一代基于3nm GAA晶體管的芯片。在臺積電的規劃路線圖上,這家全球最大的晶圓代工廠商計劃將FinFET擴展到3nm,然后在2023/2024年轉移到2nm GAA。相比之下,三星則直接從5nm FinFET轉移到3nm GAA。

英特爾還在開發可能用于其5nm節點的納米片FET,但目前尚不清楚英特爾的5nm芯片何時發布,但短期內難以縮小與臺積電和三星的工藝差距。至少在未來三年內,三星和臺積電的總支出將超過500億美元,對于任何一家公司來說,要在最先進的邏輯處理技術上趕上這兩家公司都是極其困難的。

但是,美國的英特爾在其新任CEO的領導下,趕上甚至超越還是有可能的。也許,新型的GAA(或者納米片)晶體管是拯救英特爾和摩爾定律的最后一根稻草。

編輯:jq

-

芯片

+關注

關注

455文章

50714瀏覽量

423152 -

CMOS

+關注

關注

58文章

5710瀏覽量

235418 -

晶體管

+關注

關注

77文章

9682瀏覽量

138082 -

納米

+關注

關注

2文章

696瀏覽量

36976

原文標題:干貨 | IBM 2nm芯片采用的GAA技術能否替代FinFET而延續摩爾定律的神話?

文章出處:【微信號:wc_ysj,微信公眾號:旺材芯片】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

擊碎摩爾定律!英偉達和AMD將一年一款新品,均提及HBM和先進封裝

IBM與Rapidus在多閾值電壓GAA晶體管技術的新突破

世芯電子成功流片2nm測試芯片

“自我實現的預言”摩爾定律,如何繼續引領創新

日本Rapidus攜手IBM深化合作,共同進軍2nm芯片封裝技術

Rapidus與IBM深化合作,共推2nm制程后端技術

蘋果將成為首個采用其最新2nm工藝的客戶

摩爾定律的終結:芯片產業的下一個勝者法則是什么?

IBM 2nm芯片采用的GAA技術能否替代FinFET而延續摩爾定律的神話?

IBM 2nm芯片采用的GAA技術能否替代FinFET而延續摩爾定律的神話?

評論