眾所周知,IBM最近發布了2nm芯片,按照他們的說法,這個芯片的密度為3.33億個晶體管/平方毫米(MTx / mm 2);柵極長度為12nm的44nm接觸式多節距(CPP);基于IBM正在使用水平納米片(HNS)的橫截面,Gate All Around(GAA)可以采用多種方法進行GAA;HNS疊層構建在氧化物層之上;與最先進的7nm芯片相比,性能提高45%,功耗降低75%;EUV圖案用于前端,可讓HNS片材寬度在15nm至70nm之間變化。這對于調整電路的各個區域以實現低功耗或高性能以及SRAM單元非常有用;sheet為5nm厚,堆疊為三層高。

但這真的是“ 2nm”嗎?臺積電是目前生產工藝技術的領導者。我們繪制了TSMC節點名稱與晶體管密度的關系圖,并擬合了0.99 R2值的曲線。

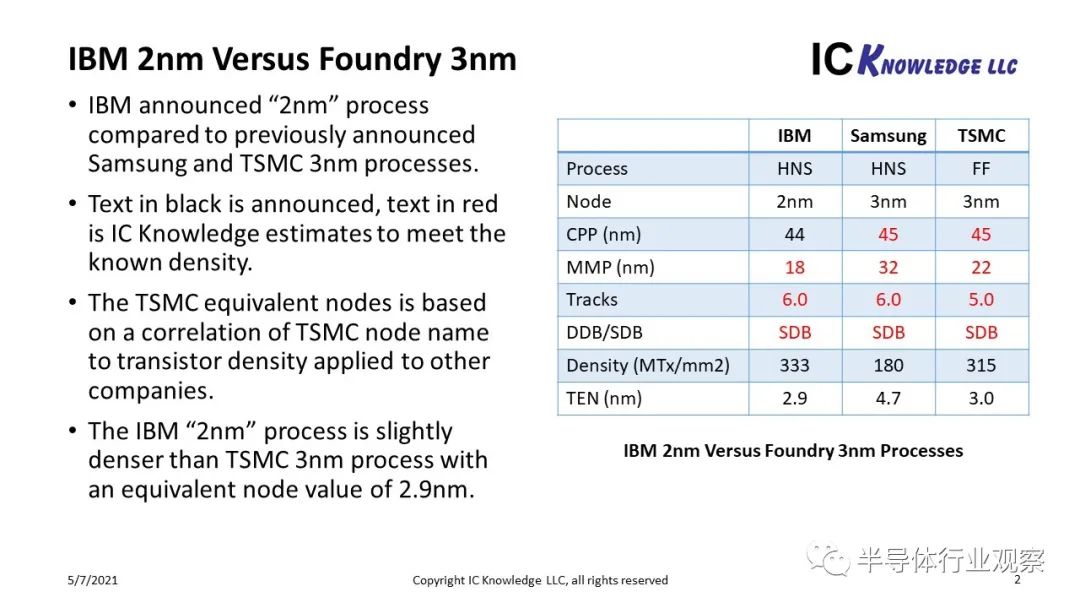

使用曲線擬合,我們可以將晶體管密度轉換為TSMC等效節點(TEN)。使用曲線擬合,對于IBM宣布的333MTx / mm 2,我們得到2.9nm的TEN 。我們認為這使公告成為3nm節點,而不是2nm節點。

為了更詳細地將IBM公告與之前宣布的3nm工藝和預計的2nm工藝進行比較,我們需要進行一些估算。

從公告中我們知道CPP為44nm。我們假設一個單擴散中斷(SDB)將導致最密集的過程。

查看公告中的橫截面,我們看不到埋入式電源導軌(BPR),需要BPR才能將HNS軌道高度降低到5.0,因此我們假設該過程為6.0。

為了達到333MTx / mm 2,最小金屬間距必須為18nm,這是一個非常具有挑戰性的值,可能需要EUV多圖案。

IBM 2nm與晶圓代工廠的3nm

圖2將IBM 2nm設計與我們對三星和臺積電3nm工藝的估計進行了比較。我們知道三星也在制造HNS,而臺積電則選擇了3nm的FinFET。三星和臺積電都宣布將3nm工藝的密度提高,因此我們知道這三家公司的晶體管密度,并且可以計算出這三家公司的TEN。如前所述,IBM的TEN為2.9,我們現在看到三星的TEN為4.7,臺積電的TEN為3.0,再次證明IBM 2nm就像臺積電3nm,而三星則落后于臺積電。

估計圖2中紅色的數字達到了宣布的密度。我們假設所有公司均為SDB。臺積電的 track height最小,因為FinFET可以不帶BPR地達到5.0的 track height,但是HNS需要BPR才能達到5.0,而BPR尚未準備好。

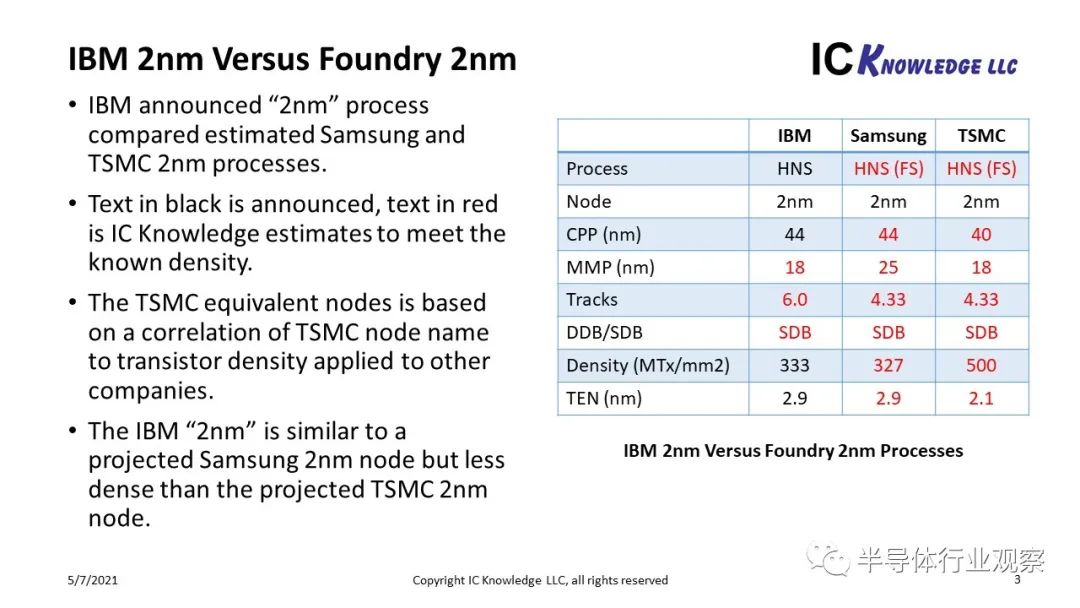

IBM 2nm和晶圓廠的2nm

如圖3,我們還預測了三星和臺積電2nm工藝。我們預計兩家公司都將使用BPR(BPR尚未準備好,但很可能是三星和臺積電在2023/2024左右推出2nm工藝時搞定)。我們還假設三星和臺積電將利用forksheet NHS,HNS(FS)架構能達到4.33的track height ,從而放松了其他一些微縮要求,然后根據該公司最近的微縮趨勢預測了CPP和MMP。

功耗與性能

在今年的ISS上,我通過一些附加的英特爾性能數據,按節點估算了三星和臺積電的相對功耗和性能。逐節點趨勢是基于兩家公司宣布的功率和性能縮放估計與14nm / 16nm的可用比較得出的。

由于IBM將其功耗和性能改進與領先的7nm性能進行了比較,因此我可以將IBM的功率和性能放在我先前介紹的相同趨勢圖上。

IBM對HNS的使用大大降低了功耗,并使2nm制程比三星或臺積電(TSMC)的3nm制程更省電,盡管我們相信,一旦臺積電在2nm上采用HNS,它們在功耗上將與IBM相同或更好。為了提高性能,我們估計臺積電的3nm工藝將勝過IBM 2nm工藝。

正如ISS文章中所討論的那樣,這些趨勢僅是估計值,并基于許多假設,但這是我們可以匯總的最佳預測。

由此可見,在分析了IBM的公告之后,我們認為從密度的角度來看,他們的“ 2nm”工藝更像是TSMC的3nm工藝,雖然功耗更高但性能卻較差。IBM的聲明令人印象深刻,但它是一種研究設備,與臺積電的3nm制程相比,只有明顯的優勢,而臺積電3nm的風險將在今年晚些時候開始,并于明年開始量產。

我們進一步相信,當臺積電工藝在2023/2024左右投產時,它將在2nm的密度,功耗和性能方面處于領導地位。

IBM推出的2nm芯片的重要意義

IBM在新聞稿中表示,新工藝將在指甲大小的芯片上生產約500億個晶體管。它還將帶來比今天的7納米芯片高出75%的效率或快45%的芯片。

從表面上看,IBM似乎在頂級芯片技術的競爭中躍居了遙遙領先的地位。英特爾的最新芯片使用10納米工藝,而臺積電則使用7納米工藝。該公司在這里取得了一些非常出色的成就。但是比較芯片很復雜。因此,值得更多地剖析新聞,以更好地了解大局。

納米到納米是蘋果到橙子

長期以來,計算機芯片的進步一直以納米級的步伐進行衡量。每一步降低都會產生更多的組件(最著名的是晶體管)被封裝到同一區域中。在過去的幾十年中,有一段時間納米命名法確實與某些芯片元件的尺寸匹配。但是那段時間已經過去了。隨著芯片技術的進步,對芯片組件的測量與每一代的命名約定分離。

十多年前,當芯片成為FinFET的最后一次重大飛躍時(形狀像鰭的3D晶體管設計),該行業的節點數量幾乎毫無意義。

它與芯片上的任何尺寸都沒有關系。當前正在爭論哪種新數字或數字組合可以更好地反映進度。并且盡管這也被證明相當復雜,但一位規范專家提出的是每平方毫米的晶體管密度。

要了解舊的命名約定如何造成混淆,請將英特爾的10納米芯片與臺積電的7納米芯片進行比較。兩者實際上具有大致相等的晶體管密度,英特爾的每平方英寸1億個晶體管實際上要比臺積電的每平方毫米9千1百萬個晶體管小。(如下圖有一個方便的表格,用于比較工藝尺寸和芯片的晶體管密度。)

IBM沒有明確宣布其芯片的晶體管密度。但是在伸手弄清楚他們指的是什么尺寸的“指甲”之后(該公司的代表說大約為150平方毫米),該出版物AnandTech計算出IBM的新工藝每平方毫米將產生約3.33億個晶體管。的確,這超出了現在已經生產中的任何芯片。也就是說,臺積電為蘋果生產的3納米芯片每平方毫米可以擁有近3億個晶體管,并有望在明年投入生產。

納米片:摩爾定律的下一步?

也許更重要的消息是晶體管本身的設計。IBM的新技術被稱為納米片或全能門晶體管,是當今FinFET晶體管期待已久的后續產品。自2017年以來,該公司一直在研究這項技術。

FinFET晶體管由一個鰭形溝道組成,該溝道在三側被“門”圍繞,該“門”控制電子的流動。但是,IBM的納米片(或全能門)晶體管具有分層的通道。這些層被堆疊在彼此的頂部上,并且由柵極包圍上所有側面。最后一點是最關鍵的部分。環繞柵晶體管可更好地控制通過溝道的電流,防止泄漏并提高效率。

麻省理工學院專門研究新型晶體管技術的教授Jesúsdel Alamo告訴《連線》雜志:“這是一項令人興奮的技術。” “這是一個全新的設計,可以推動未來的芯片路線圖。” 盡管IBM可能是第一個在此級別上展示該技術的公司,但它們可能不會是最后一個。三星和臺積電可能會效仿。

現在要對現在的生產芯片和使用IBM新晶體管的未來芯片進行認真的性能比較還為時過早,但是可以肯定地說它們將提供顯著的改進。分析公司VLSI Research的首席執行官Dan Hutcheson告訴《連線》,IBM估計的性能改進實際上似乎是保守的,并將這項工作稱為“行業里程碑”。

下一代芯片

您什么時候可以購買帶有這些芯片之一的設備?可能不會。

盡管IBM仍在設計芯片,但它在2014年出售了其芯片制造業務。這項新技術來自其位于紐約州奧爾巴尼市的研究機構,它是一個demo,而不是可用于生產的芯片。在未來的幾年中,IBM將完成該過程,屆時它可能會通過與英特爾和三星等合作伙伴的許可協議進入生產芯片。

該行業在此期間不太可能會停滯不前。目前,芯片行業正在復興。

不再僅僅花費數十億美元從傳統芯片上擰干幾滴。充滿活力和創新的產業煥發了活力,并為特殊目的(如AI)帶來了一系列奇特的設計。其中大部分發生在大公司之外。

多年來,風險資本再次涌入新興芯片公司,實際上,僅在2020年,就有超過120億美元流入了400多家芯片公司。

因此,即使在今年的芯片缺貨嚴重,但季風似乎仍在聚集。

原文標題:IBM發布的真的是2nm芯片嗎?

文章出處:【微信公眾號:電子工程世界】歡迎添加關注!文章轉載請注明出處。

責任編輯:haq

-

芯片

+關注

關注

455文章

50732瀏覽量

423247 -

IBM

+關注

關注

3文章

1755瀏覽量

74679

原文標題:IBM發布的真的是2nm芯片嗎?

文章出處:【微信號:電子工程世界,微信公眾號:電子工程世界】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

IBM最近發布的新品真的是“2nm”嗎?

IBM最近發布的新品真的是“2nm”嗎?

評論