Philps公司生產(chǎn)的型號為PDIUSBD12的接口芯片是一個具有集成的SIE,F(xiàn)IFO存儲器、發(fā)送器和電壓調(diào)整器的高性能USB接口芯片,同時還支持DMA邏輯傳輸形式。他通常應(yīng)用于基于微控制器的系統(tǒng)中,并且可以通過高速的并行接口和系統(tǒng)中的微處理器進(jìn)行通信,其中最高并行接口速率可以達(dá)到2MB/s,是一個具有8位數(shù)據(jù)總線和一個地址的存儲與數(shù)據(jù)交換設(shè)備。

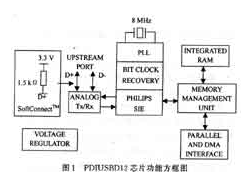

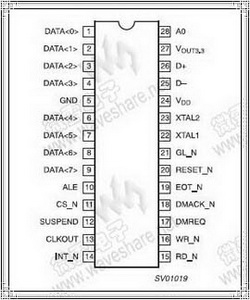

PDIUSBD12芯片的功能方框圖如圖1所示。他采用28PIN腳模式,有S028和TSSOP28封裝,SIE用來實(shí)現(xiàn)USB協(xié)議層的完整功能。具體功能如下:同步方式識別、并/串轉(zhuǎn)換、比特填充/解填充、CRC校驗(yàn)/生成、PID確認(rèn)/生成、地址識別和握手信號的鑒定/生成、批處理數(shù)據(jù)傳輸可達(dá)1 MB/s,3±0.3V雙極性輸入范圍,可接受4.5~5.5V工作電壓、工業(yè)級標(biāo)準(zhǔn)工作環(huán)境溫度范圍為一40~+85℃。也就是說,利用該芯片可以完成微控制器所送出的信號到符號USB規(guī)范的信號的轉(zhuǎn)換。

2 USB工作電路

USB相對于其他傳統(tǒng)接口而言,其快速數(shù)據(jù)傳輸能力和安裝簡單的和諧平衡在掃描儀上體現(xiàn)得尤為突出。傳統(tǒng)的SCSI接口的掃描儀安裝極為麻煩,并且對計算機(jī)的要求非常苛求,必須帶有SCSI接口,并行接口傳輸數(shù)據(jù)又顯得實(shí)在太慢。USB接口可以從速度和安裝的簡易性兩方面滿足用戶的要求。現(xiàn)在的主流掃描儀生產(chǎn)廠家都在生產(chǎn)USB接口掃描儀,如HP,ACER和TARGA等公司都在紛紛推出,這種款式的機(jī)器具有以下的優(yōu)點(diǎn):

(1)USB接口可以有效地提升數(shù)據(jù)的傳輸速度。

(2)無外置電源設(shè)計,采用CIS技術(shù),耗電量只有2W,便攜可靠。

(3)采用了超薄超輕的設(shè)計,外觀悅目。

2.1 硬件電路的設(shè)計

利用PDIUSBD12集成電路來實(shí)現(xiàn)USB接口,可以允許設(shè)計者從市場上的多種微控制器中選擇一種合適的產(chǎn)品來使用。這種靈活性可以通過使用現(xiàn)有的體系結(jié)構(gòu)來降低開發(fā)費(fèi)用,同時還可以縮短開發(fā)周期。

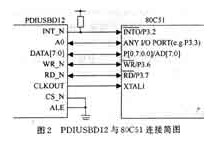

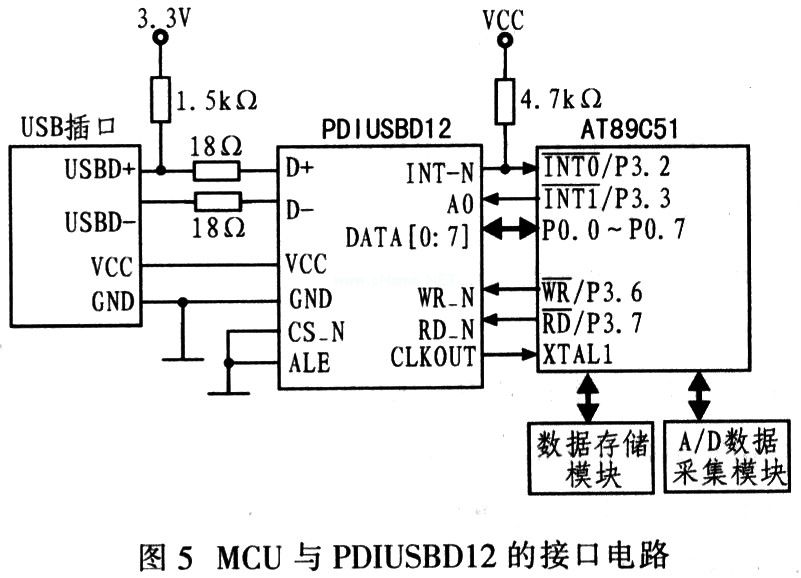

圖2所示是采用了1個80C51的微控制器與PDIUSBDl2集成電路相互連接的簡圖。由于80C51是應(yīng)用比較廣泛的一種單片機(jī)微控制器,,軟件開發(fā)工作者在其基礎(chǔ)上開發(fā)大量的軟件開發(fā)平臺,大多數(shù)電子工程師對其的原因都比較熟悉。因此,用戶可以利用比較熟悉的微處理器(80C51)進(jìn)行核心程序的設(shè)計,即用80C51來實(shí)現(xiàn)其所需的功能,具體將數(shù)據(jù)信號轉(zhuǎn)換為符合USB規(guī)則的信號,則完全由PDIUSBD12來完成。這樣以來,既可以利用80C51中豐富的軟件資源,又可以利用USB總線技術(shù)的即插即用、熱插拔等特性,可以使開發(fā)設(shè)備的成本降低、縮短開發(fā)產(chǎn)品的時間周期。

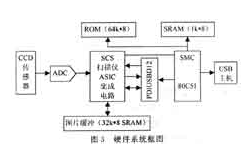

圖3所示是利用PDIUSBD12和1塊80C51微處理器構(gòu)成的硬件系統(tǒng)框圖,他是將一個符合SCSI標(biāo)準(zhǔn)的掃描儀轉(zhuǎn)換變成一個USB總線規(guī)范的設(shè)備,該方案對現(xiàn)有硬件進(jìn)行最小改動的情況下達(dá)到了USB接口技術(shù)的實(shí)現(xiàn)。

2.2 數(shù)據(jù)信號驅(qū)動

USB使用一個差模驅(qū)動器來實(shí)現(xiàn)向USB電纜傳輸U(kuò)SB數(shù)據(jù)信號。在低輸出狀態(tài),驅(qū)動器穩(wěn)態(tài)輸出的變化幅度必須是VOL<0.3V,此時應(yīng)有1.5kΩ負(fù)載加到3.6V電源上;在高輸出狀態(tài),驅(qū)動器穩(wěn)態(tài)輸出的變化幅度必須使Vho>2.8V,此時在地上有15kΩ負(fù)載,差模高輸出狀態(tài)和低輸出狀態(tài)之間輸出的變化幅度必須很好地進(jìn)行平衡,從而將信號偏差減至最小。另外,還需要驅(qū)動器上的擺動速率控制功能把輻射噪音和串話減至最小。驅(qū)動器輸出必須支持三態(tài)操作,以此來進(jìn)行雙向半雙工通信。同時還需高阻抗來將那些正在進(jìn)行熱插入操作或已經(jīng)連接了但電源卻沒有接通的下行設(shè)備同端口隔離開來。相對于沒有損壞的局部參考地而言,驅(qū)動器必須能承受信號管腳上的一o.5~3.8V電壓。

2.3 數(shù)據(jù)信號接收

接受USB數(shù)據(jù)信號時也必須利用1個差模輸入接受器。當(dāng)2個差模數(shù)據(jù)輸入以地電位作為參考,并且處于0.8-2.5V這樣的范圍之間時,接受器具有的靈敏度至少200mV,這稱為共模輸入電壓范圍。當(dāng)差模信號線不在共模范圍之內(nèi)時,也要求能進(jìn)行正確的數(shù)據(jù)接受。如果在沒有損壞并以本地地電位作電位參考的條件下,接收器所能接收的穩(wěn)態(tài)電平輸入電壓應(yīng)該位于一o.5-3.8V之間。另外對于不同的接收器而言,每一條信號線都必須有1個單端接收器,這樣接收器必須具有1個位于0。8~2.0V之間(TTL輸入)這樣的開關(guān)閥值電壓。

3 USB接口工作電路主要參數(shù)

3.1 數(shù)據(jù)編碼/解碼

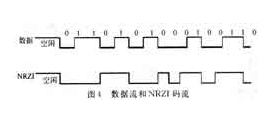

在傳輸信號時,USB應(yīng)用了NRZI編碼方式。在NRZI編碼中,“1”由不出現(xiàn)電平變化來表示,而“0”由電平發(fā)生變化來表示。圖4給出一個數(shù)據(jù)流和等同的NRZI碼流,其中高電平代表數(shù)據(jù)線上的J狀態(tài),而圖示代表了NRZI編碼過程。一串“0”會使得NRZI數(shù)據(jù)每比特周期都會出現(xiàn)跳變,而一串連“1”則使得數(shù)據(jù)中長時間不會出現(xiàn)變化。

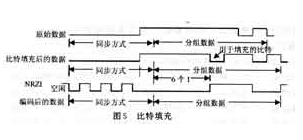

3.2 比特填充

為了保證信號有足夠的變化,在USB上發(fā)送一個分組數(shù)據(jù)時,傳輸設(shè)備要進(jìn)行比特填充。如圖5所示,對于USB上進(jìn)行NRZI編碼之前,在數(shù)據(jù)流內(nèi)每6個連“1”之后都應(yīng)該插入1個“0”,從而在NRZI數(shù)據(jù)流中強(qiáng)制加入1個變化。這樣在邏輯上至少每7個比特周期,接收器就會接收到1個數(shù)據(jù)變化,以保證數(shù)據(jù)和時鐘相互鎖定。接收器必須對NRZI數(shù)據(jù)進(jìn)行解碼,識別填充比特并丟失他們。比特填充sync(同步)模式開始進(jìn)行,并貫穿于整個傳輸過程中。用于終止該sync方式的數(shù)據(jù)“1”,將作為一個序列中的第1個數(shù)據(jù)而加以計數(shù)。比特填充總是被強(qiáng)制執(zhí)行,不會有什么例外。如果比特填充原則需要的話,即使該比特是分組結(jié)束(EOP)信號之前的最后一個比特,也會在最后面插入-個“0”比特。

3.3 數(shù)據(jù)信號速率

全速數(shù)據(jù)速率的標(biāo)稱值是12Mb/s。對于全功能設(shè)備的數(shù)據(jù)速率容差為±0.25%。為了符合幀時間間隔精度的需要,主控制器的精度必須保證其優(yōu)于±0.05%。對于低速率名譽(yù)上為1.5Mb/s,所允許的頻率容差為±1.5%。這一誤差包括下列原因所產(chǎn)生的不準(zhǔn)確性:最初的頻率的正確度、晶體容性負(fù)載、提高給振蕩器的電壓、溫度和老化。低速率的的抖動應(yīng)該小于10ns,這一容差允許在低速率設(shè)備中實(shí)用價格較低振蕩器。

4 結(jié) 論

近幾年來,隨著大量支持USB的個人電腦及Windows的廣泛應(yīng)用,使用USB接口設(shè)備(攜式、手提式電子產(chǎn)品的日益增多)也以驚人的述度發(fā)展。這里詳細(xì)介紹了PDIUSBD12芯片在USB接口電路方面的應(yīng)用。所以,對于廣大的工程師設(shè)計人員來說,USB是設(shè)計外設(shè)接口時的首選總線。

責(zé)任編輯:gt

-

芯片

+關(guān)注

關(guān)注

455文章

50714瀏覽量

423149 -

存儲器

+關(guān)注

關(guān)注

38文章

7484瀏覽量

163763 -

發(fā)送器

+關(guān)注

關(guān)注

1文章

259瀏覽量

26816

發(fā)布評論請先 登錄

相關(guān)推薦

基于PDIUSBD12的USB控制器的設(shè)計

基于PDIUSBD12的USB控制器的設(shè)計

采用PDIUSBD12的USB系統(tǒng)固件程序設(shè)計

采用PDIUSBD12的USB系統(tǒng)固件程序設(shè)計

采用PDIUSBD12的USB系統(tǒng)固件程序設(shè)計

使用 PDIUSBD12的 USB 系統(tǒng)固件程序設(shè)計

接口電路:PDIUSBD12芯片特點(diǎn)及與51單片機(jī)的接口電路圖

采用PDIUSBD12的USB系統(tǒng)固件程序設(shè)計

PDIUSBD12芯片特點(diǎn)及與51單片機(jī)的接口電路圖

采用PDIUSBD12的USB系統(tǒng)固件程序設(shè)計

基于DSP的PDIUSBD12芯片的應(yīng)用開發(fā)

MCU與PDIUSBD12的接口電路

PDIUSBD12芯片的性能特點(diǎn)及實(shí)現(xiàn)應(yīng)用設(shè)計

PDIUSBD12芯片的性能特點(diǎn)及實(shí)現(xiàn)應(yīng)用設(shè)計

評論