作者:曹艷,蔡竟業,楊亦師,范元濱,楊遠望

1 引 言

線性調頻連續波(LFMCM)雷達具有不存在距離盲區、時帶積大、發射功率低、截獲率小、接收靈敏度高等優點,因而在汽車防撞、毫米波成像、探測埋地物件(地雷、管道等)、導彈末制導等領域發揮著越來越重要的作用。傳統的LFMCM主要采用壓控振蕩器來實現,這種方法不能保證信號的高線性度。因此,現今愈來愈多地采用基于DDS的產生方法,其主要優勢在于工作模式多、頻率轉換(掃頻)時間快、頻率分辨率高、輸出相位可調。其劣勢在于雜散較大,輸出頻率范圍較低(一般小于系統時鐘的1/3)。另一方面,受DDS輸出頻率范圍的限制,往往需要對DDS的掃頻輸出頻帶進行擴展,擴展方法主要有直接倍頻、多次上變頻、DDS+PLL混合。

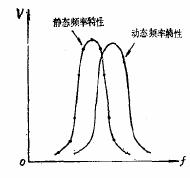

LFMCW信號的線性度特性對雷達的檢測和測距性能具有直接影響,所以,如何提高掃頻線性度是LFMCW雷達的一個重要課題。目前,一般掃頻源(VCO)線性度為5%左右,改善掃頻信號源的方法可分為開環補償和閉環補償。這兩種方法一般可將線性度做到千分之幾,現在被廣泛使用的延時鎖相法屬于閉環補償方案,其線性度可達到十萬分之幾。但對于要求比較嚴格的應用領域(如導彈末制導等),這樣的線性度還不能滿足要求。因此,要獲得更高的線性度,DDS是首選,在一定條件下,它的線性度可達10-6。本文主要討論了以ADI公司推出的AD985x和AD995x為代表的DDS的線性掃頻特性。

2 掃頻非線性度分析

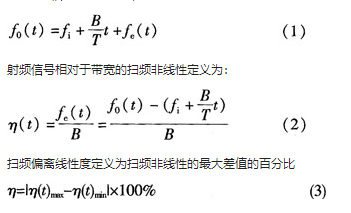

LFMCW信號的射頻輸出可描述為一個理想線性掃頻加上一個非線性頻率誤差,即

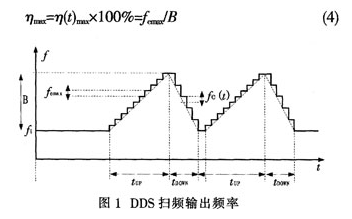

由圖1可見,對于DDS掃頻而言,i為掃頻初始頻率,B為掃頻帶寬,t為掃頻時間,當向上掃頻時t為tUP;當向下掃頻時t為tDOWN。e(t)為非線性掃頻誤差,emax為最大非線性掃頻誤差。由圖1不難發現:DDS掃頻具有很強的規律性。DDS掃頻實際上是DAC在起始頻率和終止頻率之間等間隔地輸出頻率,即輸出頻率等階躍保持。ADI公司的DDS有兩個掃頻性能控制參數,一是頻率步進,二是駐留時間(向上掃頻和向下掃頻可以有不同的頻率步進和駐留時間)。對于DDS掃頻而言,最小的非線性掃頻誤差 emin為零,最大的非線性掃頻誤差?emax為頻率步進,不難明白,這里掃頻偏離線性度和最大掃頻非線性度是一致的,均為頻率步進與掃頻帶寬的比值。

可見,DDS掃頻非線性度與頻率步進成正比。而且,掃頻步進和駐留時間具有相互制約關系。當掃頻帶寬和掃頻周期一定時,掃頻步進越小.說明在掃頻周期內掃完整個掃頻帶寬范圍所需要的步子越多,需要的駐留時間越小。需要說明的是,掃頻步進和駐留時間都受器件本身性能的制約,存在一個最小值。當掃頻周期比較長時,掃頻步進受器件本身掃頻步進最小值的限制,駐留時間大于或等于器件本身最小駐留時間,即DDS掃頻非線性度受器件本身掃頻步進最小值的限制:當掃頻周期比較短時,掃頻步進受器件本身駐留時間最小值的限制,掃頻步進大于或等于器件本身最小掃頻步進,即DDS掃頻非線性度受器件本身駐留時間最小值的限制。在一般的對掃頻周期沒有嚴格要求應用領域,應該盡量使掃頻步進達到DDS器件本身的掃頻步進最小值,從而使掃頻非線性度最低(掃頻駐留時間隨掃頻周期變化)。在導彈末制導等應用領域,由于掃頻周期極短(μs量級),而目前DDS的掃頻駐留時間只能在ns量級,所以掃頻線性度受掃頻駐留時間的限制,不能達到DDS器件本身的掃頻步進最小值,往往只能達到一個相對掃頻步進最小值(在掃頻駐留時間取最小值時得到)。

3 掃頻參數計算

ADI公司推出的掃頻DDS參數由式(5)決定

△=[DFTW/2N]×SYS_CLK (5)

其中,△為掃頻步進,DFTW為掃頻步進控制字,N為頻率步進控制字的位數(見表1),SYS_CLK為DDS的系統時鐘;而掃頻駐留時間△t為

△t=DSRR[1/SYNC_CLK] (6)

其中,DSRR為掃頻駐留時間控制字,SYNC_CLK為同步時鐘。因此,可以得出

F=s+T×[△/△t] (7)

其中,F和s分別為掃頻終止頻率和掃頻起始頻率,T為掃頻時間。

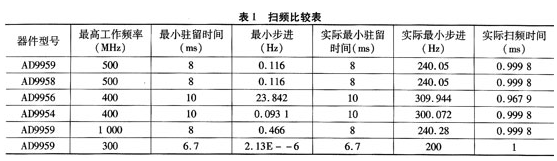

由式(5)可知,掃頻步進與掃頻步進控制字位數成反比。隨著DDS技術的發展,DDS掃頻步進越來越小,甚至可以達到1 Hz以下,對于幾十兆赫茲的應用來說,如果不考慮器件本身掃頻駐留時間的限制,那么DDS掃頻非線性度可以達到10-6量級。但是在導彈末制導等應用領域,由于受器件本身掃頻駐留時間的限制。掃頻步進達不到器件本身掃頻步進的最小值,因而DDS掃頻非線性度的量級銳減,當實際掃頻步進為幾百赫茲時,DDS掃頻非線性度只有10-4量級。例 如,在導彈末制導應用等領域,1 ms周期以內掃頻30 MHz帶寬。由式(5)~(7)可以計算出ADI多款掃頻DDS的參數,如表l所示。假設DDS器件都工作在各自最高工作頻率,掃頻30 MHz帶寬,掃頻時間1 ms。

由表1可以看出,在掃頻帶寬和掃頻時間確定的情況下。各DDS對應的最小掃頻駐留時間和最小掃頻步進是不同的。在導彈末制導等掃頻駐留時間制約掃頻非線性度的應用領域,同一款DDS器件,實際掃頻步進和最小掃頻步進也是不同的,且實際掃頻步進往往大于最小掃頻步進。因而在應用中應根據實際情況選擇不同的DDS器件。例如,AD9954最小掃頻步進雖小于AD9958,但在1 ms周期內掃頻30 MHz帶寬時,實際掃頻步進卻大于AD9958,因為AD9954的最小駐留時間大于AD9958。又如,AD9956的最小掃頻步進雖然遠大于AD9954。但在1 ms周期內掃頻30 MHz帶寬時,實際掃頻步進卻與AD9954相當,這是因為AD9956和AD9954的最小駐留時間相同。由此可以看出,在實際應用中,可以通過計算比較,確定最合適的DDS器件。

在一般的對掃頻周期沒有嚴格要求的應用領域,掃頻非線性度受掃頻步進限制,首選AD9959、AD9958、AD9954、AD9854、AD9852。在導彈末制導等應用領域,掃頻非線性度受掃頻駐留時間限制,首選AD9959、AD9958、AD9858、AD9854、AD9852。

另外,雖然從表1中看出AD9854和AD9852的最小掃頻駐留時間最短,性能最好,但這兩款DDS器件的功耗相對其他幾款器件而言大一個數量級,所以在對功耗有嚴格要求的應用場合最好選用AD995x系列器件。

4 掃頻模式比較

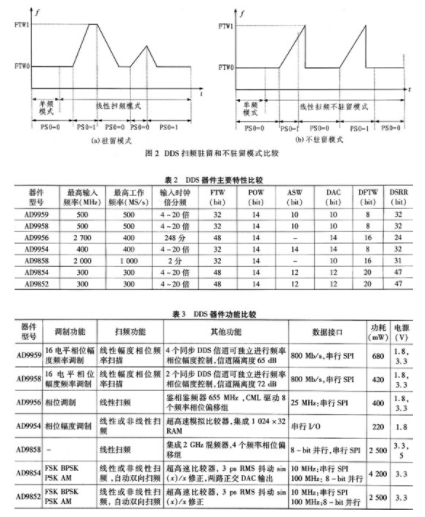

ADI公司的DDS器件通常具有兩種線性掃頻模式,駐留模式和不駐留模式。它們的主要區別在于:

(1) 在線性掃頻模式下,頻率累加器使輸出頻率從一個可編程低頻梯變為一個可編程高頻,或者從一個可編程高頻梯變到可編程低頻。低頻存儲在profile 0,高頻存儲在profile 1。頻率累加器的內部組合邏輯要求FTW0的值必須總小于FTWl的值。掃頻方向由PS0引腳控制。PS0引腳由低跳變至高時,頻率從低掃至高;PS0引腳由高跳變至低時,頻率從高掃至低。實現掃頻功能.頻率累加器需要4個控制字:①上升掃頻步進控制字(RDFTW),表示當頻率從低掃到高時,頻率每上升一步,頻率累加器需要增加多少頻率,即上升步進;②上升掃頻駐留時間控制字(RSRR),表示當頻率從低掃到高時,頻率累加器頻率增加的速度,即多長時間累加器增加一個步進。RSRR說明了在兩個步子之間,頻率累加器需要數多少個SYNC_CLK周期;③下降掃頻步進控制字(FDFTW);④下降掃頻駐留時間控制字(FSRR)。在線性掃頻模式下,組合邏輯確保器件輸出頻率不會超過FTW1,即使下一個RDFTW增加會使頻率超過FTWl。一旦頻率達到FTW1.只要PS0引腳為高,頻率輸出將始終是FTW1。同樣。內部邏輯確保下降掃頻時頻率不會低于:FTW0,即使下一個FDFTW增加會使頻率超過FTW0。如果在掃頻進行當中PS0引腳狀態改變,器件將按照新的步進頻率控制字和掃頻速度字按新的方向進行掃頻。

(2) 在線性掃頻不駐留模式,頻率累加器使輸出頻率從一個可編程低頻梯變到一個可編程高頻。當到達高頻時,累加器直接跳回低頻,而不是梯變回低頻。在線性掃頻不駐留模式,只用到上升掃頻步進控制字(RDFTW)和上升掃頻駐留時間控制字(RSRR)。在線性掃頻不駐留模式,掃頻依然由PS0引腳控制,一旦PS0引腳由低跳變至高,不管在掃頻過程中PS0引腳是否跳回低,器件都會完成整個掃頻。掃頻結束后,PS0引腳的又一個上升沿觸發下一次掃頻。這就意味著,在啟動另一個掃頻前,PS0引腳需要預先被拉低。

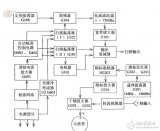

由以上對比和圖2可以看出兩種線性掃頻模式的三大主要區別:第一,線性掃頻模式有兩個掃頻方向(由低掃到高或者由高掃到低),而線性掃頻不駐留模式只能從低掃到高;第二,掃頻過程中,PS0引腳狀態(僅從0變為1或僅從1變為0)的改變,會立刻影響線性掃頻駐留模式的掃頻方向,而它對線性掃頻不駐留模式卻無影響;第三,掃頻結束后,如果PS0引腳狀態不改變(無論是1或0),線性掃頻模式的輸出會保持在掃頻過程的最后一個頻率點(FTW0或FTW1,視掃頻方向而定),而對于線性掃頻不駐留模式而言,掃頻結束后輸出會立刻跳變回FTW0。

本文所討論的幾款器件都具有駐留模式,部分器件具有不駐留模式,它們是AD9959、AD9958、AD9956、AD9954。在不同的應用場合,可以根據需要,簡單地通過對寄存器值的修改選用不同的掃頻模式。在選擇DDS器件時,應該根據實際需要的掃頻模式來選擇合適的DDS器件。

5 性能比較

ADI公司推出了很多性能優良、功能強大的DDS器件,現在最常用的是AD985x系列和AD995x系列,這兩個系列最主要的區別在于功耗,AD985x系列DDS器件功耗為瓦級,而AD995x系列DDS器件在功耗上作了很大改進,達到百毫瓦級。它們除了具有主要的DDS功能外,還額外集成了其他功能塊,如鎖相環、混頻器、比較器、多輸出通道等。下面對ADI公司多款DDS器件的主要性能和特點進行介紹和比較(參見表2、表3)。

AD9959有四路同步DDS信道,可獨立進行頻率相位幅度控制,信道隔離度大于65 dB,具有線性頻率相位幅度掃描能力,16電平頻率相位幅度調制能力,4個可編程滿量程電流獨立DAC;AD9958有兩路同步DDS信道,可獨立進行頻率相位幅度控制,信道隔離度大于72 dB,具有線性頻率相位幅度掃描能力,16電平頻率相位幅度調制能力,2個可編程滿量程電流獨立DAC:AD9956具有200 MHz鑒相鑒頻器,鑒相鑒頻器前端有655 MHz可編程分頻器(1~16整數),具有相位調制能力,8個相位頻率組。AD9954具有可編程

相位幅度抖動,超高速模擬比較器.自動線性非線性掃頻能力,l 024×32靜態RAM,具有相位調制能力,4個相位頻率組;AD9858內部時鐘1 GS/s。輸入頻率可達2 GHz,集成2 GHz混頻器,8-bit并行或串行接口,4個相位頻率組:AD9854可進行FSK、BPSK、PSK、CHIRP、AM調制,具有超高速比較器,線性或非線性掃頻,自動雙向掃頻,8-bit并行或串行接口,sinx/x修正;AD9852和AD9854絕大部分功能一樣,區別在于AD9852有一路是正常DAC輸出,另一路是控制DAC輸出,它可以輸出直流控制電平,交流信號,而AD9854只有一路是正常DAC輸出。另一路是控制DAC輸出(同AD9852)或正交DAC輸出,即兩路輸出信號總是頻率相同、相位呈90°、幅度可調。

從表2、表3的比較看出,當輸入信號頻率比較高時,首選對輸入信號具有分頻功能的DDS器件,如AD9956或AD9858。當輸入信號頻率比較低時,首選對輸人信號具有倍頻功能的DDS器件。如AD9959、AD9958、AD9954、AD9854、AD9852。當器件外部與內部數據傳輸速度要求比較高時,首選具有高速串行SPI或并行數據接口的DDS器件.如AD9959、AD9958、AD9854、AD9852。當對DDS器件功耗有要求時,首選AD995X系列DDS器件,如AD9954、AD9959、AD9958、AD9956。當需要多信道頻率輸出時,首選AD9959、AD9958、AD9854。當需要比較器時,首選AD9954、AD9854、AD9852。當需要鑒相鑒頻器構成鎖相環時,首選AD9956。當需要混頻器時,首選AD9858。當對調制、掃頻有要求時,根據要求的不同選用不同的DDS器件。

6 結束語

本文針對線性調頻連續波雷達信號的要求。對ADI公司推出的AD985x和AD995x為代表的DDS器件的相關性能特點進行了比較、分析。在工程實踐中,應當根據掃頻源設計方案和設計要求整體考慮選擇合適的DDS器件。一方面,應該考慮掃頻源的實際應用情況,看它對掃頻周期有無嚴格要求。如果有嚴格要求,則可以根據最小掃頻駐留時間來選擇,反之,則可以根據最小掃頻步進來選擇。另一方面,應該考慮系統是否對DDS器件功耗有嚴格要求。如果有嚴格要求,則可以選擇AD995系列。此外,還應該考慮是否需要其他集成功能(如混頻器、比較器、鑒相鑒頻器、DDS信道數等)。

責任編輯:gt

-

寄存器

+關注

關注

31文章

5421瀏覽量

123368 -

比較器

+關注

關注

14文章

1840瀏覽量

108541 -

DDS

+關注

關注

22文章

671瀏覽量

154044

發布評論請先 登錄

“雷達和掃描系統的FM線性掃頻源”

請問AD9106可以實現掃頻嗎?不能的話有實現掃頻功能的DDS芯片嗎?

DDS信號源如何應用于掃頻測試技術?

基于DDS的快速跳頻源設計

DDS的線性掃頻特性解析

掃頻儀是什么(由什么組成)_掃頻儀的工作原理_掃頻儀的功能及作用

評論