1 概述

隨著微電子技術的快速發展,可編程芯片的處理能力也在不斷加強,尤其是DSP芯片正在朝著高速,多指令并行執行的方向發展。DSP處理能力的增強,使得原來運算量很大的算法可以用軟件的方式快速實現。由于軟件處理的靈活性,這給整體的無線電體系結構帶來了深刻的變化。

軟件無線電是指一種基于可編程的,具有一定靈活性的高速信號處理平臺。處理平臺上的設備都可以進行重新配置,將通用化、模塊化、標準化的算法單元用軟件方式實現,根據系統的實際需要,在軟件中添加各種不同算法,可以完成特定的功能,因而可以跨越多種通信標準。當需要從一種標準切換至另一種標準時,處理器能夠動態的在軟件的主要部分切換[1“5]。

2 系統結構設計

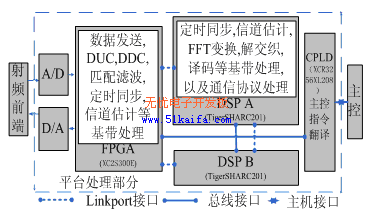

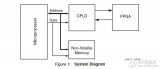

本平臺主要針對寬帶無線數字通信系統物理層的中頻和基帶單元的數字信號處理,如圖1所示,平臺上有兩個DSP(ADI,TigerSHARC201),一個FPGA(Xilinx XC2S300E)和一個CPLD(Xilinx XCR3256XL208)。依據信號處理各模塊的運算特點,以及器件特點,我們將不同的模塊選擇在不同的器件中完成。FPGA設置靈活,但是主頻很難做高,通常低于120MHz,適合于處理可并行計算的模塊;而DSP主頻很高,主要以串行方式執行指令,且DSP支持C語言,所以便于處理通信協議。基于以上特點,FPGA適合處理發送端數據以及數字上變頻(DUC);在接收端適合處理數字下變頻(DDC),匹配濾波器,定時同步等其它基帶處理模塊。DSP適合定時同步,信道估計,FFT變換,解交織,譯碼等其它基帶處理模塊,以及通信協議處理。而CPLD由于其器件特性限制,一般用作主控模塊或主控指令翻譯器。

現代寬帶無線數字通信系統要盡量使用數字信號處理方法來增加可靠性,因此要使用寬帶A/D和D/A,但是由于器件性能局限,我們一般情況下選擇在中頻處使用A/D,D/A。本平臺A/D使用12bit的AD9235,最高采樣率為65MSPS,如果中頻低于65MHz,我們可直接對中頻信號進行采樣,如果中頻頻率較高,可以采用帶通采樣的方法。D/A使用14bi的AD9857,200MSPS,實現中頻輸出。

圖1:平臺結構圖

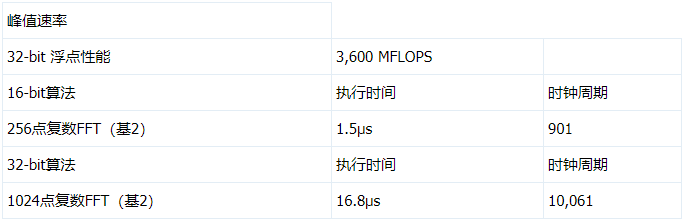

寬帶無線數字通信系統的一般基帶處理算法中主要分為碼片級處理和符號級處理,同時還有通信協議處理。碼片級信號處理的特點是運算量大,比如定時同步等,所以在以往的系統中大多采用FPGA或ASIC來實現,但是本平臺上的高性能DSP中設置了一些特殊單元,完全可以滿足碼片級處理的要求,表1為DSP處理能力的峰值指標,從此表中我們可以看到其強大的處理能力。符號級處理比如譯碼等,相對來說處理量不是很大,此DSP還提供了增強的指令,使得Viterbi和Turbo碼解碼更快。通信協議處理部分需要很多判斷,跳轉等操作,這部分如果使用FPGA或ASIC處理將使系統開發變得非常慢,而DSP可采用C語言,這點無疑非常適合于通信協議的處理。

表1:DSP處理能力指標

注:此表中是DSP工作在600MHz時的數據

FPGA作為DSP的硬件協處理器能夠增強功能,改善吞吐量,減小系統成本。本平臺上的FPGA較小,只有100萬邏輯門,在此平臺上主要作為DSP的協處理器。CPLD為主要用于完成主控指令的轉換。

2.1 DSP體系結構簡介

平臺上使用的高性能DSP TigerSHARC201主頻600MHz,其主要特點是能夠進行多指令并行執行,芯片內部集成了一些專用處理模塊,用以保證一些較為復雜的運算指令也能在一時鐘周期處理完畢。

TigerSHARC201內部主要模塊:(1)兩個運算模塊,可以并行執行計算,且每個運算模塊每周期能完成2條運算指令,大大增強了數字信號處理能力,支持定點和浮點運算;(2)兩個整數ALU,能提供強大的地址產生能力和通用的整數操作;(3)六塊片內DRAM共24M bit,每塊4Mbit,用于存儲指令和數據,這種分塊DRAM結構使得DSP可以在取指的同時訪問數據;(4)三條相互獨立的128bit寬片內數據總線,使得指令行能包括4個32bit指令,且提供了許多并行操作以簡化編程。例如,一條指令行可以讓DSP有條件的在兩個運算模塊中分別執行乘,加和減操作,且可以同時跳轉到程序的其它地方。每條片內數據總線都與六個片內DRAM相連,用以保證片內指令和數據的并行高效傳輸[6]。

TigerSHARC201外部接口:(1)一個總線接口,數據線可配置為64bit或32bit,地址線32bit;(2)四個Linkport接口,采用LVDS技術,每個接口能提供額外的全復用4bit接收和發送能力,其最大傳輸速率500Mbytes/s,用于處理器間的點對點高速數據傳輸,為數據傳輸提供了又一種途徑,Linkport接口也是本平臺的最大特點之一[6]。

2.2 數據調度方法

數據調度的原則是:盡量減少芯片間的數據傳輸量。因為芯片間的數據傳輸要走PCB板的數據線,其數據傳輸速率相對較低,而且過于頻繁的板級數據傳輸容易造成系統調度沖突,不便于處理。但是此DSP支持一個特殊的數據傳輸接口——Linkport接口,可以在很大程度上緩解此問題。

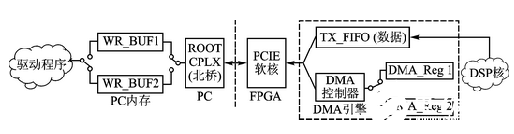

使用DSP的Linkport接口分別實現DSP與DSP,DSP與FPGA之間的點對點高速數據傳輸,這樣可滿足數據調度原則,使得系統總體調度變得較為簡單。總線接口只要負責控制指令和小量數據的傳輸就可以了。如果兩個DSP要對同一批數據分別進行處理,那么這時候就要走總線接口,使用廣播的方式進行數據傳遞,即兩個DSP可以同時接收數據,以減少數據調度。平臺上有兩個DSP,根據系統運算量需求來確定使用一個或者兩個都用。DSP間可以形成了一個處理鏈,也可以配置成兩個DSP并行處理。

為了使得平臺便于調度,所以可在平臺上將FPGA或者一個DSP設置為從屬器件。在FPGA中設置控制寄存器和狀態寄存器,在從屬DSP中設置控制變量和狀態變量,DSP通過總線接口來讀寫這些寄存器或者變量以達到控制從屬器件的目的,這樣做相當于硬件平臺上只有一個“大腦”,有利于減小硬件平臺調度沖突。同時FPGA還要通過總線接口接受CPLD(即主控)的控制。

2.3 控制信息處理機制

控制信息處理機制是指DSP作為硬件平臺的核心,如何控制其它從屬器件。一般主要有兩種方法:查詢模式和中斷模式。查詢模式是指從屬器件在特定時刻(一般為某個模塊處理完畢后)會主動讀取DSP發送來的并已事先存儲在緩存中的指令,隨后執行。中斷模式是指DSP發送的指令以中斷的形式強制從屬器件立即執行,從而控制整個硬件平臺。

CPLD主要用來作為主控或者翻譯主控發來的指令,然后將控制信息傳遞給DSP和FPGA。這里CPLD可以直接通過總線接口控制FPGA,也可以通過DSP間接控制FPGA。

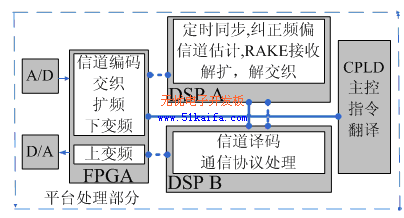

3 應用于直接序列擴頻系統

首先將各接收模塊信號運算的特點以及FPGA和DSP的特性相結合,找出比較適合于執行此模塊的器件,然后進行運算量估計,根據運算量估計結果考慮使用DSP的數量以及芯片間的數據調度方式。本平臺采用了如圖2所示的處理流程,發送端全部在FPGA內部處理。接收端下變頻在FPGA內處理,其它模塊全部由DSP處理,兩個DSP形成一個處理鏈關系,

圖2:直擴系統處理流程圖

數據先進入DSP A,然后由Linkport接口傳給DSP B,譯碼完畢后由DSP B經過總線接口傳遞給CPLD,通信協議全部在DSP B內部處理。DSPB作為整個平臺的處理核心,DSP A和FPGA均為其從屬器件。

3.1 發送端

因為發送端數據處理量較小,占用系統資源相比于接收處理基本可以忽略。依據圖1所示處理平臺結構,將原始數據直接發送給FPGA進行調制和上變頻等處理即可[7]。

3.2 接收端

FPGA主要負責數字下變頻,因為這部分的運算特點是處理量大,但是不需要繁瑣的調度。利用本地數控振蕩器(NCO)產生與輸入中頻信號頻率相同的正弦和余弦信號,并與輸入信號相乘,然后對運算結果做低通濾波,即可完成對中頻信號的下變頻操作。具體的參數由主控通過CPLD發送指令到FPGA中的控制寄存器來設定。FPGA中的寄存器又分為兩部分,一部分受CPLD控制,這樣主機可以通過CPLD發送命令來控制A/D的采樣率以及選擇數字濾波器的參數等,以適應不同的通信標準;另一部分受DSP控制,執行數據調度操作。

DSP主要完成整個基帶數字信號處理,包括定時同步、糾正頻偏、信道估計、RAKE接收、數據檢測、解擴、解交織、維特比譯碼等模塊。定時同步部分的特點時運算量比較大,且需要一些跳轉等控制。因為此DSP有非常強大的FFT運算能力,所以我們采用基于FFT快速相關的方法進行同步。DSP內部代碼采用C語言與匯編語言匯合編程的方式,利用兩種語言各自的優勢進行互補。

C語言開發速度很快,可讀性很強,而且方便軟件的修改和移植,但是效率較低。匯編語言的效率很高,但是修改和移植能力較差,而且不便于調度。基于這個特點,我們將程序全部模塊化,標準的算法模塊用匯編語言編寫,如FFT模塊等,整體的程序框架采用C語言,所以定時同步模塊采用DSP。另外,TigerSHARC201 DSP還支持一些專門用于直擴系統的指令,如解擴指令,Viterbi和Turbo譯碼專用指令等,所以將基帶處理部分放在DSP內處理較為合理。

這樣處理的另外一個優勢是使得系統兼容性更強,在此系統中采用了不同的序列擴頻比來抵抗信道衰落造成的影響,大范圍變化的擴頻比會使系統整體調度發生很大變化。比如當擴頻比為16時,所需的RAM較少,這樣片內的DRAM就已經夠用;而當擴頻比為10240時,就必須要使用片外RAM,這樣就要用到總線接口,此時兩種系統的基帶處理模式完全發生了變化,從而導致系統整體調度發生變化。用C語言處理時,可以設定幾個不同的工作模式,在處理循環開始的時候進行切換即可。如果采用了不同的通信標準的話,處理就更為繁瑣一些。

平臺控制信息和狀態信息處理機制都采用查詢模式,即在執行完一次循環后,DSP都會主動去讀取主控發來的控制指令,隨后讀取FPGA的狀態信息,最后根據情況調整工作模式。

4. 結束語

本文作者創新點是提出一種使用新的高速串行接口設計通用軟件無線電平臺的方法。平臺以高性能DSP為數據處理核心,采用了一種新的高速串行接口進行平臺數據調度。實踐證明,這種方法可以避免一些不必要的調度開銷和沖突,簡化了系統設計,縮短了開發周期。然后將其應用于直接序列擴頻系統,用實際系統設計說明了這種方法的優勢所在。

責任編輯:gt

-

dsp

+關注

關注

553文章

7987瀏覽量

348745 -

FPGA

+關注

關注

1629文章

21729瀏覽量

602990 -

cpld

+關注

關注

32文章

1248瀏覽量

169334

發布評論請先 登錄

相關推薦

如何利用FPGA設計軟件無線電平臺?

怎么實現一款基于FPGA的軟件無線電平臺設計

基于FPGA的通用軟件無線電平臺設計

基于Xilinx Virtex6 FPGA的通用軟件無線電平臺設計

基于TigerSHARC201和FPGA實現軟件無線電平臺的設計

基于TigerSHARC201和FPGA實現軟件無線電平臺的設計

評論