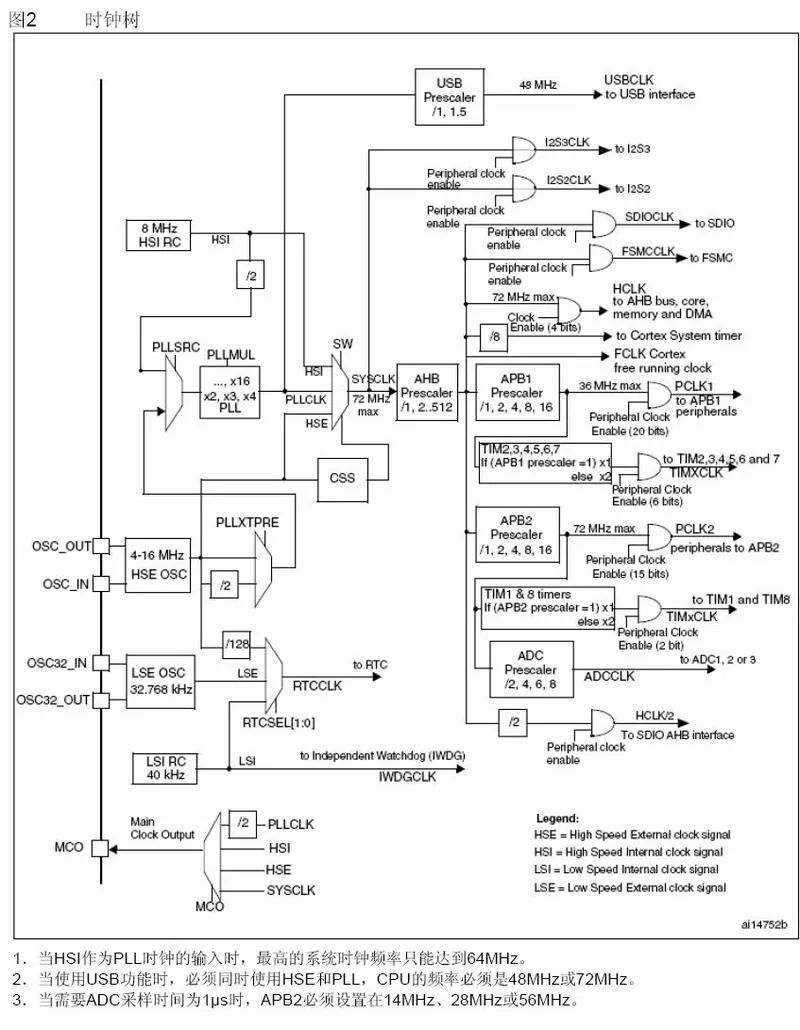

時鐘信號好比是單片機的脈搏,了解STM32時鐘系統(tǒng)很有必要。下圖是STM32F1xx用戶手冊中的時鐘系統(tǒng)結(jié)構(gòu)圖。

在STM32F1xx中,有五個時鐘源,分別為HSI、HSE、LSI、LSE、PLL。

HSI是高速內(nèi)部時鐘,RC振蕩器,頻率為8MHz

HSE是高速外部時鐘,可接石英/陶瓷諧振器或者接外部時鐘源,頻率范圍為4MHz~16MHz

LSI是低速內(nèi)部時鐘,RC振蕩器,頻率為40kHz

LSE是低速外部時鐘,接頻率為32.768kHz的石英晶振

PLL為鎖相環(huán)倍頻輸出,其輸出頻率最大不得超過72MHz

SYSCLK系統(tǒng)時鐘SYSCLK最大頻率為72MHz,它是供STM32中絕大部分部件工作的時鐘源。系統(tǒng)時鐘可由PLL、HSI或者HSE提供輸出,并且它通過AHB分頻器分頻后送給各模塊使用。HCLKHCLK為高性能總線AHB(advanced high-performance bus)提供時鐘信號。由系統(tǒng)時鐘SYSCLK分頻得到,一般不分頻時等于系統(tǒng)時鐘,是給外設(shè)使用的。

FCLK

FCLK(free running clock)是自由運行時鐘,為CPU內(nèi)核提供時鐘信號。我們所說的CPU主頻為xxHz,指的就是這個時鐘信號頻率,CPU時鐘周期就是1/FCLK。“自由”表現(xiàn)在它不來自系統(tǒng)時鐘HCLK,在系統(tǒng)時鐘停止時FCLK也繼續(xù)運行。FCLK用作采樣中斷或者為調(diào)試模塊計時。在處理器休眠時,通過FCLK可以采樣到中斷和跟蹤休眠事件。Cortex-M3內(nèi)核的FCLK和HCLK互相同步、互相平衡,保證Cortex-M3的延遲相同。

原文標(biāo)題:STM32時鐘系統(tǒng)中的SysTick、FCLK、SYSCLK、PCLK和HCLK

文章出處:【微信公眾號:MCU開發(fā)加油站】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

責(zé)任編輯:haq

-

STM32

+關(guān)注

關(guān)注

2276文章

10947瀏覽量

359167 -

時鐘

+關(guān)注

關(guān)注

11文章

1758瀏覽量

132183

原文標(biāo)題:STM32時鐘系統(tǒng)中的SysTick、FCLK、SYSCLK、PCLK和HCLK

文章出處:【微信號:mcugeek,微信公眾號:MCU開發(fā)加油站】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

一文看懂!時鐘在數(shù)據(jù)采集系統(tǒng)中究竟起到哪些關(guān)鍵作用?

STM32F103×8/STM32F103×B MCU手冊

本源產(chǎn)品丨高穩(wěn)低相噪時鐘源

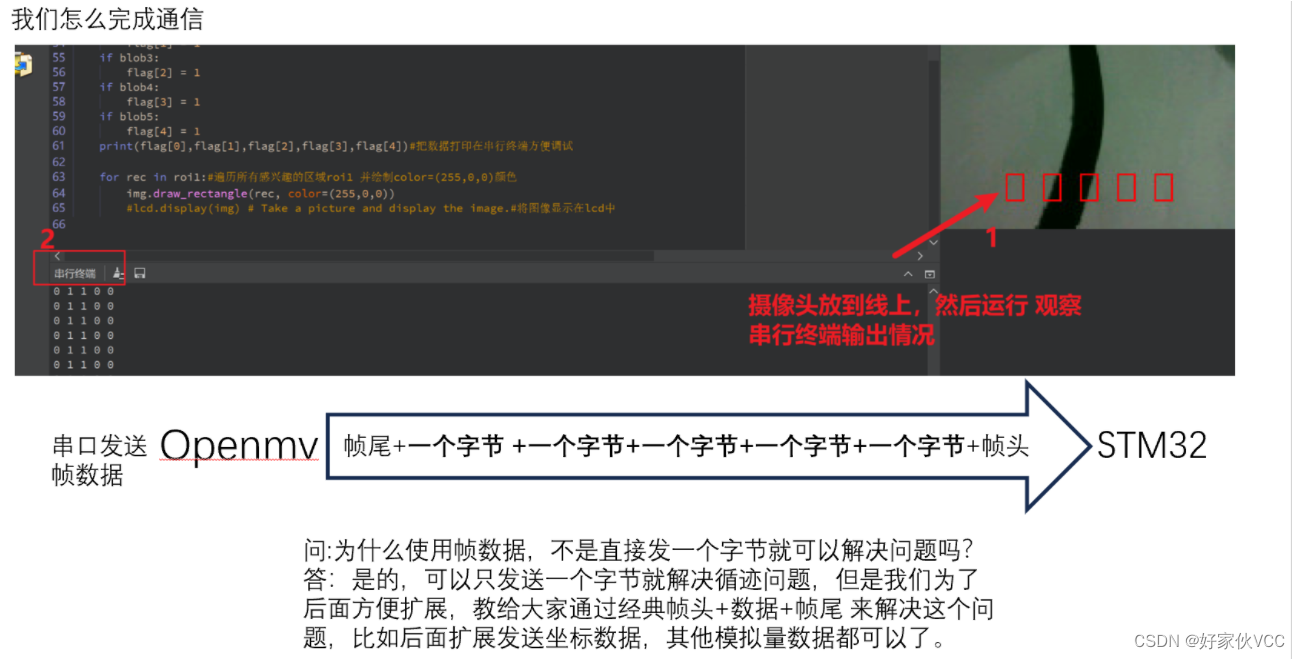

19.3-星曈科技 openmv Hopenmv發(fā)送五個uchar Openmv+STM32F103C8T6視覺巡線小車 STM32循跡小車系列教程

為什么FREERTOS不是用SYSTIMER做TICK的時鐘源呢?

安徽京準(zhǔn)-時間源服務(wù)器(NTP網(wǎng)絡(luò)時鐘源)在醫(yī)療中的重要性

求助,關(guān)于STM32U5的HIGH SPEED USB時鐘源的問題求解

請問CYT4BF8CDS如何更改PWM中的時鐘源?

機器視覺系統(tǒng)五個模塊介紹

STM32CubeMX 6.5.0時鐘配置頁面的ADC時鐘源無法配置怎么解決?

如何解決同步時鐘系統(tǒng)中的常見問題和故障?

STM32系統(tǒng)中的五個時鐘源介紹

STM32系統(tǒng)中的五個時鐘源介紹

評論