為了適應(yīng)大量的嵌入式產(chǎn)品的網(wǎng)絡(luò)接入需求,目前市場上的主流嵌入式操作系統(tǒng)都包含了 TCP/IP 網(wǎng)絡(luò)協(xié)議棧。這些商品化的TCP/IP協(xié)議棧運(yùn)行可靠、性能也非常好,但是價格較高,降低了市場競爭力。因此,開發(fā)自主知識產(chǎn)權(quán)的TCP/IP協(xié)議棧的要求變的日益迫切而有意義。本文的研究目標(biāo)是建立一個DSP系統(tǒng)的網(wǎng)絡(luò)通信平臺,實現(xiàn)DSP系統(tǒng)與網(wǎng)絡(luò)中其他通信設(shè)備的高速數(shù)據(jù)傳輸。

系統(tǒng)總體設(shè)計

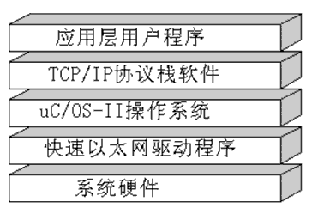

本文研究的以太網(wǎng)通信系統(tǒng)大致分為圖1所示的5個層次,由下向上分別為:硬件層、設(shè)備驅(qū)動層、操作系統(tǒng)、網(wǎng)絡(luò)模塊和用戶代碼。

圖1 系統(tǒng)的層次結(jié)構(gòu)

本系統(tǒng)的創(chuàng)新之處是以DSP系統(tǒng)和以太網(wǎng)控制芯片Ax88796的接口電路為系統(tǒng)的物理基礎(chǔ)。快速以太網(wǎng)驅(qū)動程序處于硬件抽象層,為操作系統(tǒng)提供了訪問快速以太網(wǎng)控制芯片 Ax88796 或改變其工作行為的系統(tǒng)調(diào)用。μC/OS-Ⅱ操作系統(tǒng)處于系統(tǒng)內(nèi)核,為用戶代碼統(tǒng)一管理系統(tǒng)軟硬件資源提供用戶所需的底層服務(wù)。TCP/IP 協(xié)議棧軟件為 μC/OS-Ⅱ操作系統(tǒng)擴(kuò)展了網(wǎng)絡(luò)通信能力。用戶代碼處理特定的應(yīng)用程序細(xì)節(jié)。

系統(tǒng)硬件設(shè)計

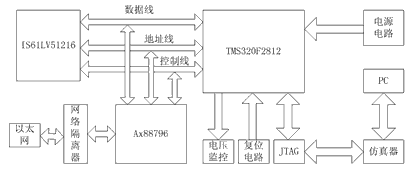

系統(tǒng)硬件包括TMS320F2812 DSP與IS61LV51216存儲器芯片的接口電路以及TMS320F2812與快速以太網(wǎng)控制芯片Ax88796的接口電路,電路硬件原理框圖如圖2所示。

圖2 硬件原理圖

TMS320F2812是TI新推出的高端C2000系列DSP,它在具備強(qiáng)大運(yùn)算能力的同時,兼顧了控制領(lǐng)域的需求,特別適合控制對象復(fù)雜又需要較高實時運(yùn)算能力的領(lǐng)域。它具有150MIPS的指令執(zhí)行速度;單周期完成 32×32 位的乘法器;快速中斷響應(yīng);單指令周期的讀寫操作;100~120MIPS的Flash訪問技術(shù);150MIPS的外部RAM訪問速度。基于以上特點(diǎn),本系統(tǒng)選擇TMS320F2812作為系統(tǒng)的主控芯片。

[table][/table]

DSP電源電路提供1.8V/1.9V、 3.3V、VDD3VFL和VDDA3V四種電源類型,分別供DSP的內(nèi)核、I/O、內(nèi)部 Flash 和AD模塊使用。并且由于各種電源類型存在嚴(yán)格的上/下電時序,電源部分還需提供時序控制功能。電源監(jiān)控電路在系統(tǒng)電源電壓出現(xiàn)波動時,給DSP系統(tǒng)提供復(fù)位信號,使系統(tǒng)程序重新初始化并運(yùn)行,避免出現(xiàn)不可預(yù)知的錯誤。

面對表面貼技術(shù)造成的測試上的不便,JTAG接口提供了簡單靈活的調(diào)試手段,用戶可以通過 JTAG接口,將在 PC交叉編譯生成的結(jié)果下載到DSP中,或者通過JTAG接口即時查看DSP內(nèi)部寄存器和RAM的值,對程序的行為進(jìn)行調(diào)試。系統(tǒng)的軟件代碼在調(diào)試階段存放在擴(kuò)展的RAM中,脫機(jī)運(yùn)行后,用于存儲傳輸?shù)膱D像數(shù)據(jù),故擴(kuò)展了512KB。以太網(wǎng)控制芯片Ax88796通過ISA接口與DSP相連,通過網(wǎng)絡(luò)隔離器16ST8515后,接入以太網(wǎng)絡(luò)中。

1 Ax88796與TMS320F2812的接口設(shè)計

TMS320F2812通過XINTF接口訪問外部設(shè)備,每次訪問都分為三個階段:前導(dǎo)(Lead)、有效(Active)和跟隨(Trail),每個階段的等待周期數(shù)都可由軟件設(shè)定,等待的時鐘周期數(shù)由該存儲區(qū)間對應(yīng)的XTIMING寄存器設(shè)置,而且每個存儲區(qū)間的讀寫過程可以單獨(dú)控制。

TMS320F2812通過對采樣XREADY信號輸入引腳來判斷外部設(shè)備是否完成數(shù)據(jù)讀/寫。當(dāng)外部低速設(shè)備的讀/寫過程未執(zhí)行完成時,輸出信號 READY為未就緒狀態(tài),此時TMS320F2812持續(xù)保持?jǐn)?shù)據(jù)有效(寫訪問)或保持等待數(shù)據(jù)(讀訪問)狀態(tài),即ACTIVE狀態(tài)。一旦 TMS320F2812對該信號的采樣結(jié)果是就緒狀態(tài),則結(jié)束本次數(shù)據(jù)讀寫過程。

在TMS320F2812對Ax88796進(jìn)行讀操作時,設(shè)置Lead和Trail階段為0個時鐘周期,Active 階段為5個時鐘周期;在TMS320F2812對Ax88796進(jìn)行寫操作時,設(shè)置Lead階段為0個時鐘周期,Active階段為1個時鐘周期, Trail階段為1個時鐘周期。

2 Ax88796的ISA接口設(shè)計

Ax88796有兩個輸入引腳,CPU[1:0]設(shè)置不同的工作模式,用于和不同的CPU總線相連。在與TMS320F2812連接時,將CPU[1:0]都拉低,設(shè)置為ISA總線接口。

Ax88796的地址總線SA與數(shù)據(jù)總線SD分別與TMS320F2812的地址/數(shù)據(jù)總線相連,TMS320F2812通過I/O讀寫 Ax88796的寄存器來控制其狀態(tài),通過遠(yuǎn)程DMAFIFO與Ax88796的內(nèi)部SRAM進(jìn)行數(shù)據(jù)交換。Ax88796的基地址默認(rèn)值為200H,所以基地址范圍為200H~21FH。Ax88796的ISA接口有10根地址線——SA[9:0]。

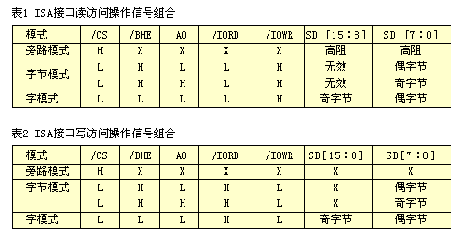

Ax88796的BHE引腳決定了是否使能高8位數(shù)據(jù)線,如果 BHE 信號為高,則高8位數(shù)據(jù)線內(nèi)部強(qiáng)行下拉,此時Ax88796工作在8位傳輸模式下。表1和表2是 Ax88796 在 ISA 模式時的訪問信號組合。

可以看出,對奇偶字節(jié)地址的訪問方式是不同的,但對于TMS320F2812而言,地址空間是按16位字尋址,所以所有的地址都是偶字節(jié)地址,這樣對地址線A0就無須再作專門處理,連線簡潔。在本課題中,直接將BHE接地,始終使用16位傳輸模式。

3 系統(tǒng)RAM擴(kuò)展

TMS320F2812內(nèi)部已經(jīng)集成了18KB的RAM,對于一般的應(yīng)用來說,已經(jīng)無須再擴(kuò)展外部RAM。片內(nèi)RAM能以150MIPS的速度進(jìn)行訪問。在對運(yùn)算速度要求很高的處理程序中,通常將經(jīng)常訪問的程序段放到內(nèi)部RAM中運(yùn)行,這樣能大大提高運(yùn)行速度,因此片內(nèi)RAM顯得格外寶貴。而且本系統(tǒng)是一個網(wǎng)絡(luò)通信系統(tǒng),將來會用于進(jìn)行大量圖像的網(wǎng)絡(luò)傳輸,因而也要求外括RAM用于存放圖像文件。

TMS320F2812采用32位的尋址方式,數(shù)據(jù)空間和程序空間統(tǒng)一編址。TMS320F2812有1056K×16 bit的外部存儲器接口能力,分為5個地址區(qū)間:區(qū)間0、區(qū)間1、區(qū)間2、區(qū)間6和區(qū)間7,其中區(qū)間6、7共用一個片選引腳 CS6AND7。在 MP模式下,TMS320F2812 在復(fù)位之后,跳轉(zhuǎn)到區(qū)間7尋找矢量表,但是在MC模式下,將不存在區(qū)間 7,由片內(nèi)的ROM取而代之,所以在擴(kuò)展系統(tǒng)RAM時,使用RAM區(qū)間6。

系統(tǒng)軟件設(shè)計

本系統(tǒng)的軟件部分包含3個方面:快速以太網(wǎng)驅(qū)動程序、μc/OS-II操作系統(tǒng)和TCP/IP協(xié)議棧軟件。快速以太網(wǎng)驅(qū)動程序屏蔽了對底層網(wǎng)絡(luò)設(shè)備的處理細(xì)節(jié),同時向上層操作系統(tǒng)提供硬件無關(guān)的接口調(diào)用。在以太網(wǎng)通信之前,首先要實現(xiàn)位于硬件抽象層的快速以太網(wǎng)驅(qū)動程序,上層軟件與以太網(wǎng)控制器的交互都要通過驅(qū)動程序進(jìn)行。網(wǎng)絡(luò)通信系統(tǒng)通常要與多個對象實現(xiàn)信息共享,因此本文為TMS320F2812DSP移植了嵌入式多任務(wù)操作系統(tǒng)μC/OS- II,增強(qiáng)系統(tǒng)的事務(wù)處理能力。TCP/IP是實現(xiàn)異構(gòu)網(wǎng)絡(luò)互聯(lián)的網(wǎng)絡(luò)體系結(jié)構(gòu)和協(xié)議標(biāo)準(zhǔn),屏蔽各種物理網(wǎng)絡(luò)技術(shù)。本文結(jié)合嵌入式系統(tǒng)的特定要求進(jìn)行簡化之后,實現(xiàn)了地址解析協(xié)議ARP、網(wǎng)際協(xié)議IP、網(wǎng)際控制報文協(xié)議ICMP、用戶數(shù)據(jù)報協(xié)議UDP和TCP傳輸控制協(xié)議等幾個Internet接入的必需協(xié)議。

系統(tǒng)測試及結(jié)果

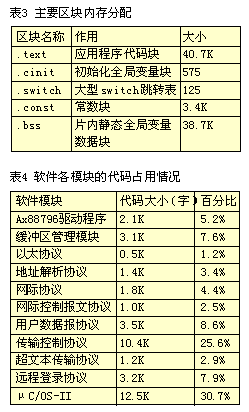

用ANSIC語言和匯編語言在TMS320F2812上編寫的網(wǎng)絡(luò)通信軟件全部調(diào)試通過,系統(tǒng)軟件占用程序空間40.7KB,數(shù)據(jù)空間38.7KB。表3和表4分別是主要區(qū)塊內(nèi)存分配和協(xié)議代碼占用情況。

結(jié)束語

綜合性的測試表明本系統(tǒng)完全滿足了網(wǎng)絡(luò)通信系統(tǒng)所具備的各項功能,它將DSP的強(qiáng)大運(yùn)算處理能力和Internet聯(lián)系起來,使得DSP系統(tǒng)不再是“信息孤島”,能夠方便的與網(wǎng)絡(luò)上的其他設(shè)備進(jìn)行信息共享,進(jìn)一步擴(kuò)展了DSP的應(yīng)用前景。

責(zé)任編輯:gt

-

dsp

+關(guān)注

關(guān)注

557文章

8161瀏覽量

358121 -

芯片

+關(guān)注

關(guān)注

460文章

52568瀏覽量

441891 -

以太網(wǎng)

+關(guān)注

關(guān)注

41文章

5684瀏覽量

176261

發(fā)布評論請先 登錄

Ax88796實現(xiàn)SA1110的軟件方面

MSP430實現(xiàn)以太網(wǎng)高速數(shù)據(jù)傳輸

基于Ax88796的SA1110以太網(wǎng)接口設(shè)計

采用AX88796C實現(xiàn)低功耗以太網(wǎng)接口模塊設(shè)計

如何用Ax88796實現(xiàn)SA1110的以太網(wǎng)接口?

基于AX88796 的以太網(wǎng)接口的設(shè)計與實現(xiàn)

基于以太網(wǎng)的指紋門禁控制器設(shè)計與實現(xiàn)

基于千兆以太網(wǎng)的高速數(shù)據(jù)傳輸系統(tǒng)設(shè)計

基于W5300的以太網(wǎng)數(shù)據(jù)傳輸系統(tǒng)的設(shè)計

基于FPGA和W5300的以太網(wǎng)數(shù)據(jù)傳輸系統(tǒng)的設(shè)計與實現(xiàn)

一種基于FPGA的以太網(wǎng)高速傳輸平臺

以太網(wǎng)數(shù)據(jù)傳輸系統(tǒng)的設(shè)計與應(yīng)用介紹

光纖接口轉(zhuǎn)為以太網(wǎng)接口數(shù)據(jù)傳輸系統(tǒng)的實現(xiàn)方法

基于W5300的以太網(wǎng)數(shù)據(jù)傳輸系統(tǒng)的設(shè)計與實現(xiàn)

評論