作者:董懷玉,余寧梅,高勇,劉高輝,牛蘭奇,陳靜瑾

數字信號在傳輸過程中可能受到各種干擾及信道傳輸特性不理想的影響而使信號發生錯誤, 從而接收到錯誤的信息。為了實現數字系統在傳輸過程中的可靠性, 幾乎所有的現代通信系統都把糾錯編碼作為一個基本組成部分。Reed-So lomon (RS)碼是目前最有效、應用最廣的差錯控制編碼之一,是一類具有很強糾錯能力的多進制BCH 碼, 它既可以糾正突發錯誤, 也可以糾正隨機錯誤。RS 碼主要應用于實時性較高的移動通信系統、深空通信、數字衛星電視、磁記錄系統等方面。

目前對RS 編碼器的設計主要局限于單一碼長和固定糾錯能力的RS 碼編碼器設計。本文提出的這種碼長可變、糾錯能力可調的RS 編碼器是把常用的RS (7, 3) 碼、RS (15, 11) 碼、RS (15, 9) 碼在一個編碼電路中實現, 把它做成IP 核, 這樣既可以大大地減少了芯片的面積而且給用戶提供了方便,又有很大的選擇空間。該編碼電路采用基于多項式乘法理論GF (2m ) 上的m 位快速有限域乘法的方法, 使電路的編碼速度有了很大的提高。本文設計的編碼器的最高工作頻率可達到100MHz, 完全滿足無線通信中,語音通信和數據通信的數據傳輸速率為幾百kbp s 的要求。

編碼算法選取

一般來說, RS 碼可以用(n, k , t) 三個參數來表示, 其中n 表示碼字長度, k 表示信息位長度, t 為糾錯能力, 滿足關系: t= (n- k )/2。RS 碼的所有元素都是定義在GF (2m ) 上, 其中有:m = log2n。對于不同的m 對應著一個本原多項式, 從本原多項式就可以得到有限域各元素。

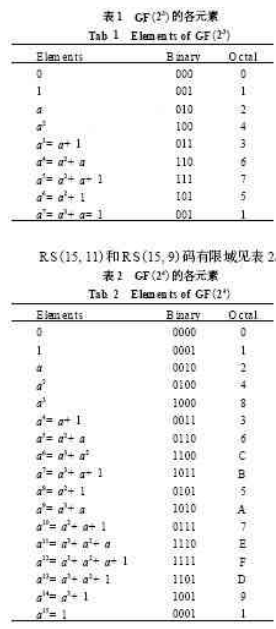

RS (7, 3) 碼的有限域見表1。

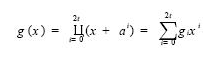

RS 編碼的生成多項式定義為:

所以可以得到各碼的生成多項式:

RS (7, 3) 碼:

g (x ) = x 4 + a3x 3 + x 2 + ax + a3

RS (15, 11) 碼:

g (x ) = x 4 + a13x 3 + a6x 2 + a3x + a10

RS (15, 9) 碼:

g (x ) = x 6 + a10x 5 + a14x 4 + a4x 3 +a6x 2 + a9x + a6

用m (x ) 表示信息碼字多項式, c (x ) 表示編碼后的碼字多項式, 則RS 碼的編碼過程可以用下面編碼多項式來表示:

c (x ) = m (x ) x n- k + [m (x ) x n- k ]modg (x )

上式中, [m (x ) x n- k ]modg (x ) 是求余運算, 得到是校驗位。

RS 編碼器的硬件實現過程, 就是運用電路來完成上述編碼多項式中信息位多項式k (x ) 與x n- k的乘法運算及k (x ) x n- kmodg (x ) 的求余運算的過程。下面將詳細討論編碼電路的構成及工作原理。

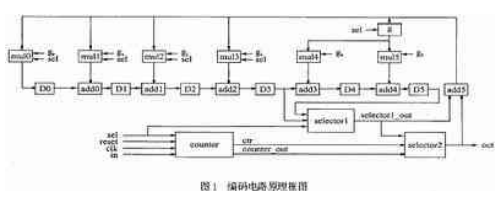

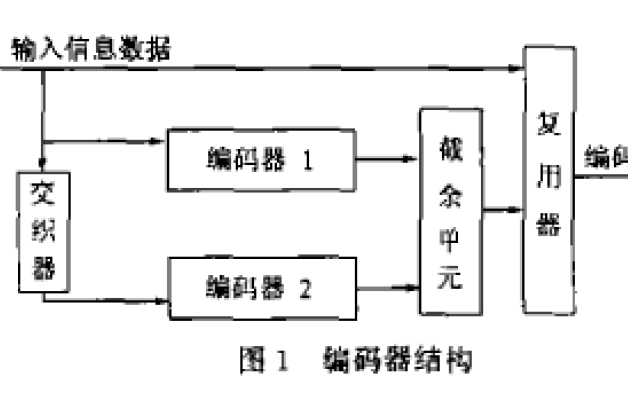

編碼電路的實現

RS編碼電路的求余運算可以用n- k 級的移位寄存器來實現, 因此可以選取6 級的移位寄存器; 信息位的輸入個數用計數器來控制, 可以加一選擇端來控制計數器是對哪一種碼字進行編碼計數; 信息位與校驗位的輸出可以用選擇器來切換。因此我們可以得到編碼電路的原理框圖如圖1。

在圖1 的電路中, 所有的信息數據傳輸均采用4 位比特寬的傳輸。Reset 是系統復位信號。電路的工作原理描述如下:

(1) 當sel 置為01 時, 編碼電路處于RS (7, 3)碼的編碼狀態。因為RS (7, 3) 碼的信息用3 位的二進制表示, 所以數據線的最高位為零, 只有低3 位起作用。

A 編碼前首先給電路一個reset 復位信號,使計數器和移位寄存器中的觸發器處于零狀態, 復位采用異步復位。

B 輸入信息(m 2, …,m 0 ) , 計數器開始計數,每輸入一個信息位, 計數器計一次數, 然后輸出。此時, selecto r2 的輸出與計數器的輸出端相接, 因此信息位一方面從編碼電路的輸出端輸出, 另一方面送入移位寄存器電路進行求余運算。

C當3 位信息位輸入完后, 計數器輸出一個控制信號ct r, 它是控制信息位與校驗位的輸出, 此時selcto r2 的輸出與selecto r1 的輸出端相接,add5 的兩個輸入端均為selecto r1 的輸出端, 由于有限域加法不考慮各位之間的進位, 因此add5 的輸出為0, 從而各乘法器m u l 的輸出為0, 所以移位寄存器中的校驗位會一次輸出。所以校驗位(D 3,…,D 0) 一次輸出。校驗位輸出后寄存器和計數器回到零狀態。因而得到編碼后的碼字為(m 2, 。,m 0,D 3, …,D 0)。

D 因為RS (7, 3) 碼編碼電路的求余運算只需要4 級的移位寄存器來實現, 因此開關K 斷開,后面兩級移位寄存器不工作, 這樣就降低了電路的功耗。A dd5 的輸入端接D3 的輸出端。

(2) 當sel 置為10 時, 編碼電路處于RS (15,11) 碼的編碼狀態, 在編碼前要給電路一個復位信號。過程與上面一樣, 編碼后得到碼字為(m 10, …,m 0, D 3, …,D 0)。同樣RS (15, 11) 碼編碼電路的求余運算只需要4 級的移位寄存器來實現, 因此K斷開, add5 的輸入端接D3 的輸出端。

(3) 當sel 置為11 時編碼電路處于RS (15, 9)碼的編碼狀態, 編碼前, 給電路一個復位信號。編碼后便可得到碼字為(m 8, …, m 0, D 3, …, D 0 )。RS(15, 9) 碼編碼電路的求余運算要6 級的移位寄存器來實現。因此K 開通, add5 的輸入端接D5 的輸出端。

在編碼電路中乘法器采用了基于多項式乘法理論GF (2m ) 上的m 位有限域乘法的方法, 大大地提高了電路的運算速度。

快速有限域乘法器實現:

快速有限域乘法的實現思路如下, 以RS (7, 3)碼為例:

因此就可以實現快速有限域乘法器, 這樣對電路的運算速度將會有很大的提高。由于RS (15,11) 碼和RS (15, 9) 碼基于同一個有限域GF (24 ) ,因此它們的乘法器一樣。當sel 置為01 時, 乘法器工作在GF (23 ) 的乘法狀態, 當sel 置為10 或11時, 乘法器工作在GF (24) 的乘法狀態。只不過工作在GF (23 ) 狀態時乘法器輸入輸出端的第4 位為0。

電路仿真及測試

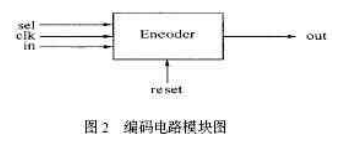

編碼電路模塊可以表示為:

sel 是編碼電路的選擇端, clk 是時鐘輸入端,reset 是系統復位端, in 是信息輸入端, ou t 是碼字輸出端。

用V erilog HDL 語言編寫電路的代碼后, 再用Cadence 公司的NC V erilog HDL 仿真工具進行仿真, 得到各種編碼的仿真結果。

A ) 給reset 一個復位信號, 使電路處于零狀態, sel 置為01 時, 輸入信息電路開始編碼。輸入信息位為(0, 1, 2) , 編碼后得到校驗位(2, 3, 1, 3) , 因此輸出端輸出碼字為(0, 1, 2, 2, 3, 1, 3)。然后再輸入信息位, 循環進行編碼。

B) 給reset 一個復位信號, sel 置為10 時, 輸入信息電路開始編碼。輸入信息為(0, 1, 2, 3, 4, 5, 6,7, 8, 9,A ) , 編碼后得到校驗位(C, E, 8, 3) , 所以輸出端輸出碼字為(0, 1, 2, 3, 4, 5, 6, 7, 8, 9,A , C, E,8, 3)。輸入端再次輸入信息, 循環進行編碼。輸出波形如圖4 所示。

C) 給reset 一個復位信號, sel 置為11 時, 輸入信息電路開始編碼。輸入信息為(0, 1, 2, 3, 4, 5,6, 7, 8) , 編碼后得到校驗位(B, C, 0, 5, 7, 8) , 所以輸出端輸出碼字為(0, 1, 2, 3, 4, 5, 6, 7, 8,B, C, 0,5, 7, 8)。輸入端再次輸入信息, 循環進行編碼。

仿真完成后, 采用Xilinx 的FPGA 板, 主芯片為SPARTAN II XC2SPQ 208 進行驗證, 輸入信息與仿真輸入的信息一致, 然后用邏輯分析儀觀測輸出結果。

A ) 給reset 一個復位信號后, 使電路工作在RS (7, 3) 碼的編碼狀態。用邏輯分析儀觀測輸入與輸出的結果如下圖6 所示, 虛線圈起來的(0, 1, 2,2, 3, 1, 3) 表示一個完整的輸出碼字。

B) 先使電路復位, 然后讓電路工作在RS (15,11) 碼的編碼狀態, 用邏輯分析儀觀測輸入與輸出結果如下圖7 所示, 虛線圈起來的(0, 1, 2, 3, 4, 5,6, 7, 8, 9,A , C, E, 8, 3) 表示一個完整的輸出碼字。

C) 電路復位后, 使它工作在RS (15, 9) 碼的編碼狀態, 用邏輯分析儀觀測結果如下圖8 所示, 虛線圈起來的(0, 1, 2, 3, 4, 5, 6, 7, 8,B, C, 0, 5, 7, 8)表示一個完整的輸出碼字。

從上面的仿真波形和測試結果可以看到他們的輸出結果一致, 驗證了設計的正確性。

電路參數

用Xilinx 公司的Pro ject Navigator 綜合工具對電路代碼進行綜合后, 得到電路的等效門單元數1339; 測得電路的靜態功耗為12.50 mW , 最高作頻率為100MHz。

結論

提出了一種碼長可變、糾錯能力可調的RS 碼編碼器, 它解決了以往RS 編碼器只能對單一碼長和固定糾錯能力編碼的局限, 同時采用快速有限域乘法的方法提高了電路的運算速度。設計后通過在FPGA 上測試, 驗證了設計的正確性。

責任編輯:gt

-

編碼器

+關注

關注

45文章

3706瀏覽量

135755 -

寄存器

+關注

關注

31文章

5390瀏覽量

121892 -

IP核

+關注

關注

4文章

332瀏覽量

49852

發布評論請先 登錄

相關推薦

采用路徑搜索的并行RS編碼器IP自動生成方法

RS通信編碼器怎么進行優化設計?

什么是編碼器 什么叫編碼器 編碼器什么意思

RS連續編碼器的FPGA設計與實現

絕對值編碼器原理

卷積Turbo碼編碼器及CPLD的實現工程中的關鍵問題

在編碼電路中實現RS碼編碼器IP核的應用設計

在編碼電路中實現RS碼編碼器IP核的應用設計

評論