1、什么是SPI?SPI是串行外設接口(Serial Peripheral Interface)的縮寫,是 Motorola 公司推出的一種同步串行接口技術,是一種高速、全雙工、同步的通信總線。2、SPI優點支持全雙工通信

通信簡單

數據傳輸速率塊

3、缺點沒有指定的流控制,沒有應答機制確認是否接收到數據,所以跟IIC總線協議比較在數據可靠性上有一定的缺陷。

4、特點

(1):高速、同步、全雙工、非差分、總線式

(2):主從機通信模式5、SPI電路連接

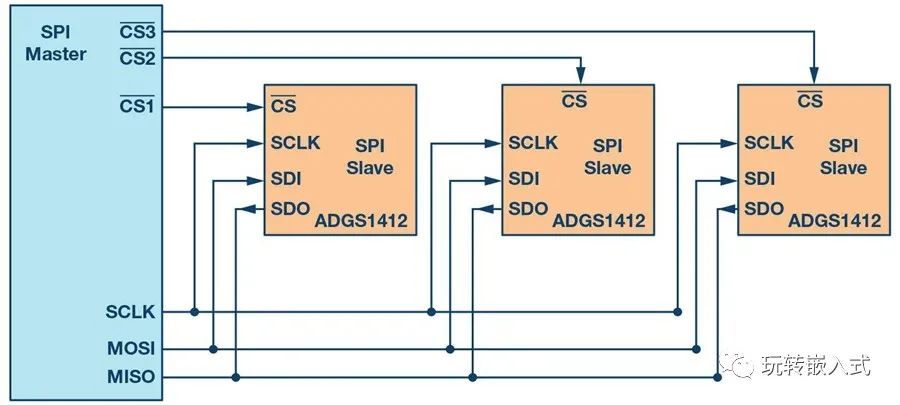

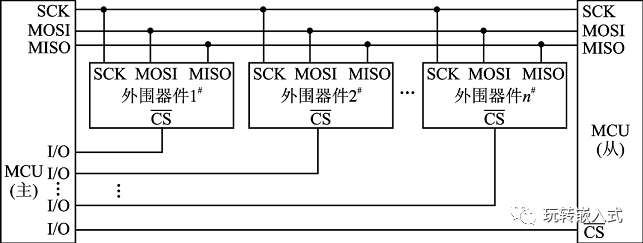

(1):SPI的通信原理很簡單,它以主從方式工作,這種模式通常有一個主設備和一個或多個從設備,有三線制和四線制之分。信號線包括SDI(串行數據輸入 Serial Digital IN)、SDO(串行數據輸出 Serial Digital OUT)、SCLK(時鐘)、CS(片選)。

(2):SDO/MOSI – 主設備數據輸出,從設備數據輸入

(3):SDI/MISO – 主設備數據輸入,從設備數據輸出

(4):SCLK – 時鐘信號,由主設備產生;(5):CS/SS – 從設備使能信號,由主設備控制。當有多個從設備的時候,因為每個從設備上都有一個片選引腳接入到主設備機中,當主設備和某個從設備通信時將需要將從設備對應的片選引腳電平拉低(一般低有效)。

6、SPI通信模式分析SPI通信有4種不同的模式,不同的從設備在出廠時配置模式已經固定, 這是不能改變的,但通信雙方設備必須工作在同一模式下,所以可以對主設備的SPI模式進行配置,通過CPOL(時鐘極性)和CPHA(時鐘相位)來控制主設備的通信模式。 具體模式具體如下:

:CPOL=0,CPHA=0

Mode1:CPOL=0,CPHA=1

Mode2:CPOL=1,CPHA=0

Mode3:CPOL=1,CPHA=1

| 模式 | CPOL | CPHA |

|---|---|---|

| Mode0 | 0 | 0 |

| Mode1 | 0 | 1 |

| Mode2 | 1 | 0 |

| Mode3 | 1 | 1 |

時鐘極性CPOL是用來配置SCLK電平的有效態的;

時鐘相位CPHA是用來配置數據采樣是發生在第幾個邊沿的。 CPOL=0表示當SCLK=0時處于空閑態,所以SCLK處于高電平時有效;

CPOL=1表示當SCLK=1時處于空閑態,所以SCLK處于低電平時有效;

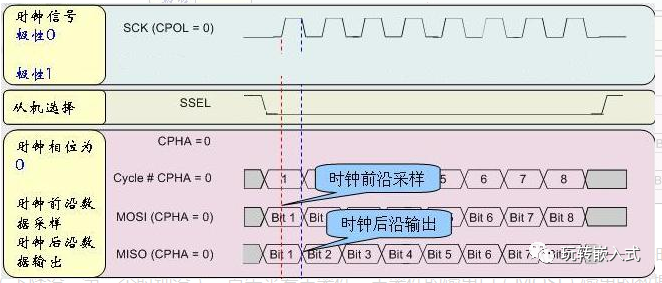

CPHA=0表示數據采樣是在第1個邊沿,數據發送在第2個邊沿;

CPHA=1表示數據采樣是在第2個邊沿,數據發送在第1個邊沿; SPI主模塊和與之通信的外設通信時,兩者的時鐘相位和極性應該保持一致。7、SPI 時序詳解CPOL=0,CPHA=0:此時空閑態時,SCLK處于低電平,數據采樣是在第1個邊沿,也就是SCLK由低電平到高電平的跳變,所以數據采樣是在上升沿,數據發送是在下降沿。 CPOL=0,CPHA=1:此時空閑態時,SCLK處于低電平,數據發送是在第1個邊沿,也就是SCLK由低電平到高電平的跳變,所以數據采樣是在下降沿,數據發送是在上升沿。 CPOL=1,CPHA=0:此時空閑態時,SCLK處于高電平,數據采集是在第1個邊沿,也就是SCLK由高電平到低電平的跳變,所以數據采集是在下降沿,數據發送是在上升沿。 CPOL=1,CPHA=1:此時空閑態時,SCLK處于高電平,數據發送是在第1個邊沿,也就是SCLK由高電平到低電平的跳變,所以數據采集是在上升沿,數據發送是在下降沿。

注意:SPI主設備能夠控制時鐘信號,因為SPI通信并不像UART或者IIC通信那樣有專門的通信周期、通信起始信號、通信結束信號;所以SPI協議只能通過控制時鐘信號線,在沒有數據交流的時候,時鐘線要么是保持高電平,要么是保持低電平。 例如:工作在模式0這種時序(CPOL=0,CPHA=0),如下:

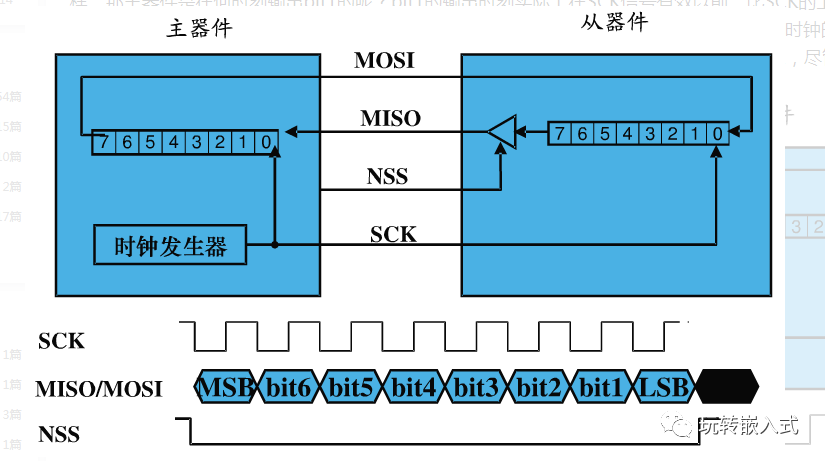

我們來關注SCK的第一個時鐘周期,在時鐘的前沿采樣數據(上升沿,第一個時鐘沿),在時鐘的后沿輸出數據(下降沿,第二個時鐘沿)。首先來看主器件,主器件的輸出口(MOSI)輸出的數據bit1,在時鐘的前沿被從器件采樣,那主器件是在何時刻輸出bit1的呢?bit1的輸出時刻實際上在SCK信號有效以前,比SCK的上升沿還要早半個時鐘周期。

bit1的輸出時刻與SSEL信號沒有關系。再來看從器件,主器件的輸入口MISO同樣是在時鐘的前沿采樣從器件輸出的bit1的,那從器件又是在何時刻輸出bit1的呢。從器件是在SSEL信號有效后,立即輸出bit1,盡管此時SCK信號還沒有起效。 從這張圖就可以很清楚的看出主從器件的bit1是怎樣輸出的。

編輯:jq

-

SPI

+關注

關注

17文章

1706瀏覽量

91508 -

IIC

+關注

關注

11文章

300瀏覽量

38311 -

SCK

+關注

關注

0文章

7瀏覽量

16114 -

miso

+關注

關注

0文章

7瀏覽量

5421

原文標題:SPI怎么玩?搞懂時序,運用自如

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

KeyStone架構串行外設接口(SPI)手冊

ADS9224R使用SPI常規模式,讀數據無返回,請問具體的讀數據的時序應該是怎樣的?

請問下DAC1282的SPI時序是CPOL=0,CPHA=0嗎?

瀚海微SD NAND之SD 協議(42)SPI總線時序

手把手帶你移植HAL庫函數

想搞懂通信協議?先來看一篇SPI熱熱身

時序電路的分類 時序電路的基本單元電路有哪些

PCB阻抗設計12問,輕松帶你搞懂阻抗!

【華秋干貨鋪】PCB阻抗設計12問,輕松帶你搞懂阻抗

PCB阻抗設計12問,輕松帶你搞懂阻抗!

搞懂時序帶你玩轉SPI?

搞懂時序帶你玩轉SPI?

評論