數字濾波器在數字信號處理的各種應用中發揮著十分重要的作用,他是通過對采樣數據信號進行數學運算處理來達到頻域濾波的目的。數字濾波器既可以是有限長單脈沖響應(FIR)濾波器也可以是無限長單脈沖響應(IIR)濾波器。在維納濾波器理論發明的早期,人們使用IIR濾波器,但現在更多是使用FIR濾波器。本文按照Matlab/Simulink/DSP Builder/QuartusⅡ流程,設計一個FIR濾波器。Altera DSP Builder是連接Simulink和QuartusⅡ開發軟件的DSP開發工具。在DSP Builder的無縫設計流程中,首先在Matlab軟件中進行算法設計,然后在Simulink軟件中進行系統集成,最后將設計輸出為硬件描述語言(HDL)文件,以便在QuartusⅡ軟件中使用。

1 FIR濾波器介紹

1.1 FIR濾波器原理

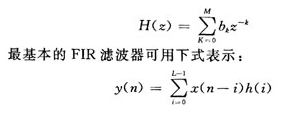

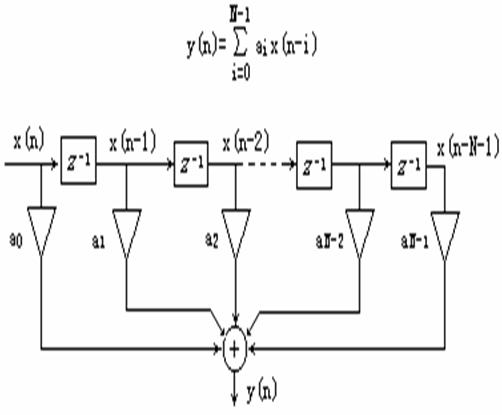

對于一個FIR濾波器系統,他的沖激響應總是有限長的,其系統函數可以記為:

其中:x(n)是輸入采樣序列;h(n)是濾波器系數;L是濾波器的階數;y(n)表示濾波器的輸出序列。也可以用卷積來表示輸出序列y(n)與x(n),h(n)的關系。

y(n)=x(n)*h(n)

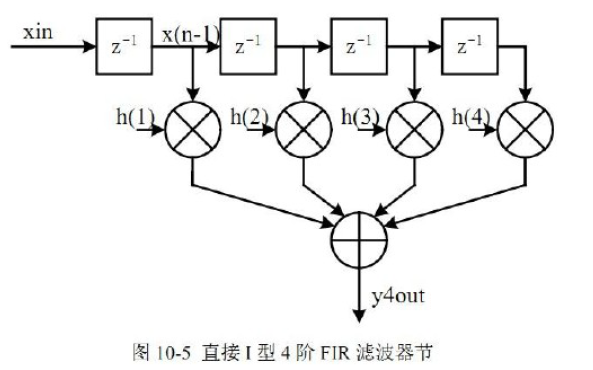

典型的直接I型FIR濾波器如圖1所示,其輸出序列y(n)滿足下式:

1.2 設計要求

數字濾波器實際上是一個采用有限精度算法實現的線性非時變離散系統,他的設計步驟是先根據需要確定其性能指標,設計一個系統函數h(n)逼近所需要的性能指標,濾波器的系數的計算可以借助Matlab強大的計算能力和現成的濾波器設計工具來完成,最后采用有限的精度算法實現。本系統的設計指標為,設計一個14階的FIR濾波器。1 MHz和16 MHz的兩個正弦波的合成波形,經過這個濾波器,濾除16 MHz的成分。

2 DSP Builder設計流程

使用DSP Builder完成設計時,首先在Matlab/Simulink軟件中建立模型文件(.mdl),DSP Builder SignalCom-piler模塊讀取由DSP Builder和MegaCore模塊構建的Simulink建模文件(.mdl),生成VHDL文件和工具命令語言(Tcl)腳本,進行綜合、硬件實施和仿真。

3 FIR數字濾波器的DSP Builder設計

3.1 Matlab/Simulink建模

根據FIR數字濾波器的算法,在Matlab的Simulink環境中建立一個MDL模型文件。用圖形方式調用Alter-aDSPBuilder和其他的Simulink庫中的圖形模塊。

3.2 在Simulink中仿真并生成VHDL代碼

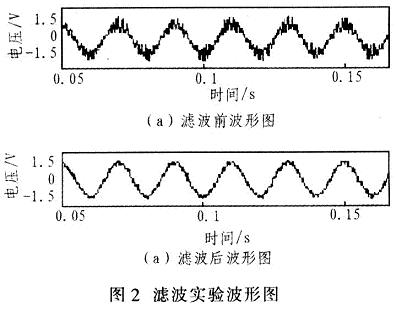

完成模型設計之后,可以先在Simulink中對模型進行仿真,可以通過Simulink中的示波器模塊查看各步驟的中間結果。輸入信號采用頻率為1 MHz和16 MHz的兩個正弦波的疊加。仿真結果如圖2所示。從仿真波形可以看出,經過FIR濾波器之后,16 MHz的高頻信號被很好地濾除了。

3.3 使用Modelsim進行RTL仿真

在Simulink中進行的仿真是屬于系統驗證性質的,是對mdl文件進行仿真,并沒有對生成的VHDL代碼進行過仿真。事實上,生成VHDL描述的是RTL級的,是針對具體的硬件結構的,而在Matlab的Simulink中的模型仿真是算法級的,兩者之間有可能存在軟件理解上的差異。轉換后的VHDL代碼實現可能與mdl模型描述的情況不完全相符。這就需要針對生成的RTL級VHDL代碼進行功能仿真,如圖3所示。

仿真結果說明,本濾波器可以較好地起到濾波的效果,由于輸入正弦波經過數字化過程之后在Modelsim中還原出的模擬波形出現失真現象。

3.4 使用QuartusⅡ進行時序仿真和綜合編譯

Modelsim完成的RTL級仿真只是功能仿真,其仿真結果并不能精確地反映電路的全部硬件特性,進行門級的時序仿真仍然是十分重要的。時序仿真即針對具體硬件芯片,在仿真時加入芯片內部的時間信息包括:建立時間,保持時間,關鍵路徑延時等。綜合編譯后,tsu=4.622 ns,tco=6.925 ns,th=0.415 ns,時間分析符合實際情況。

4 濾波器設計在FPGA上的實現

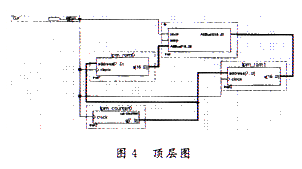

由于從Simulink建模仿真,到Modelsim RTL仿真和QuartusⅡ時序仿真,使用的輸入正弦波都是仿真信號,而不是實際的信號源。在硬件實際運行時,可以從外部信號源接入芯片內部或者在芯片內部存儲正弦波的數據。這里采用的是后者,即在頂層文件中引入LPM_ROM宏模塊,在其中存入正弦波數據的mif文件(存儲初始化文件),FIR濾波器模塊直接從ROM中讀取數據,經過濾波處理之后數據存入另一ROM中,可以通過In-systemmemory content editor工具從中讀出數據,再利用Matlab還原出波形,從而在實際硬件中驗證了濾波器的功能。

實現的頂層圖如圖4所示。

5 結 語

本文采用Matlab/Simulink/DSP Builder/QuartusⅡ的設計流程,實現了14階FIR濾波器。通過系統仿真,RTL仿真,時序仿真和實際硬件測試(這里采用了一種不需要使用SignaltapⅡ軟件邏輯分析儀的方法)對濾波器的功能、性能等進行了分析,從而驗證了采用DSP,Builder實現濾波器設計的硬件化的獨特優勢。

責任編輯:gt

-

dsp

+關注

關注

553文章

7987瀏覽量

348745 -

濾波器

+關注

關注

161文章

7795瀏覽量

177996

發布評論請先 登錄

相關推薦

基于DSP的FIR濾波器的設計

FIR濾波器的FPGA設計與實現

使用DSP設計和仿真FIR濾波器

基于Matlab和DSP設計FIR數字濾波器方案

基于DSP開發工具實現FIR濾波器的設計

基于DSP開發工具實現FIR濾波器的設計

評論