近年來(lái),伴隨國(guó)內(nèi)芯片市場(chǎng)迅猛發(fā)展,芯片的驗(yàn)證、仿真、測(cè)試需求也隨之增大,且復(fù)雜度大大提升。在此情況下,國(guó)內(nèi)市場(chǎng)大規(guī)模芯片驗(yàn)證平臺(tái)短缺以及性能不足的問(wèn)題日漸凸顯。

2019年8月,賽靈思推出最大容量 FPGA —— Virtex UltraScale+ VU19P。其擁有 350 億個(gè)晶體管,具備有史以來(lái)單顆芯片最高邏輯密度和最大I/O 數(shù)量,可以支持未來(lái)最先進(jìn) ASIC 和 SoC 技術(shù)的仿真與原型設(shè)計(jì)。與此同時(shí),還廣泛支持測(cè)試測(cè)量、計(jì)算以及網(wǎng)絡(luò)等相關(guān)應(yīng)用。

高端 FPGA 新標(biāo)桿顯著提升開(kāi)發(fā)效率

作為全球第一代使用 FPGA 芯片的企業(yè)之一,新致華桑電子始終致力于將最先進(jìn)的 FPGA 技術(shù)應(yīng)用于其 PHINEDesign FPGA 原型開(kāi)發(fā)平臺(tái)。該平臺(tái)的前三代均基于賽靈思 FPGA 平臺(tái)而開(kāi)發(fā)。

在賽靈思 VU19P 推出之初,新致華桑便加入產(chǎn)品早期試用計(jì)劃,并將其應(yīng)用到第四代原型驗(yàn)證平臺(tái)的研發(fā)設(shè)計(jì)中。2020年底,新致華桑基于賽靈思 VU19P 的第四代 PHINEDesign 平臺(tái)——NE-VU19P-LSI應(yīng)運(yùn)而生。

新致華桑 NE-VU19P-LSI 將一些 ASIC 原型或大規(guī)模 SoC 開(kāi)發(fā)的驗(yàn)證效率提升高達(dá)了 30%。對(duì)于需要大規(guī)模驗(yàn)證的客戶,新平臺(tái)可以節(jié)省近50%的資源分區(qū)工作量,從而大大縮短驗(yàn)證周期,加快客戶的產(chǎn)品上市時(shí)間。

新一代 NE-VU19P-LSI 平臺(tái)具備諸多領(lǐng)先特性

? 總計(jì)超1800個(gè) I/O,通過(guò) FMC 標(biāo)準(zhǔn)連接器接出,可兼容賽靈思等各大廠商標(biāo)準(zhǔn)子卡,為用戶提供了豐富擴(kuò)展接口選擇;同時(shí)新致華桑也為客戶配備了適用于原型驗(yàn)證的各種FMC子卡。? 48路高速 GTY 收發(fā)器,最高可達(dá)25Gbps。

可通過(guò) FMC 或者 SLIMSAS 擴(kuò)展。保證了高速 SERDES 的性能,同時(shí)接口形態(tài)更便于多系統(tǒng)的級(jí)聯(lián)擴(kuò)展,而不會(huì)造成管腳的冗余。? 電壓可調(diào)的 FMC I/O,可適配多種外部接口調(diào)試。? 可擴(kuò)展多路 DDR4/DDR3 等存儲(chǔ)卡,速率可達(dá) FPGA 標(biāo)稱2400Mbps。? 豐富的全局時(shí)鐘與復(fù)位資源,可支撐各種頻率的應(yīng)用場(chǎng)景。

能夠滿足多時(shí)鐘域的驗(yàn)證需求,又能夠滿足多顆互聯(lián)時(shí)的時(shí)鐘同源要求。? 靈活的上位機(jī)管理軟件,提供界面化直觀便捷操作。? 同時(shí)提供命令行執(zhí)行方式。

編輯:jq

-

FPGA

+關(guān)注

關(guān)注

1629文章

21734瀏覽量

603098 -

芯片

+關(guān)注

關(guān)注

455文章

50756瀏覽量

423330 -

晶體管

+關(guān)注

關(guān)注

77文章

9684瀏覽量

138117 -

FMC

+關(guān)注

關(guān)注

0文章

93瀏覽量

19679

原文標(biāo)題:保障高效 IC 設(shè)計(jì)的秘訣

文章出處:【微信號(hào):賽靈思,微信公眾號(hào):Xilinx賽靈思官微】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

怎么集齊7個(gè)云平臺(tái)?本文教你!

探索光耦:光耦在開(kāi)關(guān)電源中的應(yīng)用——保障高效、安全的電源控制

開(kāi)關(guān)電源輻射老是超?教你一個(gè)好方法搞定它

TNY284-290過(guò)載功率隨輸入電壓變化很小的高效離線式開(kāi)關(guān)IC中文手冊(cè)

PL7305鋰電池充電IC,高效升壓型3節(jié)電池充電控制芯片

PL7304升壓型雙節(jié)鋰電池充電控制芯片,高效充電管理IC

T 型車載智能云臺(tái)驅(qū)動(dòng)方案中的恒功率輸出:穩(wěn)定與高效的保障

智能IC卡測(cè)試設(shè)備的技術(shù)原理和應(yīng)用場(chǎng)景

光伏氣象站:保障光伏發(fā)電高效穩(wěn)定的關(guān)鍵利器

音頻放大器IC性能參數(shù)解析:教你如何挑選合適型號(hào)

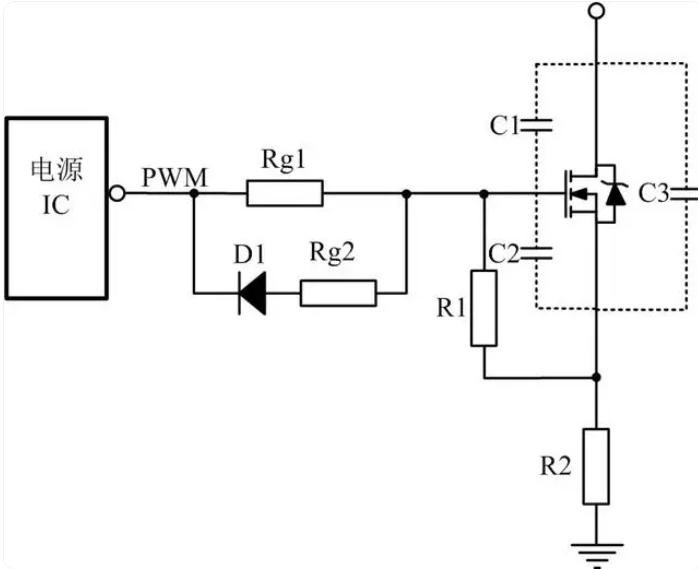

電源驅(qū)動(dòng)ic的作用是什么 電源IC驅(qū)動(dòng)電路設(shè)計(jì)圖

教你們?nèi)绾伪U细咝C設(shè)計(jì)

教你們?nèi)绾伪U细咝C設(shè)計(jì)

評(píng)論