作者:楊鎮西;丁有志;康東明

引言

會議電話是電信數字交換系統的一項重要業務,該業務可以實現多個用戶之間同時通話。以往會議電話大都采用專用芯片來實現,隨著DSP技術的進步,采用通用DSP實現會議電話由于具有容量大,成本低,升級靈活等優點,逐漸成為首選方案。

TI公司低功耗高性能的DSP TMS320VC5410具有3條獨立的數據總線和1條程序總線,提供高度并行性,其多通道緩沖串口McBSP(Multichannel Buffered Serial Port)可以很容易地接口數字交換系統中常用的ST-BUS鏈路,DMA控制器可以最大限度地減少DSP內部CPU的占用時間,片上RAM可以方便地提供程序運行空間和McBSP的收發數據緩沖區,因此本文中采用該DSP實現會議電話功能。

算法設計實現

會議電話的實現可以采用最大值輸出法。這種方法是將同一幀內到達的通話各方的話音幅度進行比較,一般是講話人的幅度最大,找出幅度最大的話音和幅度第二大的話音后將幅度第二大的話音送給講話人,而將幅度最大的話音送給其他用戶。

圖1 最大值輸出法會議電話示意圖

圖1是最大值輸出法會議電話的示意圖。圖中是以四方會議為例,A、B、C、D四方的第M幀PCM編碼送入TMS320VC5410后在第M+1幀期間進行比較,假定判斷出A的話音幅度最大,B 的話音幅度第二大,于是在第M+2幀B的話音送給用戶A,A的話音送給B、C、D三方用戶,A用戶聽到的是B用戶的聲音,其他用戶聽到的是A用戶的聲音。

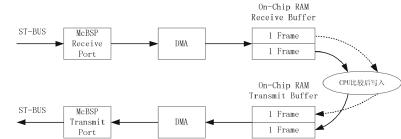

圖2 會議電話的DSP數據處理流程圖

首先DSP同時啟動McBSP的收發端口,當McBSP的接收端口收到ST-BUS鏈路送來的第M幀對應于某一用戶時隙的8 bit A律(或m律,下面以我國的A律編碼為例)PCM話音數據后,先將其轉成13 bit線性碼,然后在線性碼的右端補上3 bit的0送給接收寄存器DRR1,這是因為TMS320VC5410 是16位的,只能對片上RAM按16 bit訪問,為提高算法效率,設計中使用了線性碼進行話音幅度比較。線性碼轉換完成后McBSP通知分配給它的接收DMA控制器,此時,DRR1的數據已就緒,接收DMA控制器立即將此16 bit數據按照其對應的地址寫入接收緩沖區中。我們在DSP的片上RAM中給McBSP的接收和發送端口各分配了2幀的數據緩沖區。為方便軟件處理,配置DMA時,在分配給它的數據緩沖區達到半滿和全滿時,向DSP內的CPU發送中斷,因此DMA接收完第M幀話音數據后向CPU發送中斷。

當CPU收到DMA中斷時,表明DMA已經接收到了第M幀全部時隙的數據,CPU在第M+1幀的期間依據每一個會議電話中與會用戶所對應的時隙號,對存于接收數據緩沖區的用戶的第M幀話音數據取絕對值后進行幅度大小比較,找到最大的話音和第二大的話音,分別將它們寫入第M+2幀與會用戶對應的發送數據緩沖區的地址內。

在第M+2幀時發送DMA控制器從它的數據緩沖區內依次讀出相應的數據送給McBSP的發送端口,發送端口首先將此線性碼語音數據轉成A律語音數據,然后完成PCM話音數據發送。

DSP配置

TMS320VC5410有3個McBSP和6個DMA,可以全部用于會議電話的實現。可以將DMA0“2依次分給McBSP0”2的接收端口,DMA3“5依次分給McBSP0”2的發送端口。

片上RAM分配

TMS320VC5410具有8K字16-bit 片上雙訪問RAM (DARAM) 和56K字16-bit片上單訪問RAM (SARAM)。DARAM由4塊組成,每塊大小為2K字。每塊可以在同一個時鐘周期內讀兩次或者讀寫各一次,因此適合用于DSP與Host之間的消息緩沖區,故將數據空間的0080h-1FFFh映射為DARAM。SARAM由7塊組成,每塊大小為8K字。SARAM可以在同一個時鐘周期內讀一塊,寫另一塊,因此適合用于運行程序區和數據區,程序空間的2000h?FFFh映射為SARAM,數據空間的8000h蠪FFFh映射為SARAM。對于片上RAM的分配見圖3,具體分配如下所示:

圖3 片上RAM分配示意圖

1.0x0080“0x1FFF,DSP與Host的消息緩沖區。

2.0x2000”0x4FFF,DSP程序區,包括目標文件的.text和.cinit段。其中0x2000“0x2080為DSP的中斷向量表。

3.0x5000”0x7FFF,DSP數據區,包括DSP文件的.bss 和 .stack段。

4.0x8000“0x803F,DMA0緩沖區,用于McBSP0的接收。

5.0x8040”0x807F,DMA1 緩沖區,用于McBSP1的接收。

6.0x8080“0x80BF,DMA2 緩沖區,用于McBSP2的接收。

7.0x80C0”0x80FF,DMA3 緩沖區,用于McBSP0的發送。

8.0x8100“0x813F,DMA4 緩沖區,用于McBSP1的發送。

9.0x8140”0x817F,DMA5 緩沖區,用于McBSP2的發送。

McBSP的配置

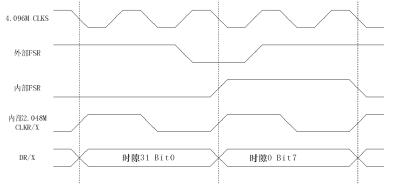

McBSP支持2M和8M ST-BUS鏈路,這里我們以4.096M輸入時鐘的2.048M ST-BUS鏈路為例,見圖4 ST-BUS鏈路示意圖。McBSP的配置主要涉及以下四個寄存器。

圖4 ST-BUS鏈路示意圖

1.引腳控制寄存器(PCR)

CLK(R/X)M = 1, 由內部采樣率發生器產生內部收發時鐘CLK(R/X);FS(R/X)P = 1,幀同步低有效。

2.接收/發送控制寄存器(RCR/XCR)

(RX)PHASE = 0,單相位幀;(R/X)FRLEN1 = 11111,每幀32 字;(R/X)WDLEN1 = 0,字寬度8-bit;(R/X)COMPAND = 11,接收/發送數據使用A律壓擴;(R/X)DATDLY = 0,無數據延遲。

3.采樣率發生寄存器(SRGR)

CLKGDV = 1,接收/發送時鐘CLK(R/X)的頻率是CLKS的1/2;

GSYNC = 1,外部接收幀同步FSR同步CLKG;CLKSP = 1,CLKS的

下降沿產生采樣率發生器的CLKG,進而產生CLK(R/X);CLKSM = 1,外部時鐘CLKS驅動采樣率發生器。

4.多通道控制寄存器(MCR1,2)

RMCM = 0,接收全部時隙使能。XMCM=00,發送全部時隙使能。

DMA的配置

DMA0“2依次分配給McBSP0”2的接收,DMA3“5依次分配給McBSP0”2的發送。具體配置如下描述:

1.DMA源地址寄存器(DMSRC)

接收DMA的DMSRC存放其對應的McBSP的DRR的地址;

發送DMA的DMSRC存放其對應的數據緩沖區的首地址。

2.DMA目的地址寄存器(DMDST)

接收DMA的DMDST存放其對應的數據緩沖區的首地址;

發送DMA的DMDST存放其對應的McBSP的DXR的地址。

3.DMA通道單元計數寄存器(DMCTR)

DMCTR的值設置了DMA數據緩沖區的大小,取為0x40,即兩數據幀所包含的用戶時隙數。

4.DMA 同步事件和幀計數寄存器(DMSFC)

DSYN[3:0]=0001,同步事件為McBSP0的接收事件REVT0;

DBLW = 0,單字模式,每一項是16 bit。

5.DMA傳輸模式控制寄存器(DMMCR)

AUTOINIT = 0,禁止自動初始化;DMA0的DINM = 1,IMOD = 1,DMA的緩沖區半滿和全滿時產生中斷;

DMA 1“5的DIMM=0,IMOD = X,不產生DMA中斷;

CTMOD = 1,DMA工作于ABU模式;

DMA0”2的SIND=000,接收DMA取為源地址不變;

DMA3“5的SIND=001,發送DMA取為源地址遞增;

DMS = 01,DMA源地址空間為數據空間;

DMA0”2的DIND=000,接收DMA取為目的地址遞增;

DMA3“5的DIND=001,發送DMA取為目的地址不變;

DMD = 01,DMA目的地址空間為數據空間。

性能計算

會議電話要求在每一幀所產生的DMA中斷服務程序中必須完成對所有會議的與會用戶的話音處理。我們以運算速度100MIPS的TMS320VC5410為例,該DSP一個指令周期的時間為10ns,因此在ST-BUS一幀125ms內可處理的指令數為125ms /10ns=12500條。由于所有用戶均參加同一個會議并且話音幅度按照時隙數遞增時DSP的運算處理量最大,因此我們按照上述條件來計算處理能力。假設一個會議發起時,可同時參加的用戶數為x,則有如下不等式:

26x+254≤12500

其中254為中斷服務程序的公共指令周期數,26為每個用戶對應的指令周期數。

由上式推算出x≤471,而三條McBSP鏈路可同時處理3×32=96個用戶(2M ST-BUS鏈路)或者3×128=384個用戶(8M ST-BUS鏈路),所以會議電話的最大用戶數最終由McBSP決定,即采用2M ST-BUS鏈路時支持96個用戶,采用8M ST-BUS鏈路時支持384個用戶。

使用匯編語言代碼效率高,程序執行速度快。上述算法DMA中斷服務程序是采用匯編語言來實現的,實踐證明該算法是高效的。

結語

本文介紹的基于TMS320VC5410的會議電話解決方案已成功地應用于CDMA系統MSC中,

網上實際運行充分驗證了該方案具有大容量和高性能價格比的特點。

責任編輯:gt

-

處理器

+關注

關注

68文章

19920瀏覽量

235667 -

dsp

+關注

關注

557文章

8161瀏覽量

358104 -

芯片

+關注

關注

460文章

52566瀏覽量

441848

發布評論請先 登錄

在TMS320VC5402處理器上怎么移植μC/OS-II操作系統?

TMS320VC5410 pdf datasheet

TMS320VC5410的McBSP串行接口技術與程序設計

TMS320VC5410-100,pdf(Fixed-Point DSP)

TMS320VC5410 DSP Silicon Errat

基于TMS320VC5410的實時信號處理系統的設計

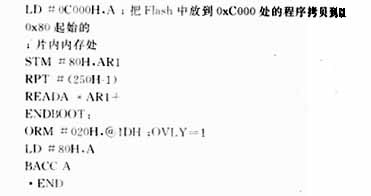

TMS320VC5410的BOOT設計與實現?

基于TMS320VC5410和SLE5542型IC卡的DES

TMS320VC5410芯片電源及復位電路設計

TMS320VC5410_Fixed-Point_Digital_Signal_Processor

TMS320VC5410A 數字信號處理器

評論