將DSP和單片機構成雙CPU處理器平臺,可以充分利用DSP對大容量數據和復雜算法的處理能力,以及單片機接口的控制能力。而DSP與單片機之間快速正確的通信是構建雙CPU處理器的關鍵問題。下面就此問題分別設計串行SCI、SPI和并行HPI三種連接方式。

1 串行通信設計與實現

1 1 SCI串行通信設計

1.1.1 多通道緩沖串行口MCBSP原理

TMS320VC5402(簡稱VC5402)提供了2個支持高速、全雙工、帶緩沖、多種數據格式等優點的多通道緩沖串行口McBSP。MCESP分為數據通路和控制通路。①數據通路負責完成數據的收發。CPU或DMAC能夠向數據發送寄存器DXR寫入數據,DXR中的數據通過發送移位寄存器XSR輸出到DX引腳。DR引腳接收數據到接收移位寄存器RSR,再復制到接收緩沖寄存器RBR,最后復制到數據接收寄存器DRR。這兩種數據多級緩沖方式使得數據搬移和片外數據通信能夠同時進行。②控制通路負責內部時鐘產生,幀同步信號產生,信號控制和多通道選擇。另外.還具有向CPU發送中斷信號和向DMAC發送同步事件的功能。MCBSP時鐘和幀同步信號通過CLKR、CLKX、FXR、FSX引腳進行控制,接收器和發送器可以相互獨立地選擇外部時鐘和幀同步信號,也可以選擇由內部采樣率發生器產生時鐘和幀同步信號。幀同步脈沖有效表示傳輸的開始。

1.1.2 SCI串行接口設計

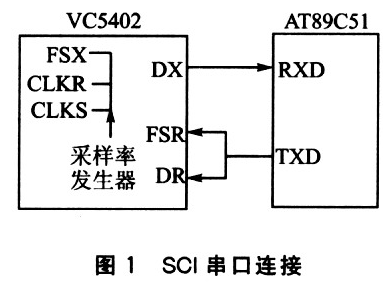

設置VC5402的McRSP輸出時鐘和幀同步信號由內部采樣率發生器產生,內部數據時鐘CLKG和幀同步信號FSG驅動發送時鐘CLKX和幀同步FSX(CLKXM=l,FSXM=l,FSGM=1),輸入時鐘也由內部采樣率發生器產生,內部數據時鐘CLKG驅動接收時鐘CLKR(CLKRM=1),同時由CPU時鐘驅動采樣率發生器(CLKSM=1)。考慮到AT89C51(簡稱C51)串口發送數據幀中第l位為起始位,因此可以利用該位驅動輸入幀同步信號FSR,同時要置忽略幀同步信號標志為1。其中FSG幀同步脈沖寬度=(FWID+1)·CLKG;FSG幀同步脈沖周期=(FPER+1)·CLKG;采樣率發生器分頻系數(采樣率=波特率)=FIN/(CLKGDV+1)。

SCI串口連接如圖1所示。

1.1.3 波特率不一致的處理

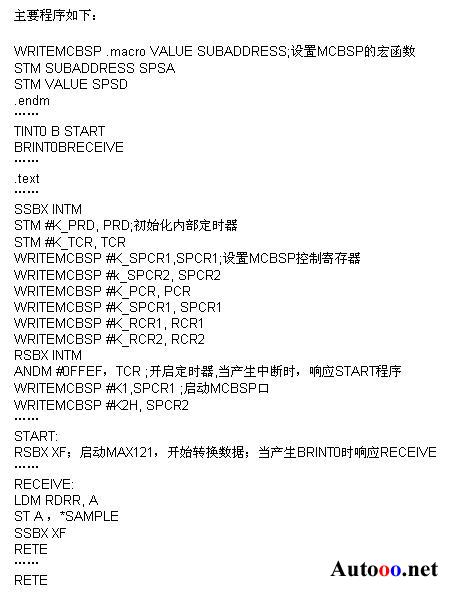

VC5402初始化(以圖1為例):

STM#SRGRl,SPSAl

STM#ooFEH,SPSDl;FSG幀同步脈沖寬度位為1個CLKG

;波特率為100 MHz/(0X(OFF)=392 156 b/s

STM#SRGR2,SPSAl

STM#3D00H,SPSDl;內部采樣率發生器時鐘由CPU驅動

C51初始化:

MOV TMOD,#20H

MOVTLl,#FFH

MOVTHl,#FFH ;C51波特率=(2SMOD/32)*(fosc/12)[1/(256一初值)]一24 509 b/s

MOV SCON,#50H ;置串口方式l,每一幀10位數據.允許接收

MOV PCON,#80H ;設置SMOD=1

VC5402波特率/C51波特率=(392 156/24 509)=16.000 49

VC5402每發送16位數據,C51只采樣1位數據。在VC5402存儲器中開辟一個空間對每次發送的8位數據進行擴展,1位擴為16位,0為0000H,l為FFFFH,共擴為128位。在數據頭部填加16位起始位0000H,數據尾部填加停止位FFFFH。在VC5402發送控制寄存器XCR中設置XWDLEN=000(1字含8位),即可將要發送的8位數據封裝成1幀10字的數據。這也符合C51串口1方式下1幀10位的數據格式。C51以1/16的VC5402采樣速率接收數據,0000H采樣為0,FFFFH采樣為1,由此可以將接收到的200位恢復為8位數據,停止位進入RB8。

C51每發送1位數據,VC5402要采樣為16位數據。C51一次發送的10位數據的起始位觸發VC5402的接收幀同步。由于VC5402以16倍C51的采樣速率接收數據,1位采樣為16位,0采樣為0000H,1采樣為FFFFH.只采樣發送來的10位中的前9位,9位封裝成144位,即接收的1幀數據完成。VC5402將收到的144位數據在開辟的存儲器空間存放,拋棄前16位,在剩下的128位里分成8組,每組16位。比較其中間的8位,若有4位以上為1,則該16位為1,反之則為0。由此將接收到的144位恢復為8位數據。

為了不讓CPU頻繁地被數據接收和發送打斷,將DMA和MCBSP聯合使用來控制數據的接收和發送。RRDY直接驅動MCBSP向DMAC接收數據事件(REVENT事件),XRDY直接驅動MCBSP向DMAC發送數據事件(XEVENT事件)。

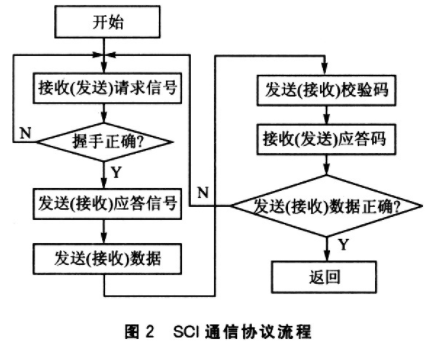

SCI通信協議如圖2所示

1. 2 SPI串行通信設計

將C51置為主機,VC5402為從機。McBSP的時鐘停止模式(CLKSTP=1X)兼容SPI模式,接收部分和發送部分內部同步。McBSP可以作為SPI的從機或主機。發送時鐘BCLKX作為SPI協議的移位時鐘SCK使用,發送幀同步信號BFSX作為從機使能信號nSS使用,接收時鐘BCLKR和接收幀同步信號BFSR不使用。它們在內部分別與BCLKX和BFSX直接連接。BDX作為MISO,而BDR作為MOSI,發送和接收具有相同字長。

C51中的并口P1.1和P1.2作為擴展串行SPI輸人輸出口與VC5402連接,P1.0作為串行時鐘輸出口,P1.3作為幀同步信號輸出口。

SPI串口連接如圖3所示。

VC5402初始化程序(以圖3為例):

STM#SPCRll,SPSAl;設置時鐘停止位進入MCBSP的SPI模式

STM#0X1000,SPSDl;時鐘開始于上升沿(無延遲)

STM#SPCRl2,SPSAl

STM#0X0040,SPSDl;XINT由XRDY(即字尾)驅動

STM#PCRl,SPSAl

STM#0X000C,SPSDl;對發送和接收時鐘,同步幀進行設置

STM#RCRll.SPSAl

STM#0X0000,SPSDl;接收數據l幀1字.1字8位

STM#XCRll,SPSAl

STM#0X0000,SPSDl;;發送數據1幀1字.1字8位;

P1.0發送到VC5402的移位時鐘是保證DSP正確采樣接收和發送數據的時鐘。它要保證和C51的采樣接收和發送數據的時鐘一致.才能使主從機同步。

2 并行通信設計與實現

2.1 VC5402的HPI接口原理

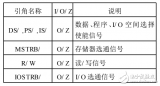

HPI一8是一個8位(HD0~HD7)的連接DSP與主機設備或主處理器的并行接口。DSP與主機通過DSP的片內RAM交換數據,整個片內RAM都可以作為HPI一8的存儲器。HPIA地址寄存器只能由主機直接訪問,存放當前尋址的存儲器的地址;HPID數據鎖存器只能由主機直接訪問,存放當前要寫入或讀出的數據;HPIC控制寄存器可以被主機和VC5402共同訪問。HPI本身的硬件中斷邏輯可以完成主從設備之間的握手,主機通過置HPIC中的特定位產生DSP中斷,同樣DSP通過nHINT引腳對主機產生中斷。HRDY引腳用于自動調節主機訪問HPI的速度,使慢速外部主機與DSP能很好地匹配。HRDY由HCS使能,即當HCS為高時HRDY一直為高,而當EMUl/nOFF為低時,HDRY輸出高阻。

HPI連接如圖4所示。

2.2 并行接口設計

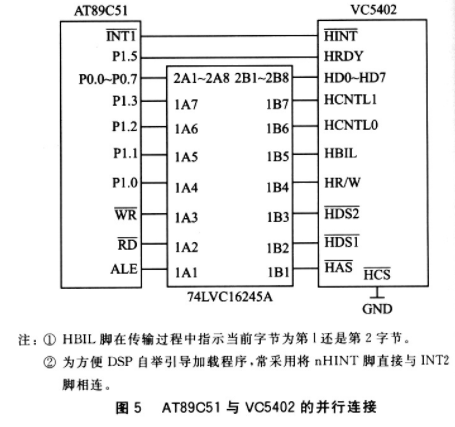

將C51置為主機,VC5402置為從機。C51的PO口和HPI的8位數據線HD0~HD7相連作為數據傳輸通道,P1.0~P1.3設置為輸出控制HPI口的操作。其中P1.0作為讀寫控制選通信號連接HR/W;P1.1連接字節識別信號HBIL,控制讀寫數據是屬于16位字的第1還是第2字節;P1.2和P1.3分別連接HCNTL0和HCNTLl,以實現對HPIC、HPIA和HPID寄存器的訪問;nRD和nWR連接nHDSl和nHDS2作為數據選通信號來鎖存有效的HCNTLO/1、HBIL和HR/W信號。nINTl作為輸入,與HPI口的主機中斷信號nHINT相連。nHCS一直接地,而nHAS口和ALE口相連接,在HCNTL0/I、HBIL和HR/W信號有效之后,設置nHDSl為低電平,則實現了讀寫的數據選通,從而完成C51對VC5402 HPI口的讀寫操作。在數據交換過程中,C51向HPI發送數據時,通過置VC5402的HPI控制寄存器HPIC中的DSPINT位為l來中斷VC5402。C51接收來自HPI的數據時通過查詢方式,當VC5402 DSP準備發送數據時,置nHINT信號為低;C51查詢到nlNTl為低時,調用接收數據子程序來實現數據的接收。

C51與VC5402的并行連接如圖5所示。

主機接收和發送初始化程序(以圖5連接為例):

RTITEADDRESS: ;寫入VC5402存儲器地址信息

CLR P1.2

注:①HBlL腳在傳輸過程中指示當前字節為第l還是第2字節。

②為方便DSP自舉引導加載程序.常采用將nHlNT腳直接與INT2

腳相連。

圖5 AT89C51與V05402的并行連接

SETB P1.3 ;主機可讀寫HPlA地址寄存器

CLR P1.0 ;主機要求寫選通HPI一8

MOV P0,A ;寫入8位地址

CALL DELAY ;等待地址寫入完成

READDATA: ;讀出VC5402存儲器數據信息

SETB P1.2

CLR P1.3 ;主機可讀寫HPID數據寄存器

SET P1.0 ;主機要求讀選通HPI一8

MOVA,P0 ;讀出8位數據

CALL DELAY ;等待數據讀出完成

WRITEDATA: ;寫入VC5402存儲器數據信息

SETB Pl.2

CLR P1.3 ;主機可讀寫HPID數據寄存器

CLR P1.0 ;主機要求寫選通HPI一8

MOV P0,A ;寫入8位數據

CALL DELAY ;等待數據寫入完成

不管是串行連接還是并行連接,都要考慮到VC5402是采用3.3 V供電,C51采用5 V供電。兩者之間存在信號電平的差異而不能直接相連,應互連接口隔離器件。

結 語

在SCI串行通信調試中,發現由于DSP的運行頻率在100 MHz左右,造成內部數據時鐘CLKG過快,不能與C51串口采樣頻率保持一致,需要軟件加以處理,這樣會額外消耗DSP資源。因此可以考慮將發送時鐘CLKX和接收時鐘CLKR接外部時鐘源(慢于DSP時鐘),以保證與C51串口采樣頻率的一致。另外在并行通信的調試中,可以知道通過HPI-8口并行通信完全沒有硬件和軟件開銷,由DSP自身的硬件來協調沖突,因此HPI-8口使用于與單片機構件較好的主從雙CPU處理器平臺。

責任編輯:gt

-

處理器

+關注

關注

68文章

19259瀏覽量

229652 -

dsp

+關注

關注

553文章

7987瀏覽量

348745 -

單片機

+關注

關注

6035文章

44554瀏覽量

634640

發布評論請先 登錄

相關推薦

TMS320VC5402 DSP與單片機的HPI接口實現

HPI方式自舉在TMS320VC5402 DSP芯片上的實現

在TMS320VC5402處理器上怎么移植μC/OS-II操作系統?

怎樣去設計TMS320VC5402與模擬芯片TLC320AD50C的接口?

AVR 和TMS320VC5402的HPI接口通信設計

MAX121與TMS320VC5402在高速數據采集中的接口

基于DSP芯片TMS320VC5402的HPI通信設計

TMS320VC5402與51單片機的接口設計

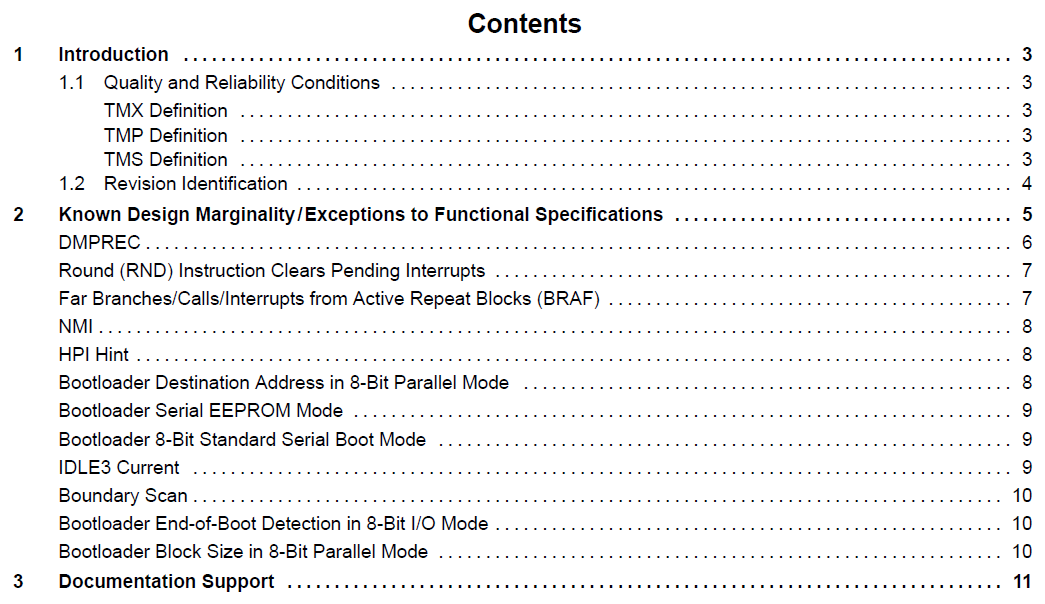

TMS320VC5402和TMS320UC5402引導加載程序的特點和操作詳細概述

TMS320UC5402和TMS320VC5402數字信號處理器硅勘誤表詳細分析概述

TMS320VC5402 數字信號處理器

基于TMS320VC5402和單片機實現主從雙CPU處理器平臺的設計

基于TMS320VC5402和單片機實現主從雙CPU處理器平臺的設計

評論