作者:仲智剛,馮根寶,郁正慶

下一代網絡(NGN- Next Generation Network)是以IP為核心,可以同時支持語音、數據和多媒體業務的融合網絡,是通信網絡的發展方向。傳統的以電路交換為核心的設備正逐漸被以IP為核心的網絡設備所替代。在這種演變過程中,設計一種能夠提供PSTN與NGN無縫連接的網關設備,從而實現以較低的成本向NGN網絡平滑過渡是目前各通訊設備制造商的重要研究課題。本文重點介紹了網關接口設備中核心器件,即NGN網關接口芯片的設計方法以及在Xilinx的Spartan3 XCS1000中的實現。

方案介紹

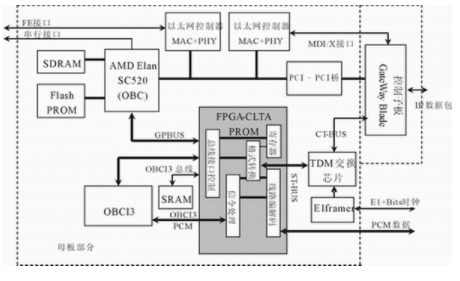

在本方案中,網關接口設備的主要功能是由網關接口板IP_GATEWAY所實現,包括母板與子板兩部分,其中母板部分主要完成傳統的語音和數據部分的格式轉換以及信令處理,子板主要完成與媒體網關控制器MGC(Media Gateway Controller)的通信與控制功能,如H.248/Megaco 協議的處理、連接的建立與釋放等。其基本結構如圖1所示,母板部分主要包括CPU-AMD Elan520,專用處理芯片OBCI3、以太網接口芯片、FPGA控制芯片、PCI橋、交換芯片TDM、板上RAM/ROM,以及時鐘、電源等模塊;子板部分(Gateway Blade)主要包括CPU-BCM1122,以太網交換芯片以及兩個DSP。限于篇幅,不做過多介紹。

如圖1所示,FPGA控制芯片(CLTA)處于整個母板的核心地位,其主要功能包括:語音和數據格式轉換,即將來自終端控制板的PCM格式語音和數據轉化為適用于TDM芯片的ST_BUS總線格式; AMD-Elan520的CPU讀寫邏輯映射以及SRAM存取,DMA模式控制;OBCI3接口控制;線路端編解碼功能。

圖1 網關接口板功能結構圖

設計描述

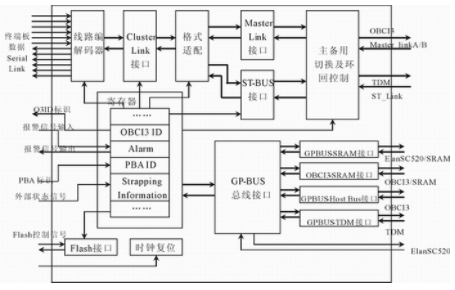

FPGA的主要功能模塊如圖2所示。處于框圖上端的部分主要是數據流處理部分,主要完成數據格式轉換以及信令提取和傳遞功能,同時還包括線路端的編解碼功能;右邊主要是控制部分,完成CPU對FPGA、OBCI3芯片以及片外SRAM的存取和控制功能;左下部分主要是FPGA寄存器模塊以及如Flash保護,系統報警處理等輔助模塊。

圖2 FPGA內部功能結構圖

數據流

從數據流角度看,FPGA包括與專用處理芯片OBCI3 相連的MasterLink[A,B],與終端控制板相連的Serial Link,與TDM芯片相連的ST_Link。為提高網關接口設備的可靠性,所有的數據流都包括A、B兩路,分別來自主/備用設備,當其中一路發生故障時,系統自動切換到另外一路。以上行數據為例,從終端控制板來的Serial Link共分6路,其中每一路數據格式都是由A、B兩路經過Manchester編碼過的復用數據,A/B路復用數據在Coder/Decoder模塊中經過線路端解碼,恢復出A 、B兩路Cluster Link數據,該數據采用PCM格式,其速率為4MHz,共分為32 個PCM 信道,每個信道16位,其中CH0 用于同步信道,CH16 用于信令信道,其它信道可以承載語音和數據,又叫SPATA 信道。16位的SPATA 信道包含了8位的語音編碼和協議位,CH0包含同步編碼,如表1所示:其中PP 是協議比特,當有告警時PP=11,否則為00,A=1時表明存在軟件或硬件告警,M=1 時表明存在摘掛機事件。其中,13 、12以及7 “4為同步位,當上下游接口芯片以每125ms的間隔固定檢測到同步碼的時候,整個系統處于完全同步狀態,否則,對端芯片會在CH16發出遠端告警,用于通知網關設備進行故障處理。

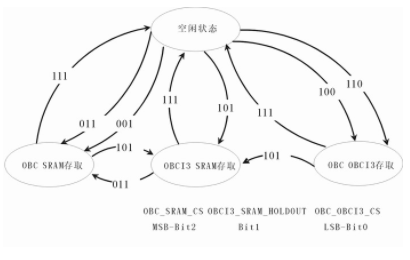

圖3 控制狀態機

CH16 是16位寬的控制信道,用于發送控制命令包或接收反饋包,用于控制終端控制板的操作。MasterLink 只承載同步和信令信道,不包括SPATA 信道,MasterLink 也包含A B兩條鏈路。ST_Link是與TDM芯片相連的TDM 鏈路,滿足標準ST-BUS 的接口要求,只承載8位的語音信道。FPGA將前述Serial Link經過Manchester解碼后分離的A/B路數據分別進行8位數據提取,然后按照ST_BUS總線的格式分別放到各自對應的通道中,共12路ST_link數據。具體實現上,采用2個雙口RAM,進行數據緩存后,按照ST_BUS格式按序讀出。反之,FPGA進行ST_BUS到Serial Link的擴展。

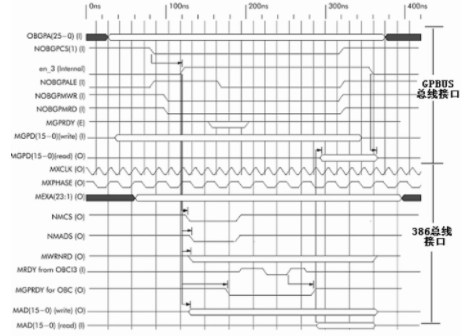

圖4 GPBUS與386總線映射關系

由于CH0中包含報警以及摘掛機信息,因此,6路Serial Link中的CH0被按位或運算后發送給OBCI3,由OBCI3進行相應的檢測和處理。反方向則將MasterLink 中來自OBCI3的CH0 廣播到同組各個Serial link中的CH0,以提供同步功能。另一方面,MasterLink 上的兩個CH16 用于控制遠端終端控制板,CPU產生的控制信令通過OBCI3芯片,傳送到MasterLink的CH16 信道上,并由FPGA廣播到相應Serial Link 的CH16 中,相反方向,Serial Link的CH16信道中來自遠端終端控制板的反饋響應,通過FPGA轉發到MasterLink 的CH16 中,由OBCI3 接收,交給CPU處理。因此,最終ST_BUS上只包含SPATA的負荷,MasterLink只包含信令消息。通過TDM芯片,ST_BUS上的SPATA 信道進行一級交換后進入子板進行語音壓縮、IP成包等后續處理。

控制流

如圖1所示,母板上采用了AMD公司的Elan520,由于該CPU采用的是專用的GP_BUS總線協議,與片外SRAM通訊需做一定處理。另外,OBCI3是我們自行設計的專用處理芯片,其CPU總線接口采用Intel-386總線協議格式,因此,FPGA必須提供兩組總線讀寫操作之間的邏輯映射。同時,OBCI3本身支持DMA模式存取SRAM,因此,FPGA還必須提供DMA接口的控制功能。

圖3是在FPGA具體實現中所采用的狀態機,系統共有4個狀態,狀態翻轉的信號見圖3右下側,低為有效。當CPU沒有總線操作時,系統為空閑狀態;當CPU需要進行SRAM操作時,SRAM片選信號有效,系統進入OBC SRAM 存取狀態,在此狀態下,FPGA將CPU的操作映射為標準的SRAM時序,從而完成SRAM的讀寫操作。FPGA同時監測OBCI3的DMA請求信號,當狀態為OBCI3 SRAM 存取時,如果CPU授權DMA請求,FPGA則激活OBCI3的HOLD_OUT信號,使OBCI3獲得系統總線控制權,并啟動DMA模式直接存取片外SRAM,從而大大加快了系統處理的速度。當CPU需要與OBCI3進行通訊的時候,系統進入OBCI3 存取狀態,在該狀態下,FPGA將異步的GPBUS總線邏輯的讀寫操作映射為同步的Intel-386接口時序,見圖4。圖中上半部分是GPBUS的讀寫時序,而下半部分則是經過FPGA映射后輸出的標準386 CPU接口時序。圖中箭頭標明了兩組總線控制信號之間的時序關系。

設計實現

本設計采用Xilinx的Spartan3-XCS1000實現。Spartan3系列器件采用90nm工藝,具有豐富的內部資源,包括17280個邏輯單元,120Kbit的分布式RAM和432Kbit的Block RAM,并提供了豐富的引腳接口類型。設計利用Synplify Pro 7.7進行綜合,在ISE8.1中完成布局布線。經過系統驗證,完全符合系統要求,現在已經進行批量生產。

結語

為順利向下一代網絡結構過渡,本文設計了NGN網關設備中的接口芯片,該芯片能夠提供設備所需要的多種邏輯功能,極大地簡化了電路板的設計。同時,設計本身采用可擴展的設計結構,可以滿足系統擴展的要求。采用Spartan3系列FPGA實現,經過系統測試,完全符合設計需求。

責任編輯:gt

-

FPGA

+關注

關注

1629文章

21729瀏覽量

603012 -

芯片

+關注

關注

455文章

50714瀏覽量

423158 -

接口

+關注

關注

33文章

8575瀏覽量

151023

發布評論請先 登錄

相關推薦

spartan3 xc3s400 bit文件轉mcs

NGN協議發展現狀和業務接口的成熟狀況

測量spartan3靜態功耗

iMPACT如何檢測斯巴達設備?

Isthis Flash與Xilinx Spartan3 FPGA兼容嗎?

是否有適用于SPARTAN3的VIVADO附加軟件包?

Cyclone與Spartan-3對比

QDR SRAM與Spartan3 FPGA的接口設計

基于Spartan3 XCS1000實現NGN網關接口芯片的設計

基于Spartan3 XCS1000實現NGN網關接口芯片的設計

評論